I always wanted to know more ... read

introduction

2 7 Y E A R S O F I B M R I S C

1965 IBM ACS

In the 1960's IBM was behind in the scientific area and

wanted to design an advanced machine better than the CDC 6800, later called the

CDC 7600.

The idea for the ACS (IBM Advanced Computing Systems) design started in 1965 with John Cocke's vision of a scientific

supercomputer. This was several years earlier than the RISC work at Berkeley and

Stanford Universities. The ACS project (which evolved from "Project Y", that

started late 1963) was cancelled in 1968.

Many of the innovative CPU organization techniques pioneered in ACS were used in the IBM

RS/6000.

After ACS, John Cocke carried this understanding of compilers and instruction sets

with him to the IBM 801 project. John also greatly influenced the IBM Cheetah and

America projects, which were the predecessors to the RS/6000.

Links:

A

Secret 1960's Supercomputer Project

IBM’s ACS-1 Machine

Technical Description of IBM ACS Project |

|

|

The

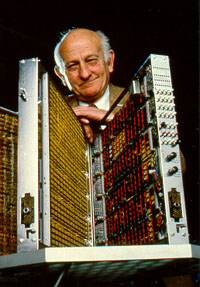

A.M. Turing Award

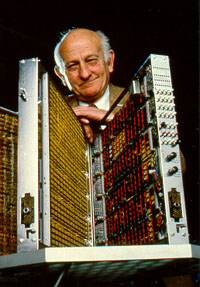

1987: John Cocke for significant

contributions in the design and theory of compilers, the architecture of

large systems and the development of reduced instruction set computers

(RISC); for discovering and systematizing many fundamental transformations

now used in optimizing compilers including reduction of operator strength,

elimination of common subexpressions, register allocation, constant

propagation, and dead code elimination. |

|

1974 the 801

IBM Reduced Instruction Set Computer

(RISC) technology

originated in 1974 in a project at the Thomas J. Watson Research Center to

design a large telephone-switching network. The computer needed was named the

801 (after Building 801, where the research was taking place).

The goal of the 801 was to execute one instruction per cycle. The experimental

801 was never build, but

the design, mostly developed by IBM researcher John Cocke, seemed to be an good

basis for a general-purpose, high-performance miniprocessor.

Links:

The

evolution of RISC technology at IBM (PDF)

1985 America

Based on the experimental design of the

801 and ACS ideas the

development laboratory in Austin completed a first prototype, where it

evolved into the superscalar (Instructions are handled paralel) RISC System/6000 (RS/6000) processor that was introduced into the market in

1990. Development work had been done under code name

"America" for the RISC chip research, and "RIOS" for systems

using the America technology.

1986 RT PC

The IBM RT PC is IBM's first RISC based UNIX

(Advanced Interactive Executive [AIX] V1) computer with 32 bits ROMP processor (without

floating point capability ...) that was first announced by IBM in January

1986. The IBM RT has had a varied life from its initial announcement. The RT was

considered as "not enough power, too high a price,

and too late" and thought to be part of IBM's Personal Computer

line ... (hence RT PC, later renamed to RT).

The IBM RT PC is IBM's first RISC based UNIX

(Advanced Interactive Executive [AIX] V1) computer with 32 bits ROMP processor (without

floating point capability ...) that was first announced by IBM in January

1986. The IBM RT has had a varied life from its initial announcement. The RT was

considered as "not enough power, too high a price,

and too late" and thought to be part of IBM's Personal Computer

line ... (hence RT PC, later renamed to RT).

Links:

6150 RT PC Models 020, 025, and A25 IBM 6151 RT PC model 010

RT PC FAQ

1986 Advanced Interactive Executive

AIX for the RT PC is announced.

The RT used the Virtual Resource Manager (VRM) that provided a virtual machine environment for

the kernel, allowing more than one operating system to execute.

Links:

RT PC AIX and Virtual Resource Manager

RT PC AIX Version 2.1

1987 AIX (PS/2)

IBM will provide the PS/2 AIX Operating

System as a subset of the multiuser, multitasking, virtual memory AIX operating

system currently available on the IBM RT PC.

Links:

PS/2 AIX Statement of Direction

Availability

of PS/2 AIX delayed ...

1990 POWER

Februari 1990 IBM announces its new RISC-based computer line, the

RISC System/6000 (later named RS/6000, nowadays eServer pSeries), running AIX

Version 3. The architecture of the systems is given the name POWER (now commonly referred to as

POWER1), standing for Performance Optimization With Enhanced RISC. They where based on a multiple chip implementation of

the 32-bit POWER architecture. The models introduced included an 8 KB instruction cache

(I-cache) and either a 32 KB or 64 KB data cache (D-cache). They had a single

floating-point unit capable of issuing one compound floating-point multiply-add

(FMA) operation each cycle, with a latency of only two cycles and optimized 3-D graphics

capabilities.

The model 7013-540

(30 MHz) processed 30 million instructions per

second.

Its electronic logic circuitry had up to 800,000 transistors per silicon chip.

The maximum memory

size was 256 Mbytes and its internal disk storage capacity was 2.5 GBytes.

Links:

RISC

System/6000 POWERstations/POWERservers 520 AND 530

RISC System/6000 POWERserver 540

RISC System/6000 POWERstation 730

RISC System/6000 POWERserver 930

AIX Version 3

AIX Version 3 is announced.

Links:

AIX Version 3 (Februari, 1990)

Overview: IBM RISC System/6000 and related announcements

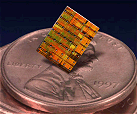

1992 RSC

In January of 1992, the model 7011-220

(33 MHz)  ,

an entry-level desktop workstation, was announced, based on a single chip

implementation of the POWER architecture, usually referred to as RISC Single

Chip (RSC). I recall we used to say "the pizza box".

,

an entry-level desktop workstation, was announced, based on a single chip

implementation of the POWER architecture, usually referred to as RISC Single

Chip (RSC). I recall we used to say "the pizza box".

Links:

RISC

System/6000 POWERstation/POWERserver 220, 22W AND 22G

1993 SP

The IBM Scalable POWERparallel Systems (SP,

now commonly referred to as SP1)

offer a scalable platform for both serial and parallel applications. Based on

RISC System/6000 technology, the basic component of the in Februari 1993

announced 9076

SP1 is a system frame containing eight to 16 RISC System/6000 processor

nodes (max. four frames, 64 nodes).

The IBM Scalable POWERparallel Systems (SP,

now commonly referred to as SP1)

offer a scalable platform for both serial and parallel applications. Based on

RISC System/6000 technology, the basic component of the in Februari 1993

announced 9076

SP1 is a system frame containing eight to 16 RISC System/6000 processor

nodes (max. four frames, 64 nodes).

The SP implements Massively Parallel Processing (MPP). All the processing nodes

have their own resources (processors, memory, disks and operating system): the

shared nothing architecture.

Links:

AIX

Parallel Environment

SP models 001, 002, 003, 004, A01, AND 101

More

SP models

2001 SP

Overview

PowerPC 601

The RISC System/6000 model 7011-250 (66 MHz) workstation, the first to be based on the

32-bit PowerPC 601

processor, was introduced in September 1993.

The 601 was the

first processor arising out of a partnership between IBM, Motorola, and Apple.

From IBM, the RISC Single Chip (RSC) microprocessor became the base design for

601. The superscalar machine organization of the 601 was improved to achieve greater

performance and additional custom circuit design was applied to reduce the die size

and to allow higher frequency operation. The Motorola 88110 microprocessor bus

interface formed the basis of the development of the 601 bus interface.

The 601 did not implement

the full PowerPC instruction set (some infrequently used instruction where

excluded) and some new instructions and features were added, such as support

for symmetric multiprocessor (SMP) systems. The 601 is capable of dispatching,

executing, and completing up to 3 instructions per cycle. Instructions issue to multiple execution

units (an integer unit, a

branch processing unit, and a floating-point unit), execute in parallel, and can complete out of

order.

An SMP has multiple processors that have their own cache, the memory and devices

are shared.

The 601 was a bridge from POWER to the full

PowerPC architecture, such as the 603,

604, and 604e.

Links:

POWERstation/POWERserver 250 Series

PowerPC 601 Microprocessor

PowerPC Architecture

POWER2

The model 7013-590

(66 MHz) was announced in September 1993 and was the first RS/6000 based on the

32-bit POWER2

architecture. The

most significant improvement introduced with the POWER2 architecture for

scientific and technical applications is that the floating-point unit (FPU)

contains two 64-bit execution units, so that two floating-point multiply-add

instructions may be executed each cycle. A second fixed-point execution unit is

also provided. In addition, several new hardware instructions were introduced

with POWER2: quad-word storage instructions, hardware square root instruction

and floating-point to integer conversion instructions.

The model 7013-590

(66 MHz) was announced in September 1993 and was the first RS/6000 based on the

32-bit POWER2

architecture. The

most significant improvement introduced with the POWER2 architecture for

scientific and technical applications is that the floating-point unit (FPU)

contains two 64-bit execution units, so that two floating-point multiply-add

instructions may be executed each cycle. A second fixed-point execution unit is

also provided. In addition, several new hardware instructions were introduced

with POWER2: quad-word storage instructions, hardware square root instruction

and floating-point to integer conversion instructions.

Initial models: 7013-58H (55 MHz),

7013-590 (66 MHz),

7015-990 (71.5 MHz).

Links:

POWER2: Next Generation of the RS/6000 Family

PowerPC

and POWER2: Technical Aspects of the New IBM RS/6000

POWER2

Architecture Implementations

POWER2

and PowerPC architecture

Migration and Compatibility

1994

Notebook

1994

Notebook

The RS/6000 7007-N40 (50 MHz) notebook workstation

(introduced in March) is the ideal portable companion for mobile professionals

who want to take AIX on the road. Based on the PowerPC 601.

Links:

7007-N40

IBM RS/6000 Model N40

SP2

The Scalable POWERparallel Systems 2 (SP2) was announced in April 1994. Based on IBM's

RISC System/6000 microprocessor technology and running AIX/6000 (as it was named

then), the SP2 could scale from

two to 128 nodes (processing elements). Using a POWER2 processor and other

options it performed twice

the processing power of the SP1 system.

Links:

Scalable

POWERparallel Systems 9076 SP2 and Enhancements for SP1

Scalable Parallel Computing

9076-xxx SP Family

AIX Version 4.1

AIX Version 4.1 is announced.

Links:

AIX

Version 4.1 (July, 1994)

AIX

Version 4 Overview and Product Life Cycle Dates

AIX Version 4.2 Overview and Product Life Cycle Dates

AIX Version 4.3 Overview and Product Life Cycle Dates

1995 PowerPC 604

32-bit PowerPC

604 RISC System/6000 microprocessor (120

MHz) upgrade announced for the RISC System/6000 model 7020-40P

(66 MHz).

Links:

Motorola/IBM

PowerPC 604/604e

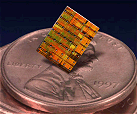

1996 POWER2 Super Chip

1996 POWER2 Super Chip

October 1996 the

RS/6000 model 7013-595

(135 MHz) was announced with the new 32-bit POWER2 Super Chip (also known as P2SC). The P2SC is a single chip

implementation of the POWER2 architecture, containing 15 million transistors on a single chip. It powers the wide and thin

nodes in SP systems.

Links:

SP

POWER2 Super Chip Nodes

RS/6000

In October (?) IBM renames RISC System/6000:

RS/6000.

PowerPC 603e

October 1996, announcement of the

portable workstation RS/6000

model 860 (166 MHz) - notebook - using the 32-bit PowerPC 603e processor.

PowerPC 604e

The

43P

models 140 and 240 with 32-bit

PowerPC

604e RS/6000 microprocessor (166 MHz)

are announced. The 604e is a superscalar processor capable of issuing four

instructions simultaneously. As many as seven instructions can finish execution

in parallel.

The

43P

models 140 and 240 with 32-bit

PowerPC

604e RS/6000 microprocessor (166 MHz)

are announced. The 604e is a superscalar processor capable of issuing four

instructions simultaneously. As many as seven instructions can finish execution

in parallel.

Links:

PowerPC

604e Overview

PowerPC

604e Technical Library

1997 RS64

The RS64 (also known as Apache) is the

first 64-bit PowerPC RISC processor (October

1997).

The RS64 is a superscalar processor optimized for commercial workloads. The processor has separate 64 KB L1 cache for instructions and

data and L2 cache controllers. The L2 caches run at full processor speed.

The RS64 contains a 16 byte interface to 2-way set associative 4MB L2 cache. The

RS64 is also used in the AS/400 (called A35). Predecessors of the A35, only

running OS/400 are the A10 (a.k.a. Cobra), the world's first 64-bit PowerPC

microprocessor, and A25 (a.k.a. Muskie).

The RS64 (also known as Apache) is the

first 64-bit PowerPC RISC processor (October

1997).

The RS64 is a superscalar processor optimized for commercial workloads. The processor has separate 64 KB L1 cache for instructions and

data and L2 cache controllers. The L2 caches run at full processor speed.

The RS64 contains a 16 byte interface to 2-way set associative 4MB L2 cache. The

RS64 is also used in the AS/400 (called A35). Predecessors of the A35, only

running OS/400 are the A10 (a.k.a. Cobra), the world's first 64-bit PowerPC

microprocessor, and A25 (a.k.a. Muskie).

IBM brings 64-bit technology to the market introducing the RS/6000 Enterprise

Server model 7017-S70

(125 MHz, code named Raven), the first 12-way SMP system, and AIX Version 4.3.

Links:

The 64-bit solution

RS/6000

Enterprise Server Model S70 Blazes the 64-Bit Trail

AIX Version 4.3

AIX Version 4.3 is announced. 32-bit/64-bit

application coexistence and concurrent execution. The kernel is still 32 bits.

Links:

AIX

Version 4.3 (October 1997)

AIX

Version 4.3.1 (April 1998)

AIX

Version 4.3.2 (October 1998)

1998 RS64 II

PowerPC RS64 II 64-bit RISC microprocessor (also know as NorthStar) is the first

in the Star series processor family.

The in July 1998 announced RS64-II contains a dedicated 32 byte interface to a private 4-way set

associative 8MB L2 cache. The processor target operating frequency is 262 MHz.

The 262 MHz cards contain four processors per card. Up to three 4-way cards can

be installed in a RS/6000 7017-S70

to create a 4-way, 8-way, or 12-way system.

Links:

The

RS/6000 Enterprise Server Model S70

4th

Generation 64-bit PowerPC-Compatible Commercial Processor Design

New Processors Enhance the IBM RS/6000 Model S70 Performance

POWER3

The new 64-bit POWER3 processor, announced October 1998, unifies the POWER2 architecture (P2SC) with the PowerPC architecture.

The new 64-bit POWER3 processor, announced October 1998, unifies the POWER2 architecture (P2SC) with the PowerPC architecture.

The SMP-capable POWER3 design

allows for concurrent operation of fixed-point instructions, load/store

instructions, branch instructions, and floating-point instructions. The POWER3

is capable of executing up to four floating-point operations per cycle (two

multiply-add instructions). Integer performance has been significantly enhanced over the

P2SC with the addition of dedicated integer and load/store execution units. The chip

features eight execution units fed by a 6.4 gigabyte-per-second memory

subsystem. The core includes two high-bandwidth buses: a 128-bit 6XX

architecture bus to main memory and 256-bit bus to the L2 cache that runs at

processor speed. The POWER3 also has on-chip 64KB data cache and a 32KB

instruction cache.

IBM's first 64-bit symmetric

multiprocessor (SMP) workstation is the POWER3 based RS/6000 43P 7043-260

(200 MHz).

Links:

RS/6000

43P 7043 Model 260

POWER3:

The next generation of PowerPC processors

POWER3: Next generation 64-bit PowerPC Processor Design (PDF)

New

IBM POWER3 chip

The

POWER3 Microarchitecture

Overview

of Recent Supercomputers

History

of POWER processors

Characterization of Web Server Workloads on Three Generations of IBM PowerPC

Microarchitectures (PDF)

1999

RS64 III

1999

RS64 III

PowerPC RS64 III 64-bit

RISC microprocessor (also known as Pulsar) using copper technology. The RS64 III

microprocessor powers the in September 1999 announced RS/6000 model 7017-S80

(450 MHz). The frequency of 450 MHz was

accomplished by using IBM's new copper technology (CMOS 7S). The RS64 III has 8

MB of Level 2 (L2) cache per processor. The 6-way SMP can be expanded to a

24-way SMP and the system memory can be expanded to 96 GB.

Links:

5th

Generation 64-bit PowerPC-Compatible Commercial Processor Design

Custom

circuit design as a driver of microprocessor performance

AIX Version 4.3.3

AIX Version 4.3.3 is announced.

links:

AIX

Version 4.3.x Overview and Product Life Cycle Dates

AIX

Version 4.3.3 UNIX Operating System ( September 1999)

2000 POWER3-II

The

64-bit POWER3-II microprocessor design is based on IBM's

advanced CMOS 7S process, which is a re-implementation of POWER3

using copper interconnects. The

64-bit POWER3-II microprocessor design is based on IBM's

advanced CMOS 7S process, which is a re-implementation of POWER3

using copper interconnects.

New RS/6000 model 44P 7044-270

(375 MHz) using the 1-4 way SMP with POWER3-II copper-based

microprocessor.

The POWER3-III didn't surface, so POWER4 is the next ...

Links:

Power3-II

375/450 MHz Processors

RS/6000

44P 7044 Model 270

Why

copper?

Back

to the Future: Copper Comes of Age

|

|

| The

use copper "wiring" for integrated circuits in 1997 was a

breakthrough in semiconductor technology (smaller, faster, more

powerful and less costly). The first copper chip was a PowerPC for

Apple iMac systems (September 1998). |

|

|

eServer pSeries

I n October IBM renames RS/6000: eServer pSeries.

n October IBM renames RS/6000: eServer pSeries.

Links:

IBM

introduces servers for the next generation of e-business

A Server By Any Other

Name

RS64 IV

PowerPC RS64 IV 64-bit

RISC microprocessor (also known as Sstar) using copper and SOI technology.

The in October 2000 announced pSeries

680 (600 MHz) a is 6- to 24-way 64-bit SMP server with up to 96GB of system

memory and 16MB L2 cache for each 600 MHz processor.

Links:

A

multithreaded PowerPC processor for commercial servers

|

Silicon-on-insulator (

SOI) technology improves

performance over bulk CMOS technology by up to 35% and reduces power requirements by up to

66%. SOI refers to placing

a thin layer of silicon on top of an

insulator such as silicon oxide or glass. The transistors would then be built on

top of this thin layer of SOI. The basic idea

is that the SOI layer will reduce the capacitance (the ability of a structure to

store electrical charge) of the switch, so it will operate faster.

SOI protects the millions transistors on a chip with a blanket of insulation,

reducing harmful electrical effects that consume energy and hinder performance.

The first SOI/copper-based chip was shipped in May 1999 (a PowerPC processor

used in new AS/400 models). |

AIX 5L Version 5.1

AIX 5L Version 5.1

AIX 5L Version 5.1 is announced in April. Full 64-bit kernel,

device drivers, and application environment, and Linux affinity. AIX 5.1 also

supports 32-bit POWER architecture and Intel Itanium (on a limited basis)

architecture.

Links:

AIX 5L

AIX

5L Version 5.1

Monterey

- AIX on Itanium ?

SP2

Overview

The RS/6000 SP system hosts dozens to hundreds

of RISC processor nodes facilitating parallel processing capability.

The basic SP building block is the processor node. It consists of a POWER3

or PowerPC Symmetric Multiprocessors (SMP), memory, Peripheral Component

Interconnect (PCI) expansion slots for Input/Output (I/O) and

connectivity, and disk devices. Nodes have either a Symmetric

MultiProcessor (SMP) configuration (using PCI) or a uniprocessor

configuration (using MCA). The three types of nodes (thin, wide, and high)

may be mixed in a system and are housed in short or tall system frames.

Depending on the type of nodes used, an SP tall frame can contain up to 16

nodes and an SP short frame can contain up to 8 nodes. These frames can be

interconnected to form a system with up to 128 nodes (512 by special

order). Each node contains its own copy of the AIX operating system.

Links:

RS/6000

SP and Clustered IBM eServer pSeries Systems Handbook

RS/6000

SP Processors

Advanced Computer

Technology Center (ACTC)

RS/6000

SP Resource Center

RS/6000

SP Planning Volume 1, Hardware and Physical Environment |

The

currently used 222 MHz/375 MHz POWER3 SMP nodes, are powered by the

same POWER3 processor technology introduced with the RS/6000 43P

model 260/270 workstation.The 332 MHz SMP nodes are powered by the

PowerPC 604e processor. Earlier nodes used POWER1 (62 MHz), POWER2

(66/77 MHz), PowerPC 604 (112/200 MHz) and P2SC (120/135/160 MHz)

and POWER3 (200 MHz). The

currently used 222 MHz/375 MHz POWER3 SMP nodes, are powered by the

same POWER3 processor technology introduced with the RS/6000 43P

model 260/270 workstation.The 332 MHz SMP nodes are powered by the

PowerPC 604e processor. Earlier nodes used POWER1 (62 MHz), POWER2

(66/77 MHz), PowerPC 604 (112/200 MHz) and P2SC (120/135/160 MHz)

and POWER3 (200 MHz). |

|

Photos: Courtesy of International Business

Machines Corporation. Unauthorized use not permitted.

The

The  The IBM Scalable POWERparallel Systems (SP,

now commonly referred to as SP1)

offer a scalable platform for both serial and parallel applications. Based on

RISC System/6000 technology, the basic component of the in Februari 1993

announced

The IBM Scalable POWERparallel Systems (SP,

now commonly referred to as SP1)

offer a scalable platform for both serial and parallel applications. Based on

RISC System/6000 technology, the basic component of the in Februari 1993

announced  The model

The model  1994

Notebook

1994

Notebook

The

The

The RS64 (also known as Apache) is the

first 64-bit PowerPC RISC processor (October

1997).

The RS64 is a superscalar processor optimized for commercial workloads. The processor has separate 64 KB L1 cache for instructions and

data and L2 cache controllers. The L2 caches run at full processor speed.

The RS64 contains a 16 byte interface to 2-way set associative 4MB L2 cache. The

RS64 is also used in the AS/400 (called A35). Predecessors of the A35, only

running OS/400 are the A10 (a.k.a. Cobra), the world's first 64-bit PowerPC

microprocessor, and A25 (a.k.a. Muskie).

The RS64 (also known as Apache) is the

first 64-bit PowerPC RISC processor (October

1997).

The RS64 is a superscalar processor optimized for commercial workloads. The processor has separate 64 KB L1 cache for instructions and

data and L2 cache controllers. The L2 caches run at full processor speed.

The RS64 contains a 16 byte interface to 2-way set associative 4MB L2 cache. The

RS64 is also used in the AS/400 (called A35). Predecessors of the A35, only

running OS/400 are the A10 (a.k.a. Cobra), the world's first 64-bit PowerPC

microprocessor, and A25 (a.k.a. Muskie). The new 64-bit POWER3 processor, announced October 1998, unifies the POWER2 architecture (P2SC) with the PowerPC architecture.

The new 64-bit POWER3 processor, announced October 1998, unifies the POWER2 architecture (P2SC) with the PowerPC architecture.

The

64-bit POWER3-II microprocessor design is based on IBM's

advanced CMOS 7S process, which is a re-implementation of POWER3

using copper interconnects.

The

64-bit POWER3-II microprocessor design is based on IBM's

advanced CMOS 7S process, which is a re-implementation of POWER3

using copper interconnects.

n October IBM renames RS/6000: eServer pSeries.

n October IBM renames RS/6000: eServer pSeries.

The POWER4 "Gigaprocessor" copper SOI 64-bit CMP microprocessor is based

on all earlier designs.

The POWER4 "Gigaprocessor" copper SOI 64-bit CMP microprocessor is based

on all earlier designs.  The in October

introduced 8- to 32-way 64 bit SMP server

The in October

introduced 8- to 32-way 64 bit SMP server

The

currently used 222 MHz/375 MHz POWER3 SMP nodes, are powered by the

same POWER3 processor technology introduced with the RS/6000 43P

model 260/270 workstation.The 332 MHz SMP nodes are powered by the

PowerPC 604e processor. Earlier nodes used POWER1 (62 MHz), POWER2

(66/77 MHz), PowerPC 604 (112/200 MHz) and P2SC (120/135/160 MHz)

and POWER3 (200 MHz).

The

currently used 222 MHz/375 MHz POWER3 SMP nodes, are powered by the

same POWER3 processor technology introduced with the RS/6000 43P

model 260/270 workstation.The 332 MHz SMP nodes are powered by the

PowerPC 604e processor. Earlier nodes used POWER1 (62 MHz), POWER2

(66/77 MHz), PowerPC 604 (112/200 MHz) and P2SC (120/135/160 MHz)

and POWER3 (200 MHz).