## ADVANCED INFORMATION

November 1996

Support: ns486@arador.nsc.com

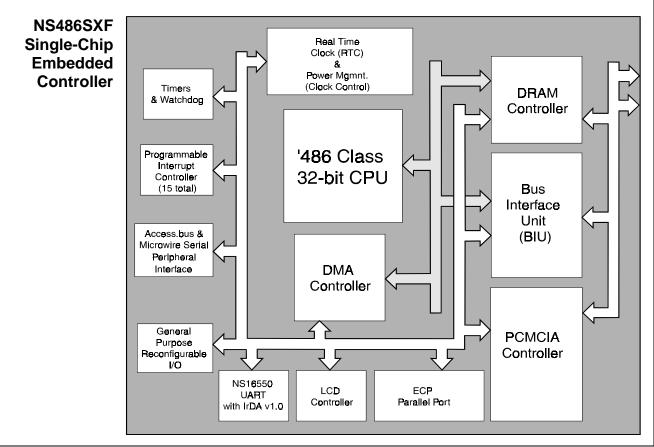

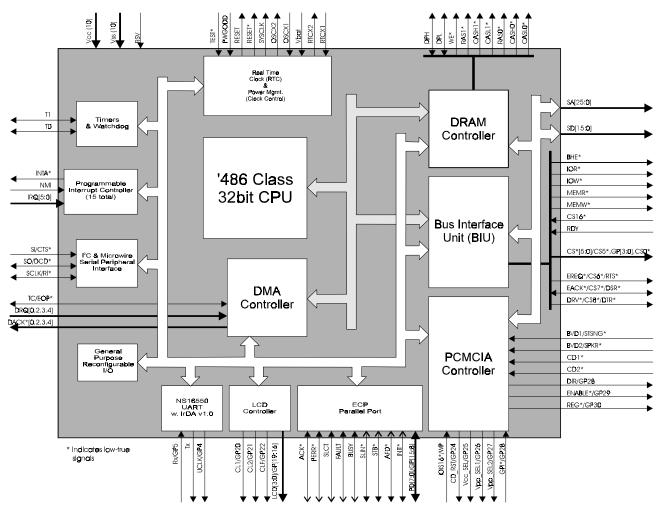

# NS486<sup>™</sup>SXF Optimized 32-bit 486-class Controller With On-chip Peripherals for Embedded Systems

## **General Description**

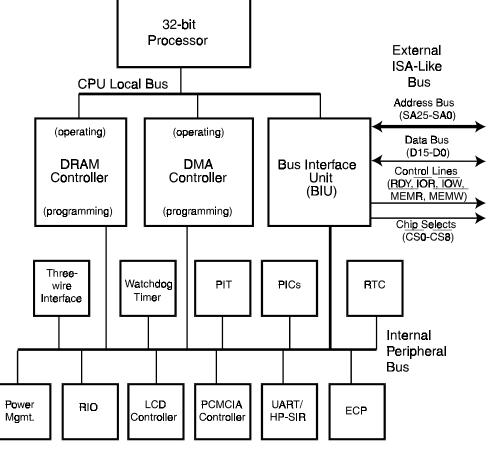

The NS486SXF is a highly integrated embedded system controller incorporating an Intel486<sup>TM</sup>-class 32-bit processor, all of the necessary System Service Elements, and a set of peripheral I/O controllers tailored for embedded control systems. It is ideally suited for a wide variety of applications running in a segmented protect-mode environment.

## **Key Features**

- 100% compatible with VxWorks<sup>®</sup>, VRTX<sup>®</sup>, QNX<sup>®</sup> Neutrino, pSOS+<sup>™</sup>, and other popular real-time executives and operating system kernels

- Intel486<sup>TM</sup> instruction set compatible (protected mode only) with optimized performance

- CPU includes a 1kByte Instruction Cache

- Operation at 25 MHz with 5 Volt supply

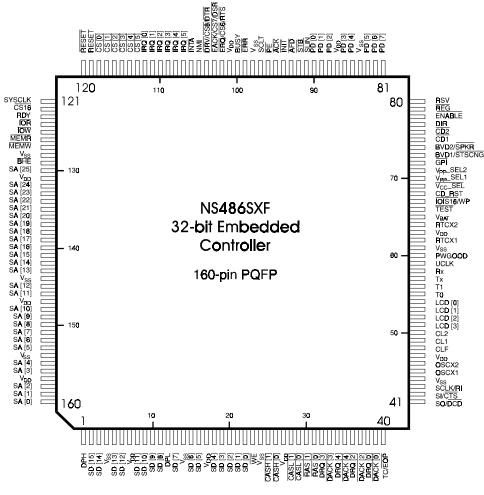

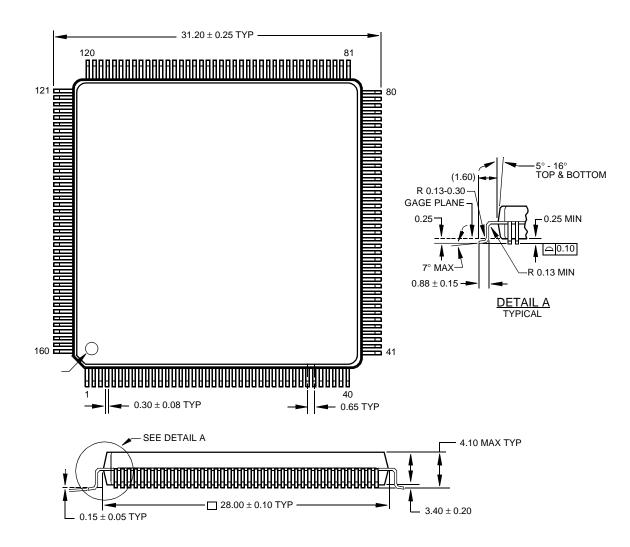

- Low cost 160-pin PQFP package

- Industry standard interrupt controller, timers, real time clock, UART with IrDA v1.0 (Infrared Data Association) port

- Intel 82365 compatible PCMCIA interface

- Protected WATCHDOG<sup>TM</sup> timer

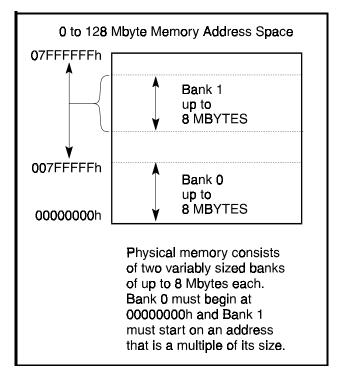

- Optimized DRAM Controller (supports two banks, up to 8 Mbytes each)

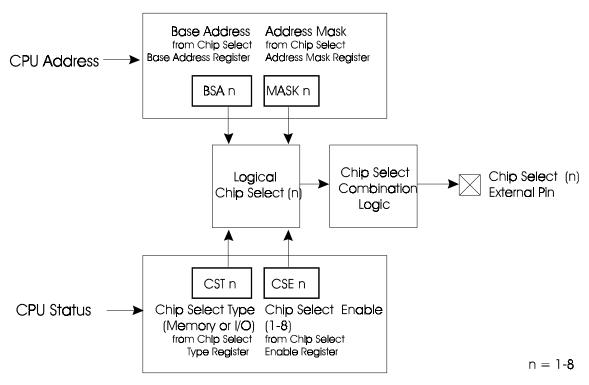

- Up to nine versatile, programmable chip selects

- Glueless interface to ISA-type peripherals

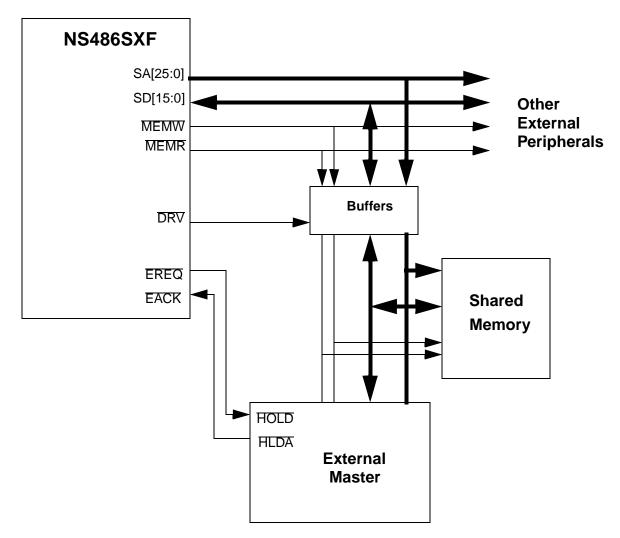

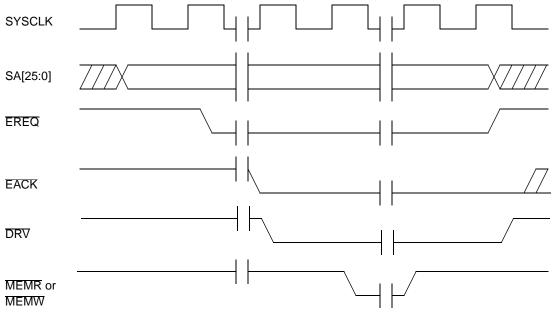

- Arbitration support for auxiliary processor

- Four external DMA channels (max. transfer rate of 25MByte/sec @ 25MHz) support many transfer modes

- High performance IEEE 1284 (ECP) Bidirectional Parallel Port

- MICROWIRE<sup>TM</sup>/Access.bus synchronous serial interfaces

- LCD Controller for monochrome supertwist Liquid Crystal Displays up to 480 X 320

- Reconfigurable I/O: Up to 29 I/O pins can be used as general purpose bidirectional I/O lines

- Flexible, programmable, multilevel power saving modes maximize power savings

© 1996 National Semiconductor Corporation • Intel486 is a trademark of Intel Corp. • NS486, WATCHDOG and MICROWIRE are trademarks of National Semiconductor Corp. • QNX is a trademark of QNX Software Systems, Inc. • VRTX is a trademark of Microtec Research, Inc. • VxWorks is a trademark of Wind River Systems, Inc. • pSOS+ is a trademark of Integrated Systems Inc.

# Contents

| 1.0 | Pi  | n Description Tables1                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 | Sy  | stem Overview11                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 2.1 | NS486SXF System Overview11                                                                                                                                                                                                                                                                                                                                                                                                             |

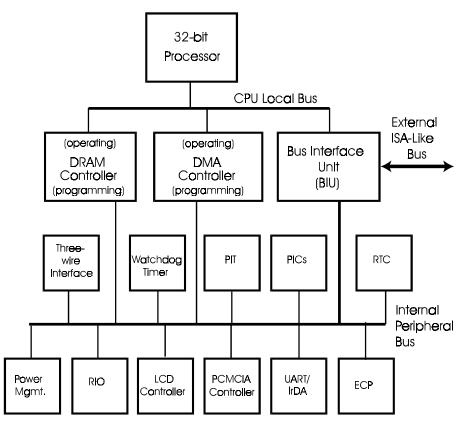

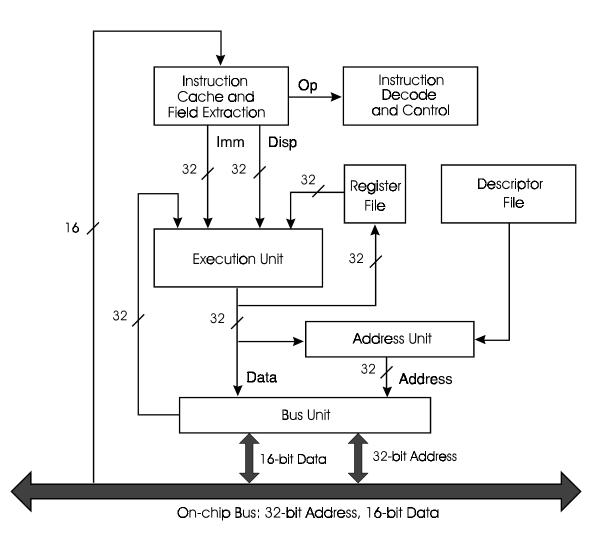

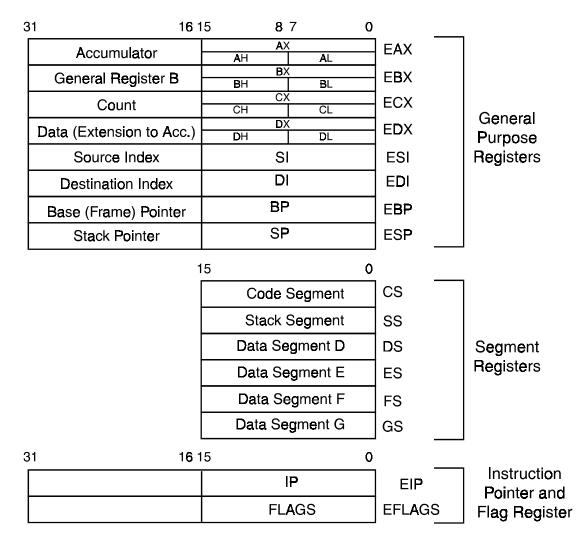

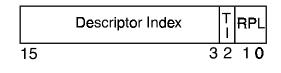

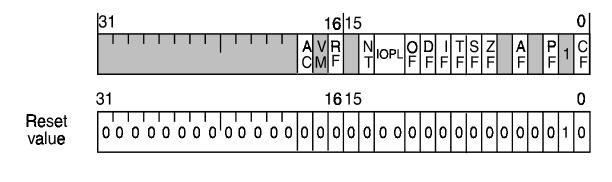

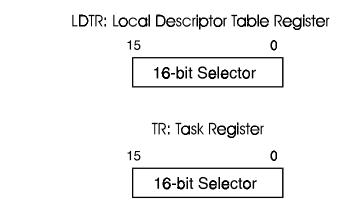

|     | 2.2 | 32-bit Processor Core12                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 2.3 | System Service Elements13                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |     | 2.3.1 DRAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |     | 2.3.2 DMA Controller13                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |     | 2.3.3 Programmable Interval Timer13                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |     | 2.3.4 WATCHDOG Timer                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |     | 2.3.5 Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |     | 2.3.7 Power Management Features14                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 2.4 | NS486SXF System Bus15                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |     | Other On-board Peripherals                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |     | 2.5.1 Reconfigurable I/O Lines                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |     | 2.5.2 IEEE 1284 Bidirectional Port16                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |     | 2.5.3 PCMCIA Interface16                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |     | 2.5.4 MICROWIRE/Access.bus Interface 16                                                                                                                                                                                                                                                                                                                                                                                                |

|     |     | 2.5.5 UART Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | •   | 2.5.6 LCD Controller                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |     | ICE Support17                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |     | Other Issues                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |     | ogramming the NS486SXF 19                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |     | I/O Address Map20                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 3.3 | System Service Elements                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |     | Reset Condition                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |     | Reset Condition                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |     | DRAM Parity Checking                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |     | DRAM Parity Checking                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28                                                                                                                                                                                                                                                                                                                                                                       |

|     |     | Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |     | Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                |

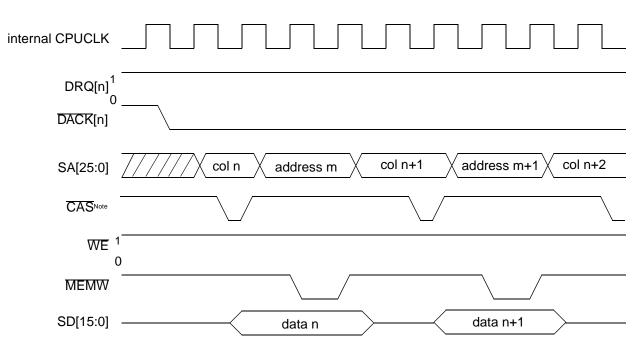

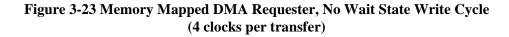

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40                                                                                                                                                                                                                                                                                             |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40                                                                                                                                                                                                                                                                            |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40                                                                                                                                                                                                                                                                                             |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40                                                                                                                                                                                                                                                             |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41                                                                                                                                                                                                    |

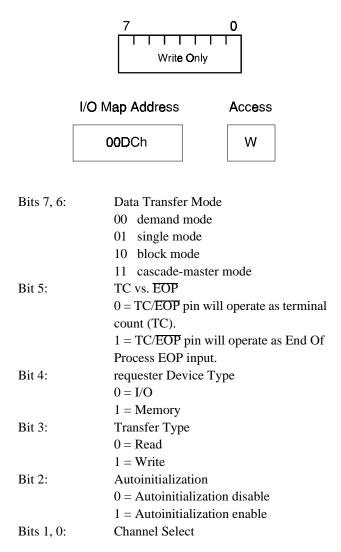

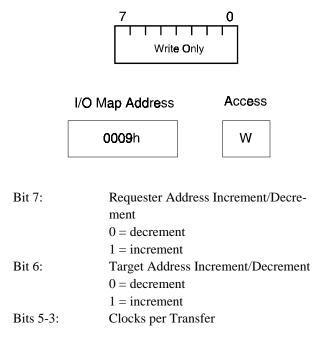

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.41DMA Configuration Registers.50                                                                                                                                              |

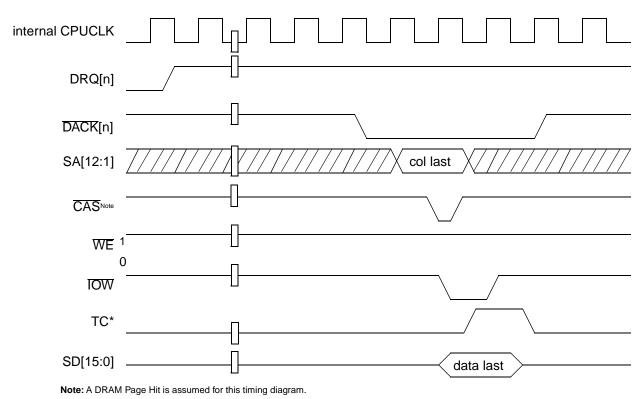

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.41DMA Configuration Registers.50 <b>3.3.3 The Programmable Interval</b>                                                                                                       |

|     |     | Refresh27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.41DMA Configuration Registers.50 <b>3.3.3 The Programmable IntervalTimer (PIT)</b> Timer (PIT).57                                                                              |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.41DMA Configuration Registers.50 <b>3.3.3 The Programmable IntervalTimer (PIT)</b> .57Programming the PIT System.58                                                           |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.41DMA Configuration Registers.50 <b>3.3.3 The Programmable IntervalTimer (PIT)</b> Timer (PIT).57Programming the PIT System.58Control Word Register.58                        |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.41DMA Configuration Registers.50 <b>3.3.3 The Programmable Interval</b> .57Programming the PIT System.58Control Word Register.58Counter Write Operations.59                   |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.50 <b>3.3.3 The Programmable Interval</b> Timer (PIT)Timer (PIT).57Programming the PIT System.58Counter Write Operations.59Counter Read Operations.59Counter Latch Command.60 |

|     |     | Refresh.27RAS Recovery (pre-charge) Rate.27The DRAM Registers.28 <b>3.3.2 The DMA Controller</b> .37DMA Transfer Modes.38Autoinitialize.40Transfer Types.40Device Types.40Maximum Performance.40Software Initiated DMA Transfers.41DMA Control Registers.50 <b>3.3.3 The Programmable Interval</b> Timer (PIT)Programming the PIT System.58Counter Write Operations.59Counter Read Operations.59                                       |

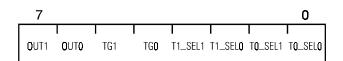

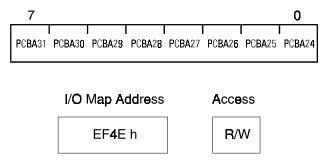

|     | Timer I/O Control Register 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

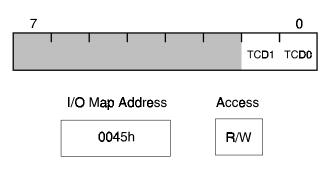

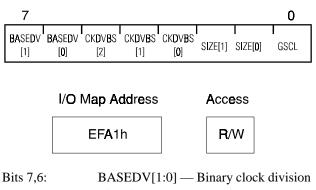

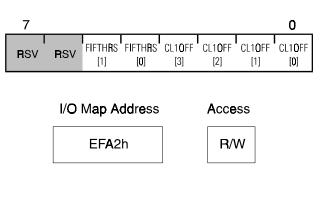

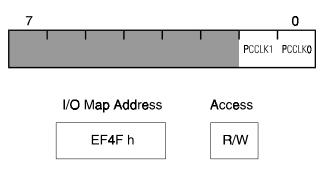

|     | Timer Clock Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | Mode Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | Gate Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

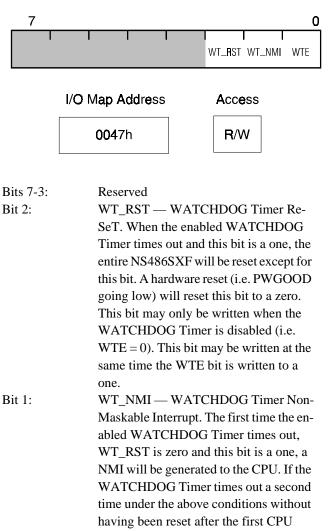

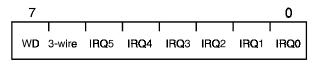

|     | <b>3.3.4</b> The WATCHDOG Timer 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | WATCHDOG Timer Control Register 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | Retriggering the WATCHDOG Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | Count to Prevent Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | Interrupt Request Supported 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | Programming Timer 2 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

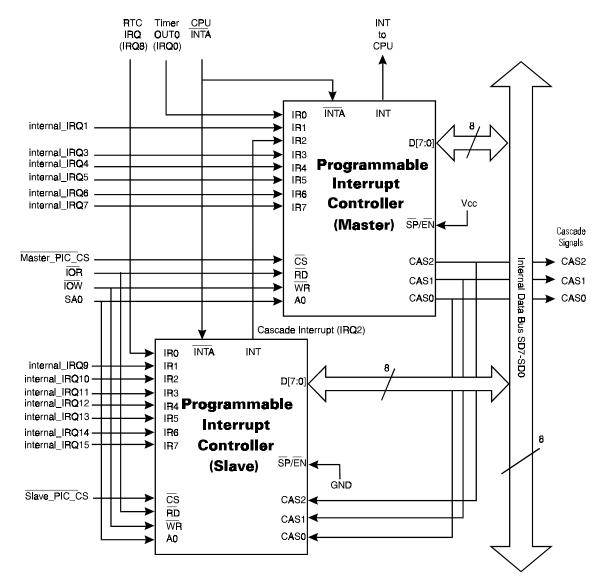

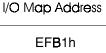

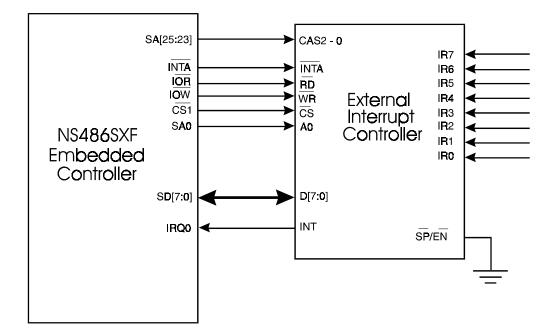

|     | 3.3.5 The Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | External Cascading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

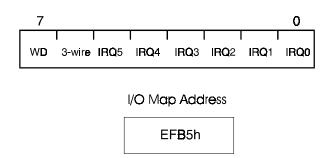

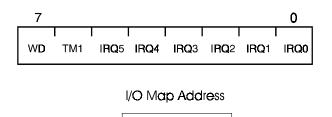

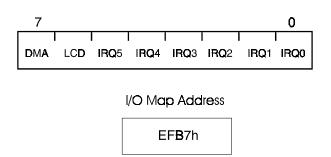

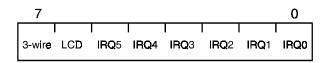

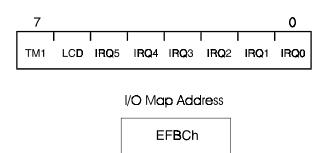

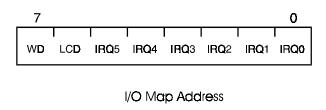

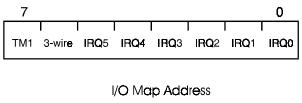

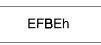

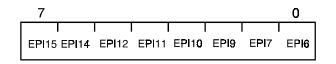

|     | Selecting Interrupt Source(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | Interrupt Source Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

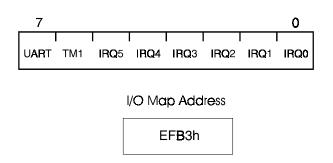

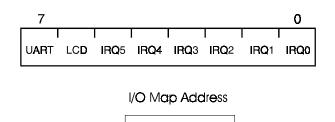

|     | Miscellaneous (PCMCIA and Extended Ca-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | pabilities Port (ECP)) Interrupt Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | Programming the PIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

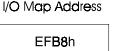

|     | General Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | Interrupt Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | End-of-interrupt (EOI) Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | Priority Nesting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | POLL Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 3.3.6 The Real Time Clock/Calendar 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | Memory Map 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

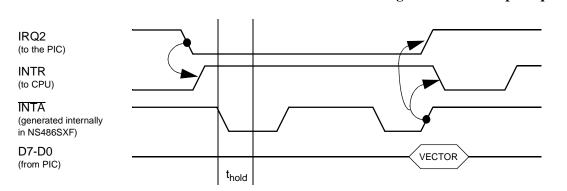

|     | Time Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

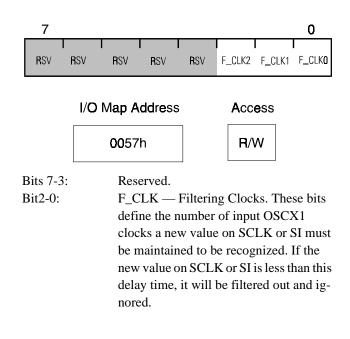

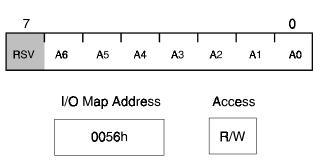

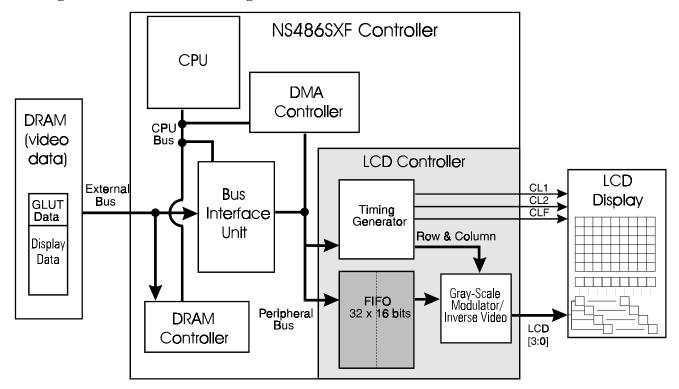

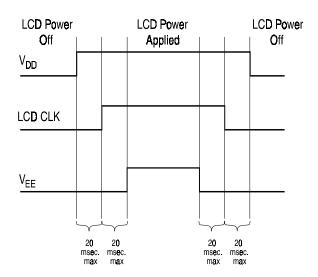

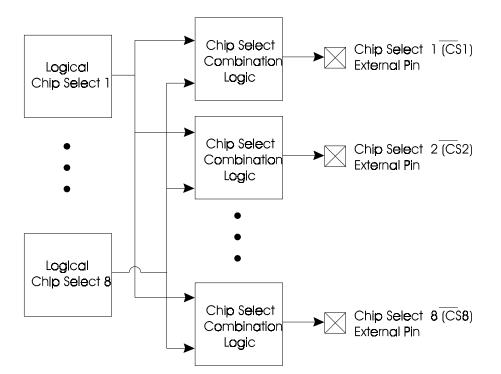

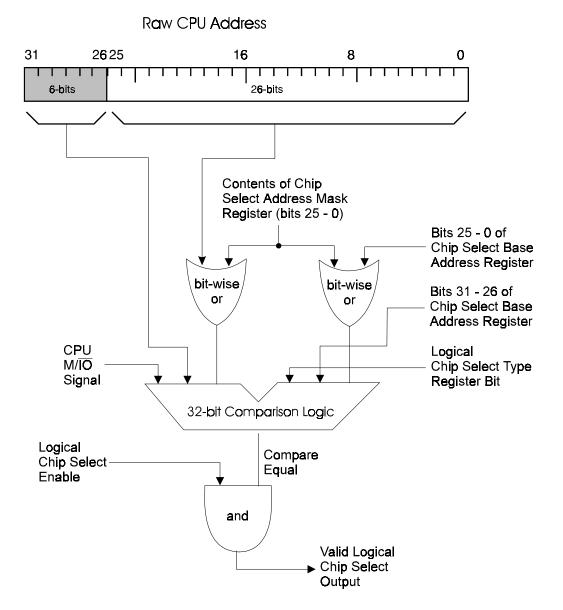

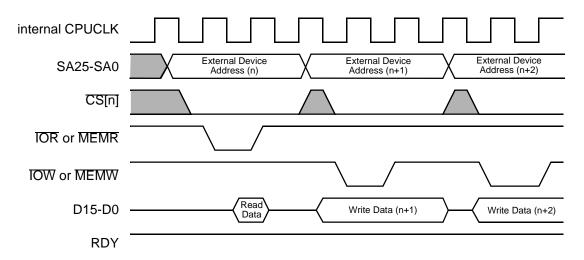

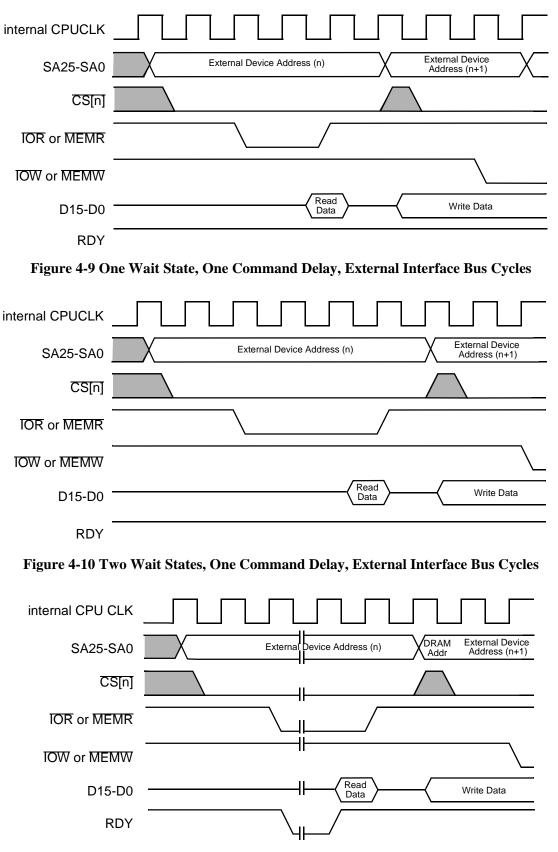

|     | RAM    91      Power Management and System Lock-out      Features    91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |