## **AP-579**

## APPLICATION NOTE

## **Pentium® Processor Flexible Motherboard Design Guidelines**

June 1997

Order Number: 243187-002

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium<sup>®</sup> processor may contain design defects or errors known as errata. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-7641

or call 1-800-879-4683 or visit Intel's website at http://www.intel.com

Copyright © Intel Corporation 1996, 1997.

Third-party brands and names are the property of their respective owners.

### CONTENTS

### PAGE

| 1.0. INTRODUCTION                                                                                             | 5  |

|---------------------------------------------------------------------------------------------------------------|----|

| 1.1. Benefits of a Flexible Motherboard                                                                       | 7  |

| 2.0. PROCESSOR DESIGN CONSIDERATIONS                                                                          | 7  |

| 2.1. Overview of the Pentium <sup>®</sup> Processor<br>Family                                                 | 8  |

| 2.2. Pinout Considerations                                                                                    | 9  |

| 2.3. Processor Identification1                                                                                | 0  |

| 3.0. FLEXIBLE MOTHERBOARD<br>IMPLEMENTATION1                                                                  | 1  |

| 3.1. Voltage Supply Implementation Overview1                                                                  | 1  |

| 3.2. The Distinct Power Planes1                                                                               | 1  |

| 3.3. Split Plane Processor/Unified Plane<br>Processor Design Configurations1                                  | 3  |

| 3.4. Power Plane Connections and Voltage<br>Regulator Shutdown1                                               | 5  |

| 3.5. Voltage Supply Implementation Options1                                                                   | 8  |

| 3.5.1. 2.8V/3.3V AUTO-CONFIGURABLE<br>REGULATOR1                                                              | 6  |

| 3.5.2. 2.8V REGULATOR AS A BUILD<br>OPTION1                                                                   | 9  |

| 3.5.3. SAFEGUARDING PENTIUM <sup>®</sup><br>PROCESSOR WITH MMX™<br>TECHNOLOGY ON THE FLEXIBLE<br>MOTHERBOARD2 | 20 |

| 3.6. Split Power Plane Layout2                                                                                | 21 |

| 3.7. Decoupling2                                                                                              | 2  |

| 3.7.1. BULK DECOUPLING2                                                                                       | 23 |

| 3.7.2. HIGH FREQUENCY DECOUPLING 2                                                                            | :3 |

| 3.7.3. DECOUPLING<br>RECOMMENDATIONS2                                                                         | 23 |

| 3.7.4. PLACEMENT OF DECOUPLING<br>CAPACITORS2                                                                 | 24 |

| 3.8. Signal Routing Guidelines2                                                                               | 26 |

|                                                        | PAGE   |

|--------------------------------------------------------|--------|

| 3.9. Thermal and Physical Space<br>Considerations      | 27     |

| 3.9.1. VOLTAGE REGULATOR THER                          |        |

| DESIGN CONSIDERATIONS                                  |        |

| 3.9.2. DESKTOP SYSTEM THERMAL                          |        |

| DESIGN CONSIDERATIONS                                  | 27     |

| 3.10. BIOS/Software Considerations                     | 28     |

| 3.11. Dual Processor Design Consideration              | ns29   |

| A1.0. VOLTAGE REGULATOR MODULE                         | 33     |

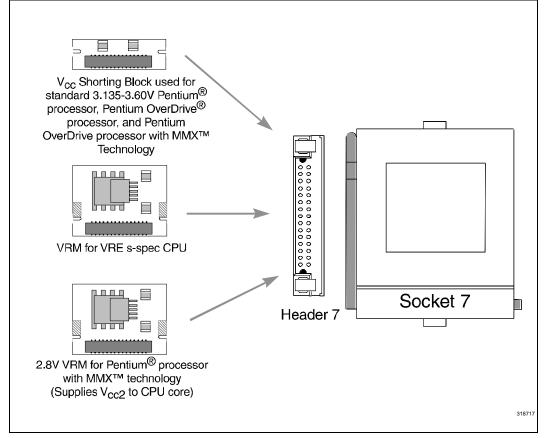

| A1.1. Header 7                                         | 34     |

| A1.2. Shorting Block or Pass-Through Mo                | dule35 |

| A1.3. VRM for Processors Running at VRI                | E 35   |

| A1.4. VRM for Pentium <sup>®</sup> Processor with M    | 1MX™   |

| Technology                                             | 35     |

| A1.5. VRM Header Placement                             | 35     |

| A2.0. VOLTAGE REGULATOR MODULE<br>HEADER PIN DIAGRAM   | 32     |

| A3.0. VOLTAGE REGULATOR MODULE C<br>PIN REFERENCE      |        |

| B1.0. SOCKET 7 PIN DIAGRAM                             | 39     |

| B2.0. SOCKET 7 QUICK PIN REFERENCE                     | 41     |

| C1.0. LINEAR AND SWITCHING REGULA<br>SOLUTIONS         |        |

| D1.0. REGULATOR VENDOR SOLUTIONS<br>CONTACT LIST       |        |

| E1.0. LIST OF RELATED TOOLS &<br>COLLATERAL            | 51     |

| E1.1. Public Documentation                             | 53     |

| E1.2. Collateral Available Under Non-Disc<br>Agreement | losure |

| 5                                                      | 54     |

E2.0. REFERENCES......54

### AP-579

# intel®

#### FIGURES

| Figure 1. Pentium <sup>®</sup> Proc<br>Motherboard | cessor Flexible                                                            |

|----------------------------------------------------|----------------------------------------------------------------------------|

| Figure 2. EAX Bit Assign                           | nments for CPUID10                                                         |

| Pentium <sup>®</sup> Pro                           | ower Planes in a Desktop<br>cessor Flexible<br>12                          |

|                                                    | cessor Family Power<br>eristics14                                          |

|                                                    | Current Flow vs. Split<br>Flow15                                           |

| Figure 6. Use of MOSFE<br>Connect/Disco            | ETs to<br>onnect Power Planes16                                            |

| Figure 7. Regulator Shu                            | tdown Phenomenon17                                                         |

| Figure 8. Auto-configura Solution                  | ble Voltage Regulator<br>18                                                |

| Figure 9. 2.8V Voltage F<br>Build Option           | Regulator Designed as a20                                                  |

| Figure 10. External Safe<br>Processor from         | eguard Circuit to Prevent<br>n Booting21                                   |

| Figure 11. External Safe<br>Output Voltage         | guard by Reducing the                                                      |

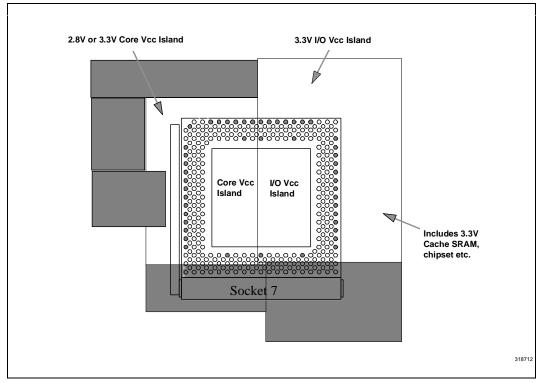

| Figure 12. Processor Po                            | ower Island Layout22                                                       |

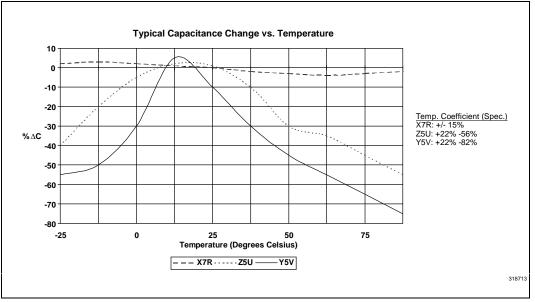

| Figure 13. Typical Capa                            | citor Characteristics25                                                    |

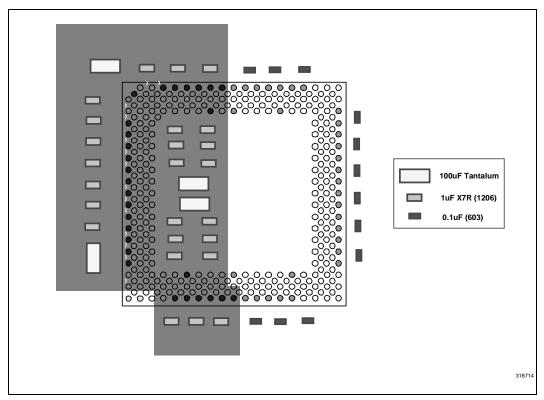

| Figure 14. Example of F<br>Capacitor Place         | Processor Decoupling<br>cement26                                           |

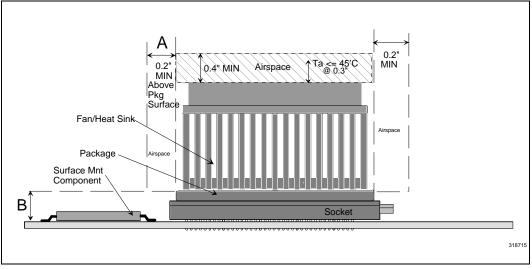

|                                                    | Physical Space<br>for Pentium OverDrive <sup>®</sup><br>nMMX™ Technology28 |

| Figure 16. Layout of a D<br>Motherboard            | P Flexible<br>30                                                           |

| Figure 17. Voltage Regu                            | lator Modules33                                                            |

| VRM Pinout Top Side Vi                             | ew36                                                                       |

| Socket 7 Pinout-Top Si                             | de View                                                                    |

|                                                    | de View40                                                                  |

### TABLES

| Table 1.                      | Pentium <sup>®</sup> Processors and Pentium<br>OverDrive <sup>®</sup> Processors and Their Key<br>Differences | y<br>a |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------|--------|--|--|

| Table 2                       | BF1-0 Core/Bus Ratio Selection Pins.                                                                          |        |  |  |

|                               | CPUID Information                                                                                             |        |  |  |

|                               | The Three Types of Pentium <sup>®</sup><br>Processor Power Planes                                             |        |  |  |

| Table 5.                      | Decoupling Recommendations for<br>Processor Core and I/O Voltage<br>Islands                                   | .23    |  |  |

| Table 6.                      | Typical Processor Voltage Supply<br>Configuration with VRM                                                    | .34    |  |  |

| 2.8V/3.3                      | V/VRE Linear Regulator Solutions                                                                              | .43    |  |  |

| 2.8V/3.3                      | V/VRE Switching Regulator Solutions                                                                           | .45    |  |  |

| On-boar                       | d Regulators                                                                                                  | .47    |  |  |

| Voltage                       | Regulator Modules                                                                                             | .48    |  |  |

| Socket 7                      | 48                                                                                                            |        |  |  |

| Header 7                      | 749                                                                                                           |        |  |  |

| Decoupli                      | ng Capacitors                                                                                                 | .49    |  |  |

| Shorting Blocks               |                                                                                                               |        |  |  |

| Resistors50                   |                                                                                                               |        |  |  |

| 3.3V Clock Driver Suppliers51 |                                                                                                               |        |  |  |

| Product Information54         |                                                                                                               |        |  |  |

| System Design Documentation54 |                                                                                                               |        |  |  |

| System I                      | Design Tools                                                                                                  | .54    |  |  |

|                               |                                                                                                               |        |  |  |

### 1.0. INTRODUCTION

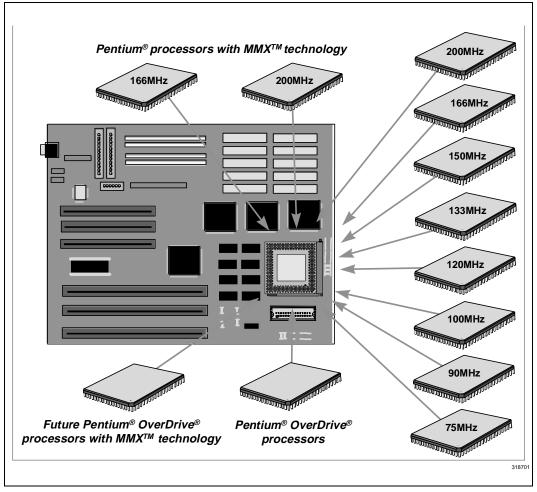

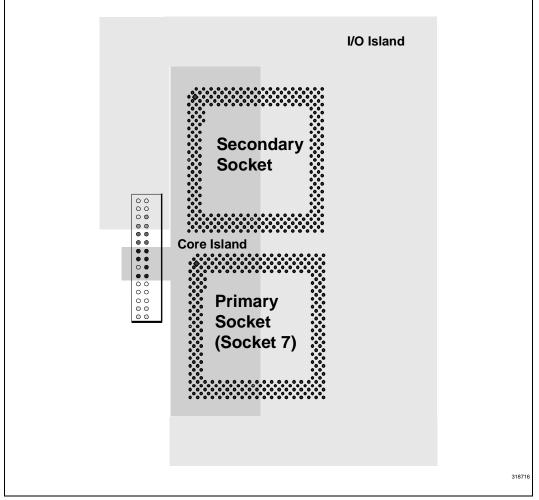

This document provides guidelines for designing a Pentium<sup>®</sup> processor family flexible motherboard. The Pentium processor family flexible motherboard, as shown in Figure 1, is a single motherboard design that can support the various members of the Pentium processor family including Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium processors with MMX<sup>™</sup> technology, Pentium OverDrive® processors, and future Pentium OverDrive processors with MMX technology.

Figure 1. Pentium® Processor Flexible Motherboard

The Pentium processor family flexible motherboard should support the following features:

- Split Power Islands: The Pentium processor family flexible motherboard should accommodate split (separate) power islands to accept processors that have split core and I/O voltage planes. The Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 and Pentium OverDrive processor have a unified core and I/O power plane internal to the processor package. The Pentium processor with MMX technology and the future Pentium OverDrive processor with MMX technology have split power planes internal to the processor with MMX technology receive two different voltages (i.e., 2.8V for the Core and 3.3V for the I/O).

- 3.3V Power Source: Pentium processors 75/90/ 100/120/133/150/166/200, Pentium OverDrive processors and future Pentium OverDrive processor with MMX technology receive 3.3V ( 3.135 – 3.6V) from the processor socket for operation. The Pentium processor family flexible motherboard should provide 3.3V by using a system power supply unit or a voltage regulator.

- 2.8V Power Source: The Pentium processor with MMX technology receives 2.8V (±100 mV) for its core. The Pentium processor family flexible motherboard should provide support for a 2.8V power source through either an on-board 2.8V voltage regulator or a Voltage Regulator Module (see Appendix A).

- Socket 7: The Pentium processor family flexible motherboard should implement a Socket 7. Pin assignments vary according to processors, and Socket 7 is a processor socket designed to accept all processors in the Pentium processor family (i.e., Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200. Pentium OverDrive processors. Pentium processors with MMX technology and future Pentium processors with MMX technology) regardless of their differences in pin assignments or power plane implementation. Socket 7 is a 321-pin ZIF socket and is a superset of the older 320-pin Socket 5. Socket 7 provides the option and capability to support both unified-plane processors and split-plane, dual-voltage supply processors and requires that CLK and PICCLK be driven at 3.3V levels. Socket 7 electrical specifications list the maximum current for the future Pentium processors with MMX

technology upgradability as 5.0A at 3.3V; however, the Pentium processor with MMX technology has a core current draw of 5.7A at 2.8V.

#### NOTE

The current draw is processor dependent and any processor belonging to the Pentium processor family may be utilized in a Socket 7 provided the system design provides adequate current.

- Local Decoupling: Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processors, Pentium processors with MMX technology and future Pentium OverDrive processors with MMX technology may cause rapid fluctuation of current during transitions between "low-power" states and "active" states. The Pentium processor family flexible motherboard provides accurate and adequate decoupling capacitors near the processor socket to prevent violation of the voltage supply range specification.

- Multiple Bus Frequencies: Pentium processors 75/90/100/120/133/150/166/200, Pentium OverDrive processors, and future Pentium OverDrive processors with MMX technology support external bus frequencies of 50 MHz, 60 MHz and 66 MHz. The Pentium processor with MMX technology supports external bus frequencies of 60 MHz and 66 MHz. The Pentium processor family flexible motherboard is implemented with system logic compatible with the AC timing parameters at these bus frequencies.

- Bus-to-Core Ratio: The Pentium processor family flexible motherboard should provide jumpers for bus fraction pin strapping options to allow for flexibility in configuring the external bus frequency to internal core frequency ratio. The bus-to-core ratios can be either 1/3, 2/5, 1/2 or 2/3. In order to support all Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 and Pentium processors with MMX technology, selection jumpers should allow a high or low logic setting for both bus fraction pins (BF1 and BF0).

#### NOTE

Not all Pentium OverDrive processors and future Pentium OverDrive processors with MMX technology internally configure the bus fraction, and jumper changes are not required when a Pentium OverDrive processor or a future Pentium OverDrive processor with MMX technology is installed in a Socket 7 system.

- Thermal and Mechanical Specifications: The Pentium processor family flexible motherboard should be designed to meet the thermal and mechanical specifications of the Socket 7 Specification, Rev. 3.0.

- BIOS Support: Each processor stepping is assigned a unique identification and feature signature. The execution of the CPUID instruction will retrieve these signatures for identification. The Pentium processor family flexible motherboard provides a system BIOS capable of supporting all Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processors, Pentium processors with MMX technology and future Pentium processors with MMX technology steppings. Through the use of the CPUID instruction, the BIOS can determine whether the processor supports certain features like APIC or MMX technology. (For more details, refer to application note AP-485, Intel Processor Identification with the CPUID Instruction. See Appendix E.)

- 3.3V Clock Drivers: Clock inputs on Pentium ٠ processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processors, Pentium processors with MMX technology and future Pentium OverDrive processors with MMX technology can accept 3.3V clock drivers but not all are 5V tolerant. The Pentium processor family flexible motherboard provides a 3.3V clock driver (for CLK and PICCLK) to ensure compatibility with all Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processors, Pentium processors with MMX technology and future Pentium OverDrive processors with MMX technology.

### Benefits of a Flexible Motherboard

1.1.

Producing a flexible motherboard design for the Pentium processor family offers several benefits:

- Offers various price/performance options: One flexible design, when populated by different members of the Pentium processor family, can provide a wide range of price/performance options. Flexibility can also be achieved through assembly time options for other components on the motherboard. For example, external caches may use asynchronous SRAM for cost effectiveness or pipelined burst SRAM for higher performance. Synchronous burst DRAM may replace extended data out (EDO) DRAM as main memory to maintain performance in costeffective platforms with optional external cache memory.

- Reduces design and validation effort associated with multiple designs: The board does not have to be revised for every proliferation of the processor thus reducing design and validation efforts. Instead, one board is designed to accept various processors that can be populated at build-time.

- Reduces inventory and manufacturing costs: Only one motherboard design has to be manufactured and has to be maintained in inventory. This reduces the overall inventory management and manufacturing costs. For a varying product demand, the board can be populated with the appropriate processor to meet the current market demand.

- Reduces debug and technical support costs: Instead of several, only one motherboard has to be debugged. The field engineers and other support personnel need only to be trained on one base motherboard design thus reducing overall technical support efforts.

### 2.0. PROCESSOR DESIGN CONSIDERATIONS

This chapter describes the differences between the various processors that need to be considered when designing a Pentium processor family flexible motherboard.

### 2.1. Overview of the Pentium<sup>®</sup> Processor Family

Table 1 shows the members of the Pentium processor family that are supported on the flexible motherboard and highlights their respective electrical/thermal specifications. The following is a brief description of the Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processors, Pentium processors with MMX **OverDrive** future Pentium technology and processors with MMX technology processors that are supported on the flexible motherboard. Please refer to Appendix E in order to obtain specifications for each processor.

The Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 is a 3.3V processor that operates at 75, 90, 100, 120, 133, 150, 166 and 200 MHz core speeds (50, 60, and 66 MHz external bus speeds). This is a unified plane processor that uses 3.3V [Standard (3.135V - 3.6V) or VRE (3.4V - 3.6V) voltage] for all V<sub>CC</sub> pins.

The Pentium processor with MMX technology 166/200 is the newest addition to the Pentium processor family. Several architectural enhancements have been made: the internal data and code cache sizes have each been doubled from 8 Kbytes to 16 Kbytes, the branch prediction has been improved, and support for Intel MMX technology has been added. MMX technology is an extension to the Intel Architecture (IA) instruction set which adds 57 new opcodes and a new MMX register set. The Pentium processor with MMX technology operates at core frequencies of 166 and 200 MHz (60 and 66 MHz external bus speeds). The Pentium processor with MMX technology uses 2.8V for its internal core while its I/O operates at 3.3V (to provide full compatibility with existing chipset and SRAM). It is pin, package, and functionally compatible with the Pentium processor 75 / 90 / 100 /120/133/150/166/200 and is operating system transparent. The Pentium processor with MMX technology's CLK and PICCLK buffers are not 5V tolerant and should only use 3.3V clock inputs.

The Pentium OverDrive processor 125/150/166 is the upgrade processor for the Pentium processor 75/90/100-based systems. It plugs into either Socket 5 or Socket 7 based designs. Pentium OverDrive processors are end-user, single-chip processor upgrade products for Pentium processor systems that speed up nearly all software applications and are binary compatible with the Pentium processor.

The future Pentium OverDrive processor with MMX technology 125/150/166/180/200 is the end-user, single chip, processor upgrade for the Pentium processor 75/90/100/120/133-based Socket 5 or Socket 7 designs. The future Pentium OverDrive processor with MMX technology 180/200 can also upgrade Pentium processor 150/166/180/200-based designs to MMX technology, but with a lower overall performance increase. The 200 MHz future Pentium OverDrive processor with MMX technology will only be supported by Socket 7-based designs.

### 2.2. Pinout Considerations

For the processors that are supported on the flexible motherboard, most of the signals are compatible to each other. The differences are noted below:

- V<sub>CC2</sub>, V<sub>CC3</sub>: On the Pentium processor with MMX technology, the internal bus logic is isolated from the core logic so that the core can run at a lower voltage (2.8V) in order to obtain faster core frequencies and reduce overall power consumption. The bus logic remains at 3.3V to remain compatible with existing chipsets and cache SRAM. The voltage for the core logic is supplied through the V<sub>CC2</sub> pins and the voltage for the bus logic is supplied through the V<sub>CC3</sub> pins. The motherboard design therefore splits the processor power plane into a separate 2.8V core voltage island and a 3.3V I/O voltage island.

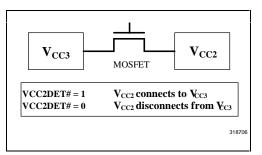

- VCC2DET#: This is a new signal defined on the Pentium processor with MMX technology to indicate to the system that the processor installed in the processor socket uses an isolated 2.8V core supply on the V<sub>CC2</sub> pins. This pin is internally connected to ground on the Pentium processor with MMX technology. On Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processors, and future Pentium OverDrive processors with MMX

| tech | nology, this | pin is | defined | as | INC (Int | ernal |

|------|--------------|--------|---------|----|----------|-------|

| No   | Connect).    | This   | signal  | is | pulled   | high  |

externally on the flexible motherboard or left as a no connect otherwise.

|                                    | Pentium <sup>®</sup> Processor               | Pentium Processor<br>with MMX™<br>Technology | Pentium<br>OverDrive <sup>®</sup><br>Processor | Future Pentium<br>OverDrive Processor<br>with MMX Technology |

|------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------------------------|--------------------------------------------------------------|

| Core Frequency                     | 75, 90, 100, 120, 133,<br>150, 166, 200      | 166, 200                                     | 125, 150, 166                                  | 125, 150, 166, 180, 200 <sup>(7)</sup>                       |

| Bus Frequency                      | 50, 60, 66                                   | 60, 66                                       | 50, 60, 66                                     | 50, 60, 66                                                   |

| Frequency Ratio                    | 1/2, 2/3, 2/5,1/3                            | 2/5,1/3                                      | 2/5 (4)                                        | 2/5, 1/3 <sup>(4)</sup>                                      |

| Clock Level                        | 3.3V or 5V                                   | 3.3V                                         | 3.3V or 5V                                     | 3.3V or 5V (7)                                               |

| Core Supply                        | 3.135V – 3.60V (STD);<br>3.40V – 3.60V (VRE) | 2.7V – 2.9V                                  | 3.135 – 3.6V                                   |                                                              |

| I/O Supply                         | 3.135V – 3.60V (STD);<br>3.40V – 3.60V (VRE) | 3.135V – 3.60V                               | 3.135 – 3.6V                                   |                                                              |

| I <sub>CC2</sub> <sup>(1, 5)</sup> | Connected to I <sub>CC3</sub>                | 5700mA (200 MHz)<br>4750mA (166 MHz)         | Connected to $I_{CC3}$                         | Note (6)                                                     |

| I CC3 <sup>(2, 5)</sup>            | 4600mA (200 MHz)<br>2650mA (75 MHz)          | 650mA (200 MHz)<br>540mA (166 MHz)           | 4330mA                                         | 5000mA (200 MHz) <sup>(6)</sup><br>4330mA(125–180 MHz)       |

| I CC5 (3, 5)                       | Not Applicable                               | 200mA                                        | 200mA                                          |                                                              |

| Max. Power <sup>(5)</sup>          | 15.5W (200 MHz)                              | 15.7 W (200 MHz)                             | 15.0 W                                         | 17.0W (200 MHz)<br>15.0W (125–180 MHz)                       |

| No. of $V_{CC2}$ Pins              | None                                         | 25                                           | None                                           | 28                                                           |

| No. of $V_{CC3}$ Pins              | 53                                           | 28                                           | 60                                             | 32                                                           |

| No. of $V_{CC5}$ Pins              | None                                         | 2                                            | 2                                              |                                                              |

| External Plane<br>Type             | Unified                                      | Split                                        | Unified                                        | Unified or Split                                             |

| Internal Plane<br>Type             | Unified                                      | Split                                        | Unified                                        | Split                                                        |

| Package Type                       | 296-pin PPGA or<br>CPGA                      | 296-pin PPGA or<br>CPGA                      | 320-pin CPGA                                   | 320-pin CPGA                                                 |

| Table 1. Pentium <sup>®</sup> Processors and Pentium OverDrive <sup>®</sup> Processors ar | d Their Key Differences |

|-------------------------------------------------------------------------------------------|-------------------------|

|-------------------------------------------------------------------------------------------|-------------------------|

#### NOTES:

1. I  $_{CC3}$  refers to V $_{CC3}$  (I/O) supply current.

- 2.  $I_{CC2}$  refers to  $V_{CC2}$  (Core) supply current.

- 3. I <sub>CC5</sub> refers to 5V supply current. This is used to power the fan/heatsink on the Pentium® OverDrive® processors.

- 4. Pentium OverDrive processors and future Pentium OverDrive processors with MMX<sup>™</sup> technology do not require the bus frequency ratio to be changed when upgraded.

- 5. The number shown represents worst case or maximum current/power at highest available frequency.

- 6. When the future Pentium OverDrive processor with MMX technology is installed in split plane designs, 4600 mA at 3.3V is drawn through  $V_{CC2}$  pins and 400 mA from  $V_{CC3}$  pins.

- 7. The 200 MHz future Pentium OverDrive processor with MMX technology will only be supported in Socket 7 designs.

- BF1-0: The bus fraction selection pins determine the bus to core frequency ratio. The BF pins are sampled by the processor at RESET, and will not be sampled by the processor again until another cold-boot (1ms) assertion of RESET. The signal on the BF pins is not an indication of the bus speed, only the ratio of the processor core with respect to the bus. The Pentium OverDrive processor and future Pentium OverDrive processor with MMX technology do not require the BF pins to be changed when upgraded and will operate properly with the bus fraction ratio selected for the processor being replaced. Table 2 summarizes the operation of the BF pins on Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 and Pentium processors with MMX technology.

- CLK, PICCLK: The clock inputs on the Pentium processor with MMX technology are not 5V tolerant. The clock inputs to the processor on the flexible motherboard are driven by an appropriate 3.3V clock driver. Driving the clock at 3.3 volts is also compatible with the Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, the Pentium OverDrive processor, and the future Pentium OverDrive processor with MMX technology.

### 2.3. Processor Identification

The CPUID instruction is used to provide information to the BIOS and other software about the vendor, family, model, and stepping of the processor. An input value of 1 loaded into the EAX register prior to executing the CPUID instruction will return the identification signature in the EAX register. Figure 2 shows the EAX bit assignment for the CPUID instruction. (For more details, refer to application note AP-485, Intel Processor Identification with the CPUID Instruction. See Appendix E.)

| 31           | 14 | 13 12 | 211 | 8   | 7  | 4   | 3    | 0      |

|--------------|----|-------|-----|-----|----|-----|------|--------|

| 0 (reserved) |    | type  | fam | ily | mo | del | step | ping   |

|              |    |       |     |     |    |     |      | 318702 |

#### Figure 2. EAX Bit Assignments for CPUID

Table 3 provides the CPUID information for the different processors that are supported on the flexible motherboard.

| BF1 Value <sup>(5)</sup> | BF0 Value <sup>(5)</sup> | Pentium <sup>®</sup> Processor<br>75 / 90 / 100 / 120 / 133 / 150 / 166<br>200<br>Frequency Ratio | Pentium Processor with MMX™<br>Technology Frequency Ratio |

|--------------------------|--------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 0                        | 0                        | 2/5 <sup>(2)</sup>                                                                                | 2/5 <sup>(2)</sup>                                        |

| 0                        | 1                        | 1/3                                                                                               | 1/3                                                       |

| 1                        | 0                        | 1/2 (3)                                                                                           | 1/2 <sup>(3)</sup> (Default)                              |

| 1                        | 1                        | 2/3 <sup>(4)</sup> (Default)                                                                      | Reserved                                                  |

| Table 2. BF1-0 Core/Bus Ratio Selection Pins |

|----------------------------------------------|

|----------------------------------------------|

#### NOTES:

1. The Pentium processors with a maximum rated core frequency of less than 75 MHz have only one bus fraction ratio defined – (1:1).

The 2/5 ratio is defined on the Pentium<sup>®</sup> processor with MMX<sup>™</sup> technology and Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200.

Defaults to 1/2 ratio if BF1 and BF0 are left unconnected on the Pentium processor with MMX technology. On the Pentium

processor with MMX technology, the BF1 pin has an internal pull-up resistor, and the BF0 pin has an internal pull-down

resistor.

Defaults to 2/3 ratio if BF1 and BF0 are left unconnected on Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200. On the Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, the BF1 and BF0 pins have internal pull-up resistors.

5. The value of external pull-down resistors used on the BF0/BF1 pins should be 500 ohms or less. The value of external pull-up resistors used on the BF0/BF1 pins should be 2.2 Kohms or less.

| Type<br>Bits(13:12) | Family<br>Bits(11:8) | Model<br>Bits(7:4) | Stepping<br>Bits(3:0) | Description                                                                                                              |

|---------------------|----------------------|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------|

| 00                  | 0101                 | 0010               | хххх                  | Pentium <sup>®</sup> processors (75, 90, 100, 120, 133, 150, 166, 200)                                                   |

| 00                  | 0101                 | 0100               | хххх                  | Pentium processor with MMX <sup>™</sup> technology (166, 200)                                                            |

| 00 (1)              | 0101                 | 0010               | хххх                  | Pentium OverDrive <sup>®</sup> processor for Pentium processor (75, 90, 100)                                             |

| 01                  | 0101                 | 0100               | хххх                  | Future Pentium OverDrive processor with<br>MMX technology for Pentium processor (75,<br>90, 100, 120, 133, 150, 166, 200 |

#### Table 3. CPUID Information

#### NOTES:

1. The definition of the type field for the OverDrive<sup>®</sup> processor is 01. An errata on the Pentium<sup>®</sup> OverDrive processor will always return 00 as the type.

## 3.0. FLEXIBLE MOTHERBOARD IMPLEMENTATION

This chapter describes the implementation of a split plane flexible motherboard using Socket 7.

#### 3.1. Voltage Supply Implementation Overview

In order to support the various members of the Pentium processor family with different voltage requirements, the flexible motherboard should include provisions for both 2.8V and 3.3V supply voltages for the processor.

The power supply pins on the Pentium processor with MMX technology are split into separate  $V_{CC2}$  and  $V_{CC3}$  pins. Socket 7 definition splits the 60  $V_{CC}$  pins on Socket 5 into 28  $V_{CC2}$  pins and 32  $V_{CC3}$  pins. These pins are connected appropriately to the processor core voltage island and processor I/O voltage island. The Pentium processor with MMX technology uses 5.7A at 2.8V (200 MHz) for its core from the supply voltage solution. The 3.3V I/O voltage for the Pentium processor with MMX technology is supplied by the system (either through the 3.3V power supply or through a 3.3V voltage regulator on the motherboard).

The voltage provided to the core of the future Pentium OverDrive processor with MMX technology is supplied by a voltage regulator, internal to the OverDrive processor package, powered by 3.3V on the  $V_{CC2}$  pins. The I/O is powered directly from the 3.3V  $V_{CC3}$  pins. The voltage supply solution on the flexible motherboard supplies a minimum of 0.4A at 3.3V on  $V_{CC3}$  and 4.6A at 3.3V on  $V_{CC2}$  to support the 200 MHz future Pentium OverDrive processor with MMX technology. It is not required that both power planes be supplied by the same source. In addition, the Pentium OverDrive processor and future Pentium OverDrive processor with MMX technology also use a +5V supply to power the fan/heatsink.

In a typical single processor system, the 3.3V power supply uses approximately 7A to power all the 3.3V components (i.e. processor, cache and chipset). In the 200 MHz Pentium processor with MMX technology, the 2.8V regulator draws up to approximately 5.7A at 2.8V for the processor core while the 3.3V power supply should require approximately 2A at 3.3V for the cache and chipset. Additional 3.3V devices such as 3.3V DRAM may require additional power. Actual power requirements should be calculated for the specific design.

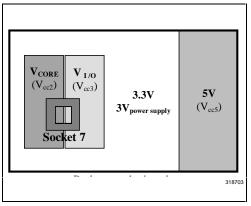

### 3.2. The Distinct Power Planes

A typical desktop flexible motherboard contains a maximum of four different power planes. Any Pentium processor will directly plug into two of these planes (V<sub>CC2</sub>, V<sub>CC3</sub>) and may be indirectly connected to the 3.3V power supply ( $3V_{POWER}$  SUPPLY) through the V<sub>I/O</sub> (V<sub>CC3</sub>) power plane. See Figure 3. For the most economically flexible motherboard design, it is recommended that the V<sub>I/O</sub> plane simply be connected to the

motherboard's 3V<sub>POWER SUPPLY</sub> by jumpers or 0 $\Omega$  resistors. Therefore, excluding the main 5V power plane, the Pentium processor family flexible motherboard may have a minimum of two distinct motherboard power planes: V<sub>CORE</sub> and V<sub>I/O</sub> + 3V<sub>POWER SUPPLY</sub>. However, some board designers may power the V<sub>I/O</sub> plane with VRE voltage instead and keep it isolated from the 3V<sub>POWER SUPPLY</sub>. This will then maintain the total possibility of four separate power planes.

The power plane distinctions are described below.

V<sub>CORE</sub> — This power plane is connected to the V<sub>CC2</sub> power pins on the Pentium processor family's Socket 7 connector (see Figure 3). When a Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 is installed in the system, this plane will typically be connected to the  $V_{I/O}$  plane through  $0\Omega$  resistors, jumpers, or the internal power plane of the Pentium processor. However, in the case of the Pentium processor with MMX technology, the V<sub>CC2</sub> and V<sub>CC3</sub> planes remain completely electrically separate. Also, the future Pentium OverDrive processor with MMX technology will not connect V<sub>CC2</sub> and V<sub>CC3</sub> through its internal power planes. Depending upon which processor is being supported, the V<sub>CC2</sub> plane may require either a discrete 2.8V voltage regulator, or a configurable 2.8V/3.3V/VRE voltage regulator. The VCC2DET# signal can be used to select between 2.8V and 3.3V/VRE on the configurable VCORE voltage regulator. The V<sub>CORE</sub> power plane uses a voltage regulator that can supply at least 5.0A at 3.3V for a Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 and at least 5.7A at 2.8V for a Pentium processor with MMX technology.

$V_{I/O}$  — This power plane is connected to the  $V_{CC3}$ power pins on the Pentium processor family's Socket 7 connector. The V<sub>I/O</sub> plane may also be connected to the motherboard's 3VPOWER SUPPLY plane (if the motherboard power supply is used instead of a 3.3V/VRE voltage regulator). Therefore, the V<sub>I/O</sub> plane may require either an electrical connection to the motherboard's 3VPOWER SUPPLY, or its own discrete 3.3V/VRE voltage regulator. When isolated from the 3VPOWER SUPPLY, the processor's V<sub>CC3</sub> pins may only require as little as 0.65A (at 200 MHz) as is the case in the Pentium processor with MMX technology. However, in order to minimize the number of discrete 3.3V voltage regulators in a flexible motherboard, it is recommended that the  $V_{I/O}$  plane connect the processor's V<sub>CC3</sub> pins with the motherboard's L2 cache, chipset and any 3.3V DRAM. Since the Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 (a unified-plane processor) has its V<sub>CORE</sub> + V<sub>I/O</sub> plane supplied with VRE voltage, the  $V_{CORE} + V_{I/O}$  plane may need to be isolated from the 3.3V components and 3VPOWER SUPPLY. See Figure 5. An auto-configurable flexible should make motherboard provisions for connecting/disconnecting the VI/O and 3VPOWER SUPPLY in order to accommodate processors running on VRE voltage or 3.3V voltage (see next section).

$3V_{POWER SUPPLY}$  — This power plane is the motherboard's 3.3V power plane (not to be confused with the motherboard's 5V power plane). This typically powers the 3.3V cache, chipset and DRAM components on the Pentium processor family flexible motherboard. In cost effective motherboards, the  $3V_{POWER}$  supply is typically connected to the  $V_{I/O}$  power plane; however, if the processor is a unified-plane processor, this plane will then be connected to both the  $V_{I/O}$  and  $V_{CORE}$  power planes as well (see next section). In a split plane, dual voltage processor, like the Pentium processor with MMX technology, the  $3V_{POWER}$  supply plane will be separated from the  $V_{CORE}$  power plane.

#### NOTE

The future Pentium OverDrive approcessor with MMX technology will not internally connect  $V_{CORE}$  to  $V_{I/O}$ .

5V<sub>POWER SUPPLY</sub>— This is the motherboard's 5V power plane. This plane will power the 5V components such as DRAM, keyboard controller, mouse, FLASH BIOS memory, TTL Logic, and some I/O bus components and connectors.

#### 3.3. Split Plane Processor/Unified Plane Processor Design Configurations

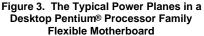

Currently, the Pentium processor family line may be divided into three power plane categories (*see Figure 4 and Table 4*):

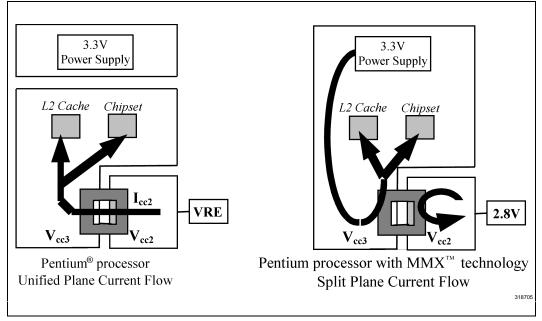

The Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 and Pentium OverDrive processor have an internal unified power plane. This means that the V<sub>CC2</sub> and V<sub>CC3</sub> power pins are connected to a single power plane internal to the processor package. The processor may be operated by applying 3.3V/VRE to both the V<sub>CC2</sub> power pins and V<sub>CC3</sub> power pins simultaneously, or by applying 3.3V/VRE power to either the V<sub>CC2</sub> pins or the V<sub>CC3</sub> pins separately. Since the internal power plane is unified, the power from the V<sub>CC2</sub> pins will flow to the V<sub>CC3</sub> pins and vice-versa.

In designing flexible motherboard options, the  $V_{CORE}$  and  $V_{I/O}$  power planes may be electrically isolated or they may be shorted together by jumpers or  $0\Omega$  resistors. In the case where the V<sub>CORE</sub> and V<sub>I/O</sub> power planes are isolated (and there are no jumpers or  $0\Omega$  resistors to combine the two motherboard power planes), the Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 and Pentium OverDrive processor will serve as the means of conduction that shorts the two power planes together provided the current flow through the processor does not exceed 8A. See Figure 5. This scenario would never occur with a Pentium processor with MMX technology, nor with a future Pentium OverDrive processor with MMX technology, because of their internal split power plane design.

Figure 4. Pentium<sup>®</sup> Processor Family Power Plane Characteristics

| Table 4. The Three Ty | pes of Pentium <sup>®</sup> Processor Power Planes |

|-----------------------|----------------------------------------------------|

| <b>0</b> /            | -                                                  |

| Category                                                                                  | Processor                                                                                                                                   |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Unified Plane processors with Single Voltage Input ( $V_{CC} = 3.3V/VRE$ )                | Pentium <sup>®</sup> processors 75 / 90 / 100 / 120 / 133 / 150 / 166<br>200 MHz, Pentium OverDrive <sup>®</sup> processors 125/150/166 MHz |

| Split-Plane processors with Dual Voltage Input ( $V_{CC2}$ = 2.8V & $V_{CC3}$ = 3.3V/VRE) | Pentium processors with MMX™ technology (166, 200 MHz)                                                                                      |

| Split-Plane processors with Single Voltage Input (V <sub>CC</sub> =3.3V/VRE)              | Future Pentium OverDrive processors with MMX technology 125/150/166/180/20C MHz                                                             |

Figure 5. Unified Plane Current Flow vs. Split Plane Current Flow

The Pentium processor with MMX technology has an internal split power plane which means that the  $V_{CORE}$  and  $V_{I/O}$  power planes, which are internal to the processor package, are electrically isolated. For proper processor operation, the  $V_{CC2}$  pins have to be supplied with 2.8V while the  $V_{CC3}$  pins have to be supplied simultaneously with 3.3V/VRE.

The future Pentium OverDrive processor with MMX technology also has an internal split power plane which means that the  $V_{CORE}$  and  $V_{I/O}$  power planes, internal to the processor package, are also electrically isolated. In order to properly operate this OverDrive processor, the  $V_{CC2}$  pins and  $V_{CC3}$  pins must always be powered simultaneously with 3.3V/VRE.

#### NOTE

The two power planes do not have to be powered by the same voltage source.

#### 3.4. Power Plane Connections and Voltage Regulator Shutdown

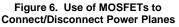

As a flexible motherboard option, the two V<sub>CORE</sub> and V<sub>I/O</sub> power planes have the option of being connected via 0 $\Omega$  resistors, jumpers, a Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 or Pentium OverDrive processor, shorting blocks, or even MOSFETs (see Figure 6). MOSFETs are typically implemented in flexible motherboards with an auto-detect circuit and are an ideal solution for designing in an "automatic" power plane selection device using VCC2DET# as an input.

If a unified-plane processor is plugged into a flexible motherboard with two voltage regulators, one of the voltage regulators may "shut down". The voltage regulator attached to the V<sub>CC2</sub> power pins will always have a much higher current rating than the voltage regulator attached to the V<sub>CC3</sub> power pins because the V<sub>CC2</sub> plane directly powers the processor core. When a Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 or Pentium OverDrive processor is plugged into the system, the current will flow from the  $V_{CC2}$  plane to the  $V_{CC3}$ power plane and shut down the weaker voltage regulator (the weaker voltage regulator will detect the increased current and shut itself down). This is acceptable provided the 8A maximum specification for current flow across a unified plane processor is maintained (see Figure 7). However, when a split plane processor, like the Pentium processor with MMX technology or the future Pentium OverDrive processor with MMX technology, is inserted in the socket, the two regulators are electrically isolated and each continues to function. Also, the designer may design the motherboard such that the two

voltage regulators current share; however, this is an implementation specific option and up to the designer's discretion.

### 3.5. Voltage Supply Implementation Options

There are several voltage supply implementation options to support all the different Pentium family processors on the flexible motherboard. The following options will be discussed in this section:

- 1. Using a 2.8V/3.3V auto-configurable voltage regulator.

- 2. Using an on-board 2.8V regulator as a build option.

- 3. Using the Voltage Regulator Module (VRM). Refer to Appendix A.

## 3.5.1. 2.8V/3.3V AUTO-CONFIGURABLE REGULATOR

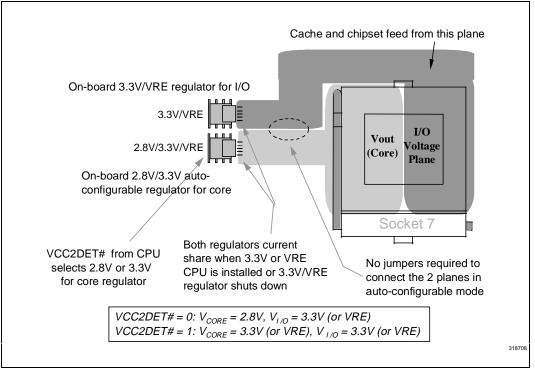

An auto-configurable regulator circuit is an option for supply voltage implementation on the flexible motherboard. This approach allows all Pentium processors 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processors, Pentium processors with MMX technology, and future Pentium OverDrive processors with MMX technology to be easily supported without the need for any jumper/resistor configuration. Figure 8 shows two regulators that work together to form an autoconfigurable voltage solution.

Figure 7. Regulator Shutdown Phenomenon

Figure 8. Auto-Configurable Voltage Regulator Solution

The VCC2DET# pin, defined on the Pentium processor with MMX technology and Socket 7, is used to steer the voltage regulator supplying the processor core to the correct voltage depending on which processor is in the socket. On the Pentium processor with MMX technology, the VCC2DET# pin is always driven low (or grounded). On the Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200, Pentium OverDrive processor and future Pentium OverDrive processor with MMX technology, this pin is an internal no connect; therefore, the VCC2DET# signal trace needs an external pull-up resistor so that the autoconfigurable regulator circuit does not confuse a Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 with a Pentium processor with MMX technology and apply the incorrect input voltages.

When a unified-plane processor (Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 or Pentium OverDrive processor) is plugged into a Socket 7 in the auto-configurable system, the following events take place:

- 1. The VCC2DET# signal is not asserted and the 2.8V/3.3V/VRE voltage regulator toggles to either 3.3V or VRE voltage.

- 2. The  $V_{CORE}$  and  $V_{I/O}$  power planes automatically become electrically shorted ( $V_{CORE} + V_{I/O}$ ) because the processor unifies these two planes internal to the package. This is within processor specification provided that the total sum of electrical current flowing through the processor does not exceed 8A. The 2.8V/3.3V/VRE voltage regulator would have to be sized to accommodate the current draw of any other components attached to the  $V_{CORE} + V_{I/O}$  plane. The 8A of current should be adequate to power the processor, cache and chipset.

- 3. The 3.3/VRE voltage regulator will then shut itself down as it detects the power flow of the much larger 2.8/3.3V/VRE voltage regulator.

When a split-plane, dual voltage processor (Pentium processor with MMX technology) is plugged into a

Socket 7 in the auto-configurable system, the following events take place:

- 1. The VCC2DET# signal is asserted and the 2.8V/3.3V/VRE voltage regulator toggles to 2.8V voltage.

- 2. The  $V_{CORE}$  and  $V_{I/O}$  power planes remain electrically isolated because the processor splits these two planes internal to the package.

- 3. The 3.3V/VRE voltage regulator continues to function and supply the V<sub>I/O</sub> power plane which may include both the processor's V<sub>CC3</sub> pins and any cache and chipset on the V<sub>I/O</sub> plane.

When a split-plane, single voltage processor (future Pentium OverDrive processor with MMX technology) is plugged into a Socket 7 in the autoconfigurable system, the following events take place:

- 1. The VCC2DET# signal is not asserted and the 2.8V/3.3V/VRE voltage regulator toggles to either 3.3V or VRE voltage.

- 2. The  $V_{CORE}$  and  $V_{I/O}$  power planes remain electrically isolated because the processor splits these two planes internal to the package.

- 3. The 3.3V/VRE voltage regulator continues to function and supply the V<sub>I/O</sub> power plane which may include both the processor's V<sub>CC3</sub> pins and any cache and chipset on the V<sub>I/O</sub> plane.

An auto-configurable voltage regulator solution may also be designed-in as a manufacturing stuffing option. In this case, both regulators are designed-in but only one regulator is populated on the board. This regulator needs to provide enough current capability to drive both the core and the I/O voltage planes. With only one regulator in the system, 4-6 $0\Omega$  resistors or external jumpers are also needed to connect both the core and I/O planes at manufacturing time (for split-plane, single voltage processors). When the second regulator and associated circuitry is populated on the board, these jumpers are removed or left out to provide the full auto-configurable capability.

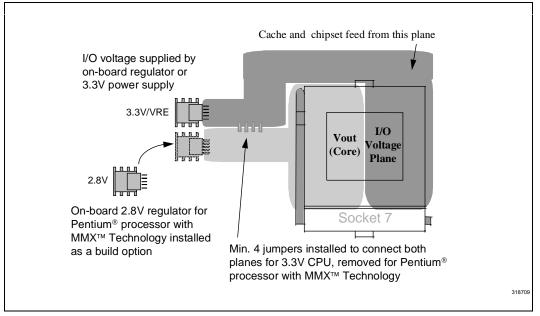

## 3.5.2. 2.8V REGULATOR AS A BUILD OPTION

In this implementation option, the flexible motherboard is configured at manufacturing build or assembly time for either the Pentium processor, 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 (unified-plane, single-voltage processor) or the Pentium processor with MMX technology (split-plane, dual voltage processor).

#### NOTE

All Pentium OverDrive processors and future Pentium OverDrive processors with MMX technology are intended as a consumer upgrade product for unified-plane, single-voltage processors.

As shown in Figure 9, a 2.8V voltage regulator is designed-in and populated when the board is configured to support the Pentium processor with MMX technology.

When the 2.8V voltage regulator is not installed on the board, a Motherboard build option of 4-6 jumpers or  $0\Omega$  resistors (i.e. , #1206, 1/8 watt, surface mount resistors) is recommended to connect the core and I/O voltage planes (in split-plane, single voltage processors and, optionally, unifiedplane, single voltage processors as well) for an approximate current carrying capability of approximately 5-8 amps (dependent upon the quantity of components). However, a unified-plane processor will conduct current between the core and I/O voltage planes without a need for jumpers/resistors. Conversely, when the 2.8V voltage regulator is assembled on the motherboard, the jumper/resistor build option should not be added in order to isolate the two voltage planes.

Figure 9. 2.8V Voltage Regulator Designed as a Build Option

#### 3.5.3. SAFEGUARDING THE PENTIUM<sup>®</sup> PROCESSOR WITH MMX<sup>™</sup> TECHNOLOGY ON THE FLEXIBLE MOTHERBOARD

The Pentium processor with MMX technology core operates at 2.8V. A Socket 7 based flexible motherboard design that is not configured for 2.8V should implement some type of safeguarding mechanism to protect the Pentium processor with MMX technology from getting the wrong voltage. Operating the Pentium processor with MMX technology's core at 3.3V could potentially cause damage to the processor.

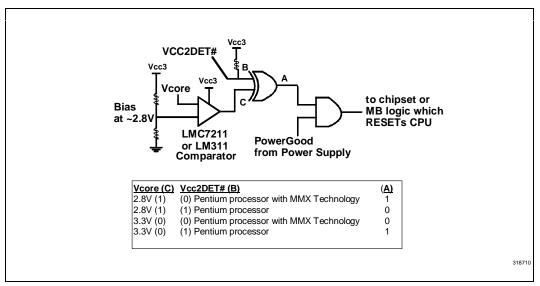

The VCC2DET# pin defined on the Pentium processor with MMX technology and Socket 7 may be used to implement some type of protection circuitry that can be used to either disable the voltage source or prevent the processor from booting if the wrong voltage is detected.

The example circuit shown in Figure 10 may be used to prevent RESET from being generated to the processor if the wrong core voltage is detected. This circuit uses a comparator to compare the core voltage to a reference voltage (~2.8V). If VCC2DET# is grounded (for the Pentium processor with MMX technology) and the core voltage is greater than the reference voltage, the output of the exclusive OR gate will be low which would signal the chipset to not assert RESET. Similarly if VCC2DET# is high (for 3.3V processor), and the core voltage is lower than the reference voltage, the chipset should not be allowed to assert RESET.

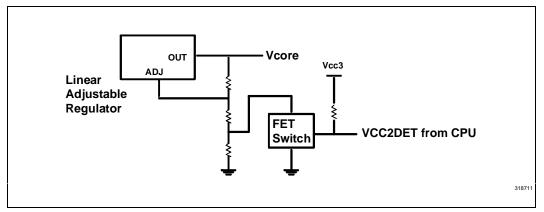

Another example of safeguard implementation is shown in Figure 11. The approach here is to reduce the output voltage of the core regulator (3.3V or VRE) if a low level on VCC2DET# pin is detected. This would be а simpler and cheaper implementation for designs that are using an adjustable voltage regulator, where the output voltage level can be adjusted using a resistor divider. As shown in Figure 9, the value of the resistor divider is altered appropriately (bottom resistor is shorted to ground) when VCC2DET# indicates a zero. This effectively can reduce the output voltage to an appropriate level for the Pentium processor with MMX technology.

Figure 10. External Safeguard Circuit to Prevent Processor from Booting

Figure 11. External Safeguard by Reducing the Output Voltage

### 3.6. Split Power Plane Layout

Implementing a power island on an existing power layer instead of assigning a separate power layer for core  $V_{CC}$  can be a more economical solution. The separate voltage island can be isolated from the other section of the power plane using an air gap. The size of the air gap is determined by analysis of the noise effects and board manufacturing capabilities (typically 10–20 mils). Figure 12 shows a typical layout of the separate voltage islands in the processor area. It shows the core  $V_{\rm CC}$  pins ( $V_{\rm CC2}$ ) clustered on one side of the processor to allow easy layout of the core voltage island. The remaining  $V_{\rm CC}$  pins for the periphery ( $V_{\rm CC3}$ ) are located on the other side and are part of the I/O voltage island (refer to Socket 7 pinout, see Appendix B).

Figure 12. Processor Power Island Layout

The I/O  $V_{CC}$  island should also include other 3.3V components that interface with the processor. A typical configuration would include 3.3V cache SRAM, 3.3V chipset I/O, and processor I/O on the same 3.3V I/O voltage island. This ensures that signals interfacing between the processor and other 3.3V components operate at the same voltage levels. This is also to avoid split plane crossovers for these signals which is recommended for better signal quality and reduced EMI/RFI effects.

When using jumpers or  $0\Omega$  resistors to connect the two power planes (in the case of single voltage processors), the number of jumpers should be chosen so as to provide enough current carrying capability. Insufficient number of jumpers will result in excessive voltage drop and other reliability problems. For the flexible motherboard, a minimum of four (six recommended) zero-ohm, #1206, 1/8 watt, surface mount resistors should be used. Routing of the power source to the voltage islands should also be carefully done to avoid significant voltage drop at the processor and an increase in thermal dissipation in the voltage islands. It is recommended that wide traces be used to prevent excessive voltage drop across the power plane. Also vias and through-holes cutting through the power plane at critical widths should be avoided.

### 3.7. Decoupling

The small size of the processor core voltage island, its isolation from the motherboard power plane, and support of varied voltage requirements make proper decoupling of the island power plane voltage and ground plane essential. Appropriate decoupling capacitors are implemented on the voltage island near the processor to ensure that the processor voltage stays within specified limits during normal and transient conditions. There are two types of decoupling that need to be considered: bulk decoupling and high frequency decoupling.

#### 3.7.1. BULK DECOUPLING

For the processors supported on the flexible motherboard, the power consumption can transition from a low level to a much higher level (or vice versa) very rapidly. This can happen during normal program execution; however, a higher surge of current typically occurs when entering or exiting the Stop Grant state. Another example is when executing a HALT instruction which causes the processor to enter the Auto-HALT Power Down state, or transition from HALT back to the Normal state.

#### NOTE

The Auto-HALT Power Down feature is always enabled even when other power management features are not implemented.

All of these examples may cause abrupt changes in the power consumed by the processor.

As the voltage supply (regulator) cannot respond to a sudden load change instantaneously, bulk storage capacitors with low ESR (Effective Series Resistance) are used to maintain the regulated supply voltage during the interval that falls between the time the current load changes and the point that the regulated power supply output can react to the change in load. In order to reduce the ESR, it may be necessary to place several bulk storage capacitors in parallel.

#### 3.7.2. HIGH FREQUENCY DECOUPLING

High frequency decoupling may be required to provide a short, low impedance path to high frequency components such as high current spikes in order to minimize noise. The processor driving its large address and data buses at high frequencies can cause transient power surges, particularly when driving large capacitive loads.

For high frequency decoupling, low inductance capacitors and interconnects are recommended for best high speed electrical performance. Inductance can be reduced by shortening circuit board traces between the processor and decoupling capacitors as much as possible. Surface mount capacitors are preferable, as capacitors with long leads add inductance to the circuit. The capacitors should be of RF grade, with low ESR and low inductance to reduce spikes.

#### 3.7.3. DECOUPLING RECOMMENDATIONS

Table 5 shows the processor decoupling recommendations for the flexible motherboard for both the processor core and I/O voltage islands. This is based on simulation and testing of the voltage transients from the processor and the effects of motherboard decoupling.

Spice modeling (modeling worst case current transients including the processor package inductance, capacitance, routing, decoupling, voltage regulator output inductance, etc.) should be used to estimate the amount of decoupling capacitance for the processor voltage island.

It is highly recommended that before committing to any change from the decoupling capacitor recommendation, the solution be simulated for the variety of variables in components, temperature and lifetime degradation.

| · · · · · · · · · · · · · · · · · · ·          |          |        |                         |                         |                         |  |

|------------------------------------------------|----------|--------|-------------------------|-------------------------|-------------------------|--|

|                                                | Quantity | Value  | ESR                     | ESL                     | Туре                    |  |

| Processor Core<br>Voltage Island               | 4        | 100 µF | 25 mOhms <sup>(1)</sup> | 0.45 nH <sup>(3)</sup>  | Tantalum                |  |

|                                                | 25       | 1 µF   | 0.6 mOhms (2)           | 0.084 nH <sup>(4)</sup> | X7R dielectric, ceramic |  |

| Processor I/O<br>Voltage Island <sup>(5)</sup> | 12       | 0.1 µF |                         |                         | 603 Туре                |  |

Table 5. Decoupling Recommendations for Processor Core and I/O Voltage Islands

#### NOTES:

- 1. ESR per capacitor should be less than 100 mOhms.

- 2. ESR per capacitor should be less than 15 mOhms.

- 3. ESL per capacitor (including 0.7 nH Via inductance per capacitor) should be less than 2.7 nH.

- 4. ESL per capacitor (including 0.7 nH Via inductance per capacitor) should be less than 2.1 nH.

- 5. This does not include decoupling for components other than the processor in the 3.3V I/O voltage island.

For bulk decoupling, tantalum capacitors are recommended over electrolytic capacitors. In general, electrolytic capacitors degrade at a much faster rate, are not as accurate, and are not as stable over temperature as tantalum capacitors.

For high speed decoupling in the processor core voltage island, low inductance, 1µF capacitors of X7R dielectric are recommended. These capacitors not only decouple the processor core for high frequency noise but also control the voltage during very fast transients (less than 100 ns.) Figure 13 shows that ceramic capacitors of X7R (or X7S) exhibit dielectric relatively stable capacitor characteristics over temperature compared to capacitors of Z5U or Y5V type dielectric. For example, at a typical operating temperature of 45°C, the Y5V dielectric can lose 45% of the initial rated capacitance.

Measurement techniques to ensure that motherboard designs are within  $V_{CC}$  noise and transients specification are discussed in the following application notes (see Appendix E for order information).

- Voltage Guidelines for Pentium<sup>®</sup> Processors with MMX<sup>TM</sup> Technology Processors

- Implementation Guidelines for Pentium® Processors with VRE Specifications

#### 3.7.4. PLACEMENT OF DECOUPLING CAPACITORS

Figure 14 shows an example of how the recommended processor decoupling capacitors (Table 5) should be placed inside the respective voltage islands on the flexible motherboard. The bulk capacitors should be placed near the processor inside the voltage island to ensure that the supply voltage stays within specified limits during changes in the supply current during operation. The 1 µF, X7R capacitors should be evenly distributed inside the processor core voltage island inside and around the processor footprint. Figure 12 also shows the twelve 0.1 µF capacitors evenly placed around the processor, close to the processor V<sub>CC3</sub> pins inside the processor I/O voltage island.

In this example, all the capacitors were placed on one side of the board. If components are assembled on both sides of the board then these capacitors can be distributed between the top and bottom sides. If done this way, vias connecting the capacitor pads to the power and ground layer can be shared between the capacitors on the top and bottom sides. This can help reduce the total overall capacitor inductance.

Figure 13. Typical Capacitor Characteristics

Figure 14. Example of Processor Decoupling Capacitor Placement

The traces connecting the vias to the capacitor pads should be kept as short as possible. In cases where it is difficult to reduce the length of the circuit board trace, the trace should be made wider so as to reduce the trace inductance.

### 3.8. Signal Routing Guidelines

As the power plane on the flexible motherboard is split into separate voltage islands, signal routing should be done in such a way so as to minimize crossovers between voltage islands for high speed signals. Signal routing between the voltage islands and the system power plane should be limited to only those signals that absolutely need to cross the gap between the island and the power plane. This is to avoid possible signal degradation from impedance discontinuity effects. Significant levels of EMI could be generated by electromagnetic radiation from high speed traces (such as clocks,

26

strobes, data lines, and low address lines) when their return path is interrupted. On a multi-layer board this return path is on the power or ground plane that is adjacent to the signal layer directly under the signal trace. If this trace is routed over a break in the return path, the return current has to find another longer path in order to maintain current continuity. The increased area generated by the signal trace and the length of this extended return path can lead to increased radiation levels from this signal trace.

The following guidelines should be followed when routing high speed signals on the flexible motherboard:

Clocks and Strobes: These signals should not be routed over breaks in the reference plane return path. Use of vias to connect between signal planes should be minimized, and the signal planes should be within 8 mils of the reference plane. Clock

signals should be routed on the layer that is adjacent to the ground layer.

Data Bus and Low Address Lines: These signals can be routed on any signal layer. However, it is desired that the number of traces crossing over splits in the return path plane be minimized and ideally kept to zero. Among this group, signals that do need to cross the gap should be routed on the signal layer near the ground plane to minimize radiated emissions (using a via, a trace may be taken down to the layer that is referenced to the ground plane). On a four layer board, the signal layer with the least potential for signal crossovers should be placed adjacent to the power plane. Capacitive decoupling across the split planes can also be used near signal crossovers (for those which cannot be avoided) to help reduce the magnitude of EMI radiation. Within an inch of the signal crossover violation, a 0.1 µF ceramic capacitor should be placed across the power plane gap, using one capacitor for every three trace violations (provided they are all within the one inch limit).

## 3.9. Thermal and Physical Space Considerations

The thermal design of a system using the flexible motherboard should be based on the worst case power dissipation and related thermal requirements for the processors that are supported.

The Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 and Pentium processor with MMX technology use OEM specified heatsinks which are dependent upon the entire system cooling solution. The maximum case temperature for these processors should not exceed 70°C to ensure proper operation. Heatsinks also may need a certain airflow in order to maintain their specified temperature. For detailed information refer to the respective datasheet for these processors (see Appendix E). In addition, detailed discussion of thermal design issues for the Pentium processor is covered in *Pentium® Processor Thermal Design Guidelines* (see Appendix E).

The Pentium OverDrive processors and future Pentium OverDrive processors with MMX technology are shipped with integrated fan/heatsink cooling solutions. Although these fan/heatsinks remove the heat from the package, the system should be able to dissipate the added heat to the system. From Table 1, the future Pentium OverDrive processor with MMX technology dissipates the most power at 200 MHz. The system provides sufficient airflow to dissipate this power from the system and prevent the temperature of the air entering the fan/heatsink from exceeding 45°C. When the  $T_A$  (max)  $\leq$  45°C specification is met ( $T_A$ = ambient temperature), the Pentium OverDrive processor and future Pentium OverDrive processor with MMX technology fan/heatsink will keep  $T_C$ (case temperature) within the specified range, provided airflow through the fan/heatsink is unimpeded. The ambient temperature should be measured approximately 0.3" above the top of the fan/heatsink.

Figure 15 illustrates the thermal and physical space specifications for the Pentium OverDrive processor and the future Pentium OverDrive processor with MMX technology.

Physical space specifications for the future Pentium OverDrive processor with MMX technology are summarized as follows:

- 1.75" vertical clearance above the surface (opposite pin side) of Socket 7 when installed.

- 0.2" clearance around all four sides of the package.

- Space greater than specified above for end-user installation.

## 3.9.1. VOLTAGE REGULATOR THERMAL DESIGN CONSIDERATIONS

Voltage regulators are typically shipped with passive heatsinks for heat dissipation and may require adequate airflow. For a 45 to  $50^{\circ}$ C ambient temperature, voltage regulators typically call for an airflow of 200 LFM to ensure proper cooling. The airflow is parallel to the surface of the voltage regulator to ensure that the heatsink receives adequate airflow. Refer to your voltage regulator datasheet for actual specifications.

## 3.9.2. DESKTOP SYSTEM THERMAL DESIGN CONSIDERATIONS

To avoid localized heating at the processor, a clear air path and adequate venting is provided to prevent hot spots from occurring. A typical solution to this thermal problem is to add an auxiliary fan to the front vents of the chassis, directing airflow across the processor. While this solution would appear to be fairly simple, the addition of a second fan can actually cause the problem to intensify. Unless the front vents are of sufficient size, and placement of the fan is carefully considered, the auxiliary fan can actually cause the air heated by the processor and other components to be recirculated within the system rather than expelled out the back of the chassis. This heated air can easily raise the temperature around the processor beyond the temperature specifications for the components in the system.

Figure 15. Thermal and Physical Space Requirements for the Pentium<sup>®</sup> OverDrive<sup>®</sup> Processor with MMX<sup>™</sup> Technology

When adding an auxiliary fan to the system, the size of the chassis vents deserves special consideration. The fan is most effective when all of the air pushed through the fan blades comes from outside the chassis. If the vents are too small or inadequate for the fan velocity, gaps between the fan and chassis will cause air from inside the system to be drawn through the fan, causing re-circulation of heated air. The position of the fan is also critical. The highest air flow is from the blades and not from the center of the fan. Care should be taken not to block the blades with frame supports.

For details on Baby AT style chassis design suggestions, refer to the application note, *Pentium® Processor Chassis Design Suggestions* available on CD-ROM (See Appendix E).

#### 3.10. BIOS/Software Considerations

As the flexible motherboard can accommodate a variety of processors, the BIOS is designed such

that it can support all the different processors on the flexible motherboard. The BIOS code should use the CPUID instruction to identify the processor's CPUID signature (see Section 2.3.).

Other considerations for BIOS/software on the flexible motherboard include the following:

- Processor test code should be independent of model specific registers (MSR). Various processors have different caches, test registers, and core architecture; e.g. the Pentium processor with MMX technology's cache size and associativity is different from the Pentium processor 75 / 90 / 100 / 120 / 133 / 150 / 166 / 200 resulting in differences in cache test registers.

- Since processors of various core frequencies are supported on the flexible motherboard, BIOS code should not contain any software timing

loops and should be independent of the prefetch algorithm.

### 3.11. Dual Processor Design Considerations

The Pentium processor family flexible motherboard may also be designed as one planar board to support uni-processor (UP) and dual-processor (DP) modes. This provides the flexibility of using the same motherboard populated with either one socket (for UP system) or two sockets (for DP system.) Figure 16 shows the layout for a split plane flexible motherboard designed with two sockets.

Figure 16. Layout of a DP Flexible Motherboard

The following needs to be considered when designing a split plane flexible motherboard with two sockets:

- The power islands should be laid out such that the processor cores share one common island and the I/O share another island. This minimizes the number of islands resulting in better signal quality and reduced EMI effects.

- Socket 7 should only be used at the primary socket location. The secondary socket footprint

should not be designed with the Socket 7 footprint.

#### NOTE