# AMD-K6<sup>™</sup>

# **MMX<sup>™</sup> Enhanced Processor**

**Revision Guide**

Publication # 21266 Issue Date: July 1997 Amendment/0

Rev: D

© 1997 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD's Terms and Conditions of Sale for such product.

#### **Trademarks**

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

RISC86 is a registered trademark, and K86, AMD-K5, AMD-K6, and the AMD-K6 logo are trademarks of Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks, and Windows NT is a trademark of Microsoft Corporation.

Netware is a registered trademark of Novell, Inc.

MMX is a trademark of the Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# AMD-K6™ MMX™ Enhanced Processor Revision Guide

The purpose of the *AMD-K6<sup>TM</sup> MMX<sup>TM</sup> Enhanced Processor Revision Guide* is to communicate updated product information on the AMD-K6 processor to designers of computer systems and software developers. This guide consists of four major sections:

- **Product Marking Identification:** This section provides product types, product revisions, OPNs (Ordering Part Numbers), and product marking information.

- **Product Errata:** This section provides a detailed description of product errata, including potential effects on system operation and suggested workarounds. An erratum is defined as a deviation from the product's specification.

- **Specification Changes/Clarifications:** This section provides changes, additions, and clarifications to product specifications.

- **Technical and Documentation Support:** This section provides a listing of available technical support resources. It also lists corrections, modifications, and clarifications to listed documents.

#### **Revision Guide Policy**

At times, AMD identifies deviations or changes to the specification of the AMD-K6 MMX enhanced processor. These are documented in the *AMD-K6 MMX Enhanced Processor Revision Guide* as errata or specification changes/clarifications and are available to anyone who requests the information. The descriptions are written to assist system and software designers in using the AMD-K6 processor. In addition, any corrections to AMD's published documentation on the AMD-K6 processor are included. The errata and specification changes are the result of extensive testing and validation that is done for all AMD products. AMD works closely with system and software designers to ensure the appropriate workarounds or changes are implemented to avoid impact to PC users.

The *AMD-K6 MMX Enhanced Processor Revision Guide* is made publicly available to all who are interested during the third week of each month. All issues that have been resolved and communicated to AMD's customers are included in this release.

# 1 Product Marking Identification

Ceramic Pin Grid Array (CPGA)

(Packages Not Drawn to Scale)

xxxpvt = OPN, where:

- xxx = Operating Frequency

- p = Package Type

- A = 321-pin PGA

- v = Operating Voltage

- N = 3.1-3.3V Core/3.135-3.6V I/O

- L = 2.755-3.045V Core/3.135-3.6V I/O

- t = Case Temperature

- R = 70°C

v.vV = Core Voltage, where:

- 2.9V = 2.9V Component

- 3.2V = 3.2V Component

R AAAAAA = Revision, where:

- R = Revision

- B = Revision B

- C = Revision C

- etc.

- AAAAAA = Internally-Defined

### 2 Product Errata

This section documents AMD-K6 processor product errata. The errata are divided into categories to assist referencing particular errata. A unique tracking number for each erratum has been assigned within this document for user convenience in tracking the errata within specific revision levels. Table 1 cross-references the revisions of the processor to each erratum. An "X" indicates that the erratum applies to the stepping. The absence of an "X" indicates that the erratum does not apply to the stepping. Shading within the table indicates an addition or modification from the previous release of this document.

Table 1. Cross-Reference of Product Revision to Errata

| Erratum<br>Number         | Description                                                                           | Rev<br>B |  |  |

|---------------------------|---------------------------------------------------------------------------------------|----------|--|--|

| Test and Debug            |                                                                                       |          |  |  |

| 2.1.1                     | Built-In Self-Test (BIST)                                                             | Х        |  |  |

| System Bus                |                                                                                       |          |  |  |

| 2.2.1                     | Drive Strength Selection                                                              | Χ        |  |  |

| 2.2.2                     | HLDA Assertion Delayed by One Clock                                                   | Χ        |  |  |

| Interrupts and Exceptions |                                                                                       |          |  |  |

| 2.3.1                     | Interruption of REP MOVS Instruction                                                  | Χ        |  |  |

| Instructions              |                                                                                       |          |  |  |

| 2.4.1                     | LGDT Instruction                                                                      | Χ        |  |  |

| DC Specifications         |                                                                                       |          |  |  |

| 2.5.1                     | Input Leakage Current Bias with Pullup (I <sub>IL</sub> )                             | Χ        |  |  |

| Self-Modifying Code       |                                                                                       |          |  |  |

| 2.6.1                     | Misaligned Write to Displacement of Transfer Control Instruction                      | Χ        |  |  |

| 2.6.2                     | Re-execution of Instructions Due to Self-Modifying Code                               | Χ        |  |  |

|                           | Shading indicates additions or modifications from the previous release of this docume |          |  |  |

#### 2.1 Test and Debug

#### 2.1.1 Built-In Self-Test (BIST)

**Products Affected.** B stepping

*Normal Specified Operation.* Following the falling transition of RESET, the processor unconditionally runs its BIST.

Non-conformance. BIST is not supported.

Potential Effect on System. The L1 caches are not tested after RESET.

Suggested Workaround. None.

Resolution Status. This erratum will be corrected in a future stepping of the AMD-K6 processor.

#### 2.2 System Bus

#### 2.2.1 Drive Strength Selection

**Products Affected.** B stepping

Normal Specified Operation. The processor samples the BRDYC# input during the falling transition of RESET to configure the drive strength of A[20:3], ADS#, HITM#, and W/R#. If BRDYC# is sampled asserted during the fall of RESET, these particular outputs are configured using a higher drive strength than the standard drive strength. If BRDYC# is sampled negated during the fall of RESET, the standard drive strength is selected for these particular outputs.

*Non-conformance.* If BRDYC# is sampled asserted during the fall of RESET, all output drivers are configured using the higher drive strength.

*Potential Effect on System.* Using the higher strength drive configuration can affect signal quality by resulting in additional overshoot or undershoot.

*Suggested Workaround.* Use the standard drive configuration. With few exceptions, most board designs require the standard drive configuration.

Resolution Status. This erratum will be corrected in a future stepping of the AMD-K6 processor.

#### 2.2.2 HLDA Assertion Delayed by One Clock

Products Affected. B stepping

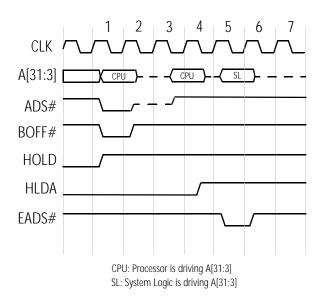

*Normal Specified Operation.* If BOFF# and HOLD are sampled asserted on the same clock edge that negates ADS#, the processor asserts HLDA one clock edge after HOLD is sampled asserted.

*Non-conformance.* If BOFF# and HOLD are sampled asserted on the same clock edge that negates ADS#, the processor asserts HLDA two clock edges after HOLD is sampled asserted.

Potential Effect on System. There are three potential effects of this erratum to consider:

- If the system logic asserts BOFF# for a duration of one clock, anticipates the assertion of HLDA in clock 3 (see Figure 1)—which is the normal specified operation—and drives the address bus and EADS# for an inquire cycle in clock 3, then the processor will not sample EADS# asserted. In addition, address bus contention will occur in clock 3.

- If the system logic asserts BOFF# for a duration of two clocks, anticipates the assertion of HLDA in clock 3, and drives the address bus and EADS# for an inquire cycle in clock 3, then the processor will not sample EADS# asserted. (No address bus contention occurs in this case.)

- If the system logic asserts BOFF# for a duration of one clock, anticipates the assertion of HLDA in clock 3, and drives the address bus and EADS# for an inquire cycle in clock 4, then address bus contention may occur in clock 4. (The processor will sample EADS# asserted in this case.)

If the processor does not sample EADS# asserted during an inquire cycle, cache/memory incoherency will occur. Address bus contention can affect the reliability of the processor and the system logic.

*Suggested Workaround.* The system logic must sample the assertion of HLDA before asserting EADS# and driving the address bus for an inquire cycle—as shown in clock 5 of Figure 1.

Resolution Status. This erratum will be corrected in a future stepping of the AMD-K6 processor.

Figure 1. AMD-K6™ Processor Assertion of HLDA Due to Simultaneous BOFF#/HOLD Assertion

#### 2.3 Interrupts and Exceptions

#### 2.3.1 Interruption of REP MOVS Instruction

Products Affected. B stepping

*Normal Specified Operation.* A move string instruction (MOVS) with a REP prefix can be interrupted before the start of its execution by the occurrence of a hardware interrupt—such as NMI, INTR, STPCLK#, or SMI#.

Non-conformance. If a REP MOVS instruction is interrupted after it is decoded, but before the execution of the first iteration of the instruction—specifically, during the initial check for ECX equal to 0—and all of the conditions itemized below are true, then the incorrect address size and/or operand segment register is used for the one iteration of the REP MOVS instruction that is executed before the interrupt is recognized. Following is a list of the conditions that must apply to the REP MOVS instruction for this erratum to occur:

- An address size override prefix is used

- The initial loop count loaded in ECX equals 6

- The interrupt is received internally on exactly one specific clock just as the processor is checking if the initial loop count in ECX equals 0

- The next few instructions—between one and four—that immediately follow the REP MOVS instruction reside in the processor's instruction cache, and one of them is a vector-decoded instruction (the complex x86 instructions are typically vector decoded)

- The effective address size or operand segment register of the vector-decoded instruction differs from that of the REP MOVS instruction

- Certain other relative internal pipeline timing conditions must occur

Potential Effect on System. The effect on software is unpredictable.

Suggested Workaround. None.

*Resolution Status.* This erratum is corrected in a future stepping of the AMD-K6 processor.

#### 2.4 Instructions

#### 2.4.1 LGDT Instruction

Products Affected. B stepping

*Normal Specified Operation.* While reading the memory operand of the Load Global Descriptor Table Register (LGDT) instruction, a general protection fault, a stack segment fault, or a page fault can occur.

*Non-conformance.* If only the limit value portion of the memory operand of the LGDT instruction faults—that is, the base address portion of the memory operand must not fault for this erratum to occur—then one of two possible scenarios can occur:

- If the assertion of SMI# is recognized any time after the execution of the LGDT instruction, but before the next successfully-executed LGDT instruction, then the base address portion of the GDTR that is stored in the SMM state-save area is incorrect. During the execution of the RSM instruction, the GDTR that is restored will be corrupted.

- If an SGDT instruction is executed after the LGDT instruction—without an intervening successfully-executed LGDT instruction—then the SGDT instruction will store an incorrect base address.

Potential Effect on System. Either of these scenarios can lead to unpredictable operating system behavior.

Suggested Workaround. None. However, the LGDT instruction is privileged and only executed by the operating system. Operating systems typically either avoid faults on the LGDT instruction, or they align the memory operand of the LGDT instruction such that if a fault were to occur, both the base address and the limit value will fault.

This erratum has not been observed to adversely affect a system. It was detected by design inspection.

Resolution Status. This erratum will be corrected in a future stepping of the AMD-K6 processor.

#### 2.5 DC Specifications

#### 2.5.1 Input Leakage Current Bias with Pullup (III)

Products Affected. B stepping

Normal Specified Operation. The Input Leakage Current Bias With Pullup specification is -400 µA.

Non-conformance. The Input Leakage Current Bias With Pullup is -450 µA.

Potential Effect on System. None.

Suggested Workaround. None.

Resolution Status. This erratum will be corrected in a future stepping of the AMD-K6 processor.

#### 2.6 Self-Modifying Code

#### 2.6.1 Misaligned Write to Displacement of Transfer Control Instruction

Products Affected. B stepping

*Normal Specified Operation.* If an instruction causes a memory write to the displacement part of a transfer control instruction, and the transfer control instruction is subsequently executed, the processor ensures that the transfer control uses the modified displacement.

#### Non-conformance. If:

- The target of the transfer control instruction is sequentially fetched and stored in the processor's L1 cache

- The transfer control instruction is speculatively executed causing the processor to initiate the allocation of an entry in the Branch Target Cache (BTC)

- A data read of the target of the transfer control instruction occurs (this has the effect of invalidating the previously-fetched target of the transfer control instruction that resides in the L1 cache, which in turn delays the completion of the BTC allocation)

- A misaligned memory write to the displacement part of the transfer control instruction occurs (self-modifying code)

- The processor fetches the original target of the transfer control instruction in order to complete the pending BTC allocation

- The processor refetches the transfer control instruction with the new displacement as a result of detecting the self-modifying code sequence

- Certain other relative internal pipeline timing conditions must occur

then: the processor erroneously hits the BTC and executes the instruction at the original displacement of the transfer control rather than the instruction at the modified displacement.

*Potential Effect on System.* This erratum can lead to unpredictable system behavior.

Suggested Workaround. None.

Resolution Status. This erratum will be corrected in a future stepping of the AMD-K6 processor.

#### 2.6.2 Re-execution of Instructions Due to Self-Modifying Code

#### Products Affected. B stepping

*Normal Specified Operation.* If the processor detects a potential self-modifying code condition, the processor performs specific internal actions to ensure that instruction execution occurs in the correct manner.

#### Non-conformance. If:

- The target of a transfer control instruction is fetched and loaded into the processor's Branch Target Cache (BTC)

- This transfer control instruction is speculatively executed and hits in the BTC

- An instruction (Instruction "A") is executed that causes the processor to detect a potential self-modifying code condition relative to the transfer control target that resides in the BTC

- Instruction "A" is followed by a register-modifying instruction(s) in the form of:

- A long-decoded instruction, or;

- One or two short-decoded instructions

- The transfer control instruction that was speculatively executed follows the register-modifying instruction(s) within approximately 1–9 instructions

- Certain other relative internal pipeline timing conditions must occur

then: the long-decoded instruction, or the short-decoded instruction(s), is executed twice.

Potential Effect on System. If software is not affected by the re-execution of the register-modifying instruction(s)—for instance, loading immediate data into a general purpose register—then this erratum has no effect on the system. However, if any of the instructions that are re-executed change the state of the system from the state that would be achieved by the normal specified operation—for instance, incrementing a register by one—then this erratum can lead to unpredictable system behavior.

Suggested Workaround. None.

Resolution Status. This erratum will be corrected in a future stepping of the AMD-K6 processor.

## **3** Specification Changes/Clarifications

This section documents AMD-K6 processor specification changes and clarifications. The changes/clarifications are divided into categories to assist referencing particular changes. A unique tracking number for each change/clarification has been assigned within this document for user convenience in tracking the specification change/clarification within specific revision levels. Table 2 cross-references the revisions of the processor to each specification change/clarification. An "X" indicates that the specification change/clarification applies to the stepping. The absence of an "X" indicates the specification change/clarification does not apply to the stepping.

Table 2. Cross-Reference of Product Revision to Specification Change/Clarification

| Change<br>Number          | Description                                                                             | Rev<br>B | Future<br>Rev |  |

|---------------------------|-----------------------------------------------------------------------------------------|----------|---------------|--|

| Interrupts and Exceptions |                                                                                         |          |               |  |

| 3.1.1                     | Recognition of External Hardware Interrupts During I/O Read Cycle                       |          | Х             |  |

|                           | Shading indicates additions or modifications from the previous release of this document |          |               |  |

#### 3.1 Interrupts and Exceptions

#### 3.1.1 Recognition of External Hardware Interrupts During I/O Read Cycle

New Specification Applies to: A future stepping.

*Previous Operation.* For I/O Reads, the AMD-K6 processor waits for preceding instructions to complete before executing the I/O Read instruction. However, there is no serialization for succeeding instructions. This means that succeeding instructions can be executed in parallel with the I/O Read. As a result, external interrupts may not be recognized and serviced before succeeding instructions are completed.

New Operation. For I/O Reads, the AMD-K6 processor waits for preceding instructions to complete before executing the I/O Read instruction and it serializes succeeding instructions. This means that the I/O Read instruction completes before any succeeding instructions are executed. Such serialization allows for external interrupts, asserted during the I/O cycle, to be recognized and serviced before any dependent instructions are executed.

*Implication.* The previous and new operation has no implication for software and hardware that are designed to the Socket 7 specification, which states that IN instructions are not fully serialized.

## 4 Technical and Documentation Support

#### 4.1 **Documentation Support**

The following documents provide additional information regarding the operation of the AMD-K6 processor:

- AMD-K6<sup>TM</sup> MMX<sup>TM</sup> Enhanced Processor Data Sheet (order# 20695)

- AMD-K6<sup>™</sup> MMX<sup>™</sup> Enhanced Processor Multimedia Technology (order# 20726)

- AMD K86™ Family BIOS and Software Tools Developers Guide (order# 21062)

- AMD K86™ Family BIOS Design Application Note (order# 21329)

- AMD Processor Recognition Application Note (order# 20734)

- Implementation of Write Allocate in the K86 Processors (order# 21326)

- AMD-K6<sup>™</sup> MMX<sup>™</sup> Enhanced Processor Thermal Solution Design Application Note (order# 21085)

- AMD-K6<sup>™</sup> MMX<sup>™</sup> Enhanced Processor Power Supply Design Application Note (order# 21103)

- AMD-K6<sup>TM</sup> MMX<sup>TM</sup> Enhanced Processor I/O Model Application Note (order# 21084)

For the latest updates, refer to www.amd.com and download the appropriate files.