# IBM @server p5 590 and p5 595 System Handbook

ibm.com/redbooks

# IBM

International Technical Support Organization

| IBM @server p5 590 and p5 595 System Handbook February 2005 **Note:** Before using this information and the product it supports, read the information in "Notices" on page xv.

#### First Edition (February 2005)

This edition applies to the IBM @server p5 9119 Models 590 and 595.

© Copyright International Business Machines Corporation 2005. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

# **Contents**

| Figures                                  | ix    |

|------------------------------------------|-------|

| Tables                                   | xii   |

| <b>Notices</b>                           |       |

| Preface                                  | . xvi |

| The team that wrote this redbook         |       |

| Become a published author                | xix   |

| Comments welcome                         | xix   |

| Chapter 1. System overview               |       |

| 1.1 Introduction                         |       |

| 1.2 What's new                           |       |

| 1.3 General overview and characteristics |       |

| 1.3.1 Microprocessor technology          |       |

| 1.3.2 Memory subsystem                   |       |

| 1.3.3 I/O subsystem                      |       |

| 1.3.4 Virtualization                     |       |

| <ul><li>1.4 Features summary</li></ul>   |       |

| 1.5.1 AIX 5L                             |       |

| 1.5.2 Linux                              |       |

| 1.9.2 Liliux                             | 14    |

| Chapter 2. Hardware architecture         | 17    |

| 2.1 Server overview                      | 18    |

| 2.2 The POWER5 microprocessor            | 18    |

| 2.2.1 Simultaneous multi-threading       | 20    |

| 2.2.2 Dynamic power management           | 21    |

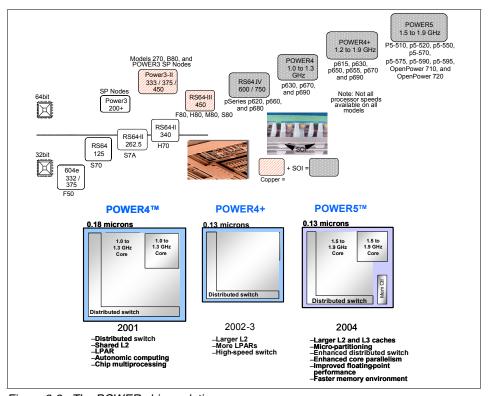

| 2.2.3 The POWER chip evolution           | 21    |

| 2.2.4 CMOS, copper, and SOI technology   | 24    |

| 2.2.5 Processor books                    |       |

| 2.2.6 Processor clock rate               |       |

| 2.3 Memory subsystem                     |       |

| 2.3.1 Memory cards                       |       |

| 2.3.2 Memory placement rules             |       |

| 2.4 Central electronics complex          |       |

| 2.4.1 CEC backplane                      | 32    |

| 2.5 System flash memory configuration                            | . 34 |

|------------------------------------------------------------------|------|

| 2.6 Vital product data and system smart chips                    | . 35 |

| 2.7 I/O drawer                                                   | . 35 |

| 2.7.1 EEH adapters and partitioning                              | . 36 |

| 2.7.2 I/O drawer attachment                                      | . 37 |

| 2.7.3 Full-drawer cabling                                        | . 38 |

| 2.7.4 Half-drawer cabling                                        | . 40 |

| 2.7.5 Blind-swap cassette                                        | . 41 |

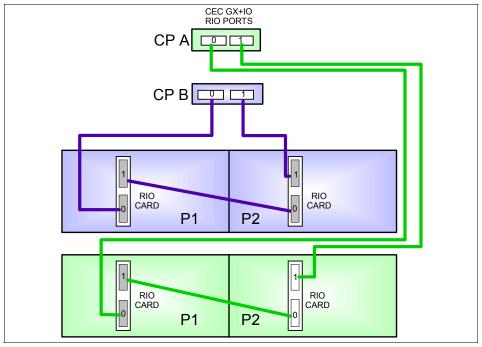

| 2.7.6 Logical view of a RIO-2 drawer                             |      |

| 2.7.7 I/O drawer RAS                                             | . 44 |

| 2.7.8 Supported I/O adapters in p5-595 and p5-590                | . 45 |

| 2.7.9 Expansion units 5791, 5794, and 7040-61D                   | . 48 |

| 2.7.10 Configuration of I/O drawer ID and serial number          |      |

| •                                                                |      |

| Chapter 3. POWER5 virtualization capabilities                    |      |

| 3.1 p5 virtualization features                                   |      |

| 3.2 Micro-Partitioning                                           |      |

| 3.2.1 Shared processor partitions                                |      |

| 3.2.2 Types of shared processor partitions                       |      |

| 3.2.3 Typical usage of Micro-Partitioning technology             |      |

| 3.2.4 Limitations and considerations                             |      |

| 3.3 Virtual Ethernet                                             |      |

| 3.3.1 Virtual LAN                                                |      |

| 3.3.2 Virtual Ethernet connections                               |      |

| 3.3.3 Dynamic partitioning for virtual Ethernet devices          |      |

| 3.3.4 Limitations and considerations                             |      |

| 3.4 Shared Ethernet Adapter                                      |      |

| 3.4.1 Connecting a virtual Ethernet to external networks         |      |

| 3.4.2 Using Link Aggregation (EtherChannel) to external networks |      |

| 3.4.3 Limitations and considerations                             |      |

| 3.5 Virtual I/O Server                                           |      |

| 3.6 Virtual SCSI                                                 |      |

| 3.6.1 Limitations and considerations                             | . 81 |

| Observed A. Osmarika an Damand                                   | 00   |

| Chapter 4. Capacity on Demand                                    |      |

| 4.1 Capacity on Demand overview                                  |      |

| 4.2 What's new in Capacity on Demand?                            |      |

| 4.3 Preparing for Capacity on Demand                             |      |

| 4.3.1 Step 1. Plan for future growth with inactive resources     |      |

| 4.3.2 Step 2. Choose the amount and desired level of activation  |      |

| 4.4 Types of Capacity on Demand                                  |      |

| 4.5 Capacity BackUp                                              |      |

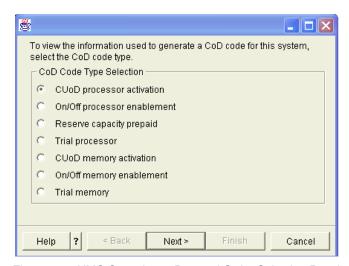

| 4.6 Capacity on Demand activation procedure                      | . 89 |

| 4.7 Using Capacity on Demand                                    | 90   |

|-----------------------------------------------------------------|------|

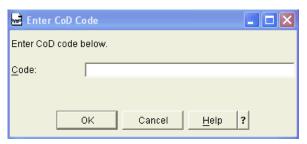

| 4.7.1 Using Capacity Upgrade on Demand                          | 90   |

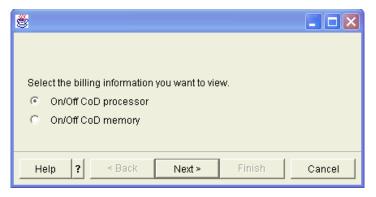

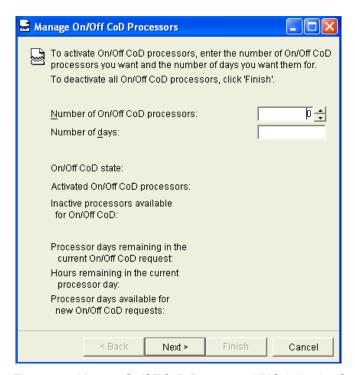

| 4.7.2 Using On/Off Capacity On Demand                           | 91   |

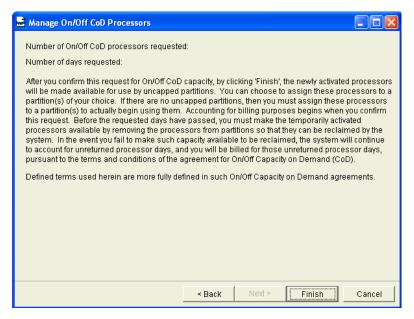

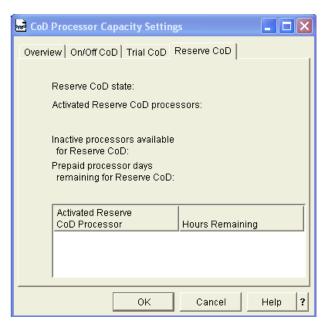

| 4.7.3 Using Reserve Capacity on Demand                          | 96   |

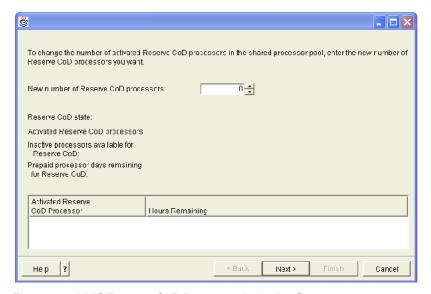

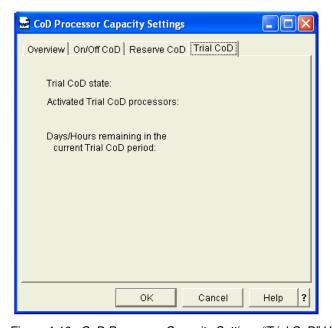

| 4.7.4 Using Trial Capacity on Demand                            | 97   |

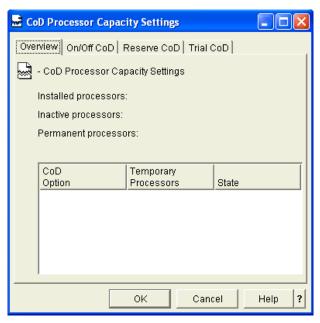

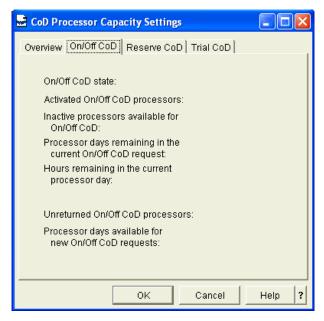

| 4.8 HMC Capacity on Demand menus                                | 98   |

| 4.8.1 HMC command line functions                                | 102  |

| 4.9 Capacity on Demand configuration rules                      | 102  |

| 4.9.1 Processor capacity Upgrade on Demand configuration rules  | 102  |

| 4.9.2 Memory capacity Upgrade on Demand configuration rules     |      |

| 4.9.3 Trial Capacity on Demand configuration rules              |      |

| 4.9.4 Dynamic processor sparing                                 |      |

| 4.10 Software licensing considerations                          |      |

| 4.10.1 License entitlements for permanent processor activations |      |

| 4.10.2 License entitlements for temporary processor activations |      |

| 4.11 Capacity on Demand feature codes                           | 107  |

| Chapter 5. Configuration tools and rules                        | 100  |

| 5.1 Configuration tools                                         |      |

| 5.1.1 IBM Configurator for e-business                           |      |

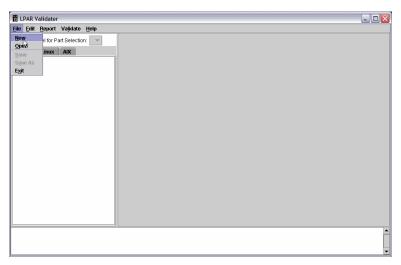

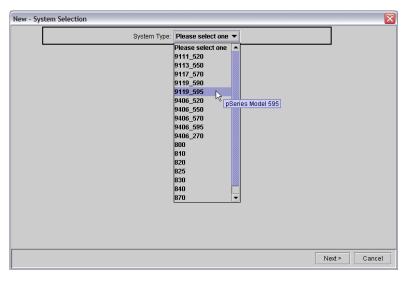

| 5.1.2 LPAR Validation Tool                                      |      |

| 5.2 Configuration rules for p5-590 and p5-595                   |      |

| 5.2.1 Minimum configuration for the p5-590 and p5-595           |      |

| 5.2.2 LPAR considerations                                       |      |

| 5.2.3 Processor configuration rules                             |      |

| 5.2.4 Memory configuration rules                                |      |

| 5.2.5 Advanced POWER Virtualization                             |      |

| 5.2.6 I/O sub-system configuration rules                        |      |

| 5.2.7 Disks, boot devices, and media devices                    |      |

| 5.2.8 PCI and PCI-X slots and adapters                          |      |

| 5.2.9 Keyboards and displays                                    |      |

| 5.2.10 Rack, power, and battery backup configuration rules      |      |

| 5.2.11 HMC configuration rules                                  |      |

| 5.2.12 Cluster 1600 considerations                              | 133  |

| 5.3 Capacity planning considerations                            | 133  |

| 5.3.1 p5-590 and p5-595 general considerations                  |      |

| 5.3.2 Further capacity planning considerations                  |      |

|                                                                 |      |

| Chapter 6. Reliability, availability, and serviceability        |      |

| 6.1 What's new in RAS                                           |      |

| 6.2 RAS overview                                                |      |

| 6.3 Predictive functions                                        |      |

| n.s.i. Eirst faillire data cantilre (EEL)(.)                    | 1/17 |

| 6.3.2 Predictive failure analysis                          | 142 |

|------------------------------------------------------------|-----|

| 6.3.3 Component reliability                                |     |

| 6.3.4 Extended system testing and surveillance             | 143 |

| 6.4 Redundancy in components                               | 144 |

| 6.4.1 Power and cooling redundancy                         | 144 |

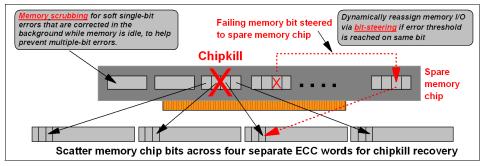

| 6.4.2 Memory redundancy mechanisms                         | 144 |

| 6.4.3 Service processor and clocks                         | 147 |

| 6.4.4 Multiple data paths                                  | 148 |

| 6.5 Fault recovery                                         | 148 |

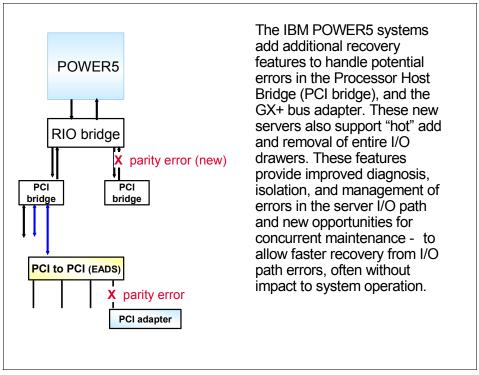

| 6.5.1 PCI bus error recovery                               | 148 |

| 6.5.2 Dynamic CPU deallocation                             | 150 |

| 6.5.3 CPU Guard                                            | 152 |

| 6.5.4 Hot-swappable components                             | 153 |

| 6.5.5 Hot-swappable boot disks                             | 154 |

| 6.5.6 Blind-swap PCI adapters                              | 154 |

| 6.5.7 Guiding Light Diagnostics                            | 156 |

| 6.6 Serviceability features                                | 157 |

| 6.6.1 Converged service architecture                       | 157 |

| 6.6.2 Hardware Management Console                          | 158 |

| 6.6.3 Error analyzing                                      | 159 |

| 6.6.4 Service processor                                    | 161 |

| 6.6.5 Service Agent                                        | 163 |

| 6.6.6 Service Focal Point                                  | 164 |

| 6.7 AIX RAS features                                       | 166 |

| 6.8 Linux RAS features                                     | 168 |

|                                                            |     |

| Chapter 7. Service processor                               |     |

| 7.1 Service processor functions                            |     |

| 7.1.1 Firmware binary image                                |     |

| 7.1.2 Platform initial program load                        |     |

| 7.1.3 Error Handling                                       |     |

| 7.2 Service processor cabling                              |     |

| 7.3 Advanced System Management Interface (ASMI)            |     |

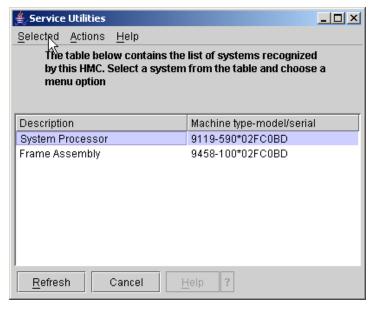

| 7.3.1 Accessing ASMI using HMC Service Focal Point utility |     |

| 7.3.2 Accessing ASMI using a Web browser                   |     |

| 7.3.3 ASMI login screen                                    |     |

| 7.3.4 ASMI user accounts                                   |     |

| 7.3.5 ASMI menu functions                                  |     |

| 7.3.6 Power On/Off tasks                                   |     |

| 7.3.7 System Service Aids tasks                            |     |

| 7.3.8 System Configuration ASMI menu                       |     |

| 7.3.9 Network Services ASMI menu                           |     |

| 7.3.10 Performance Setup ASMI menu                         | 185 |

| 7.4 Firmware updates                                   |     |

|--------------------------------------------------------|-----|

| Chapter 8. Hardware Management Console overview        |     |

| 8.1 Introduction                                       |     |

| 8.1.1 Desktop HMC                                      |     |

| 8.1.2 Rack mounted HMC                                 |     |

| 8.1.3 HMC characteristics                              |     |

| 8.2 HMC setup                                          |     |

| 8.2.1 The HMC logical communications                   |     |

| 8.3 HMC network interfaces                             |     |

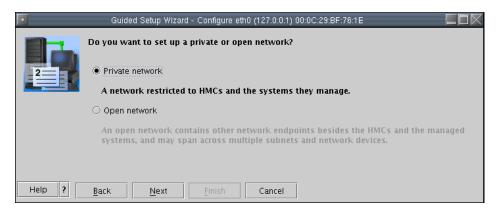

| 8.3.1 Private and open networks in the HMC environment |     |

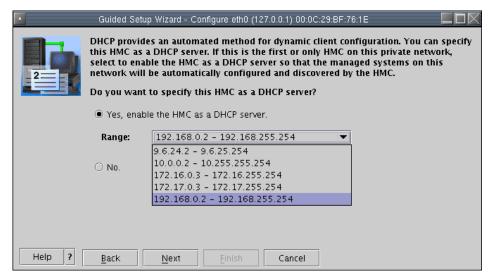

| 8.3.2 Using the HMC as a DHCP server                   |     |

| 8.3.3 HMC connections                                  |     |

| 8.3.4 Predefined HMC user accounts                     |     |

| 8.4.1 Required setup information                       |     |

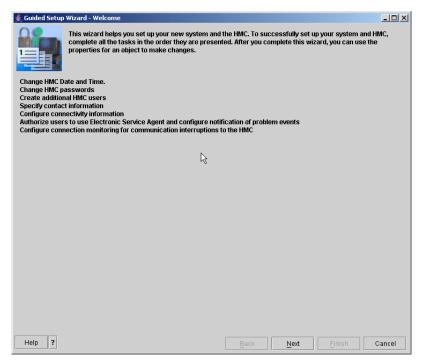

| 8.5 HMC Guided Setup Wizard                            |     |

| 8.6 HMC security and user management                   |     |

| 8.6.1 Server security                                  |     |

| 8.6.2 Object manager security                          |     |

| 8.6.3 HMC user management                              |     |

| 8.7 Inventory Scout services                           |     |

| 8.8 Service Agent and Service Focal Point              |     |

| 8.8.1 Service Agent                                    |     |

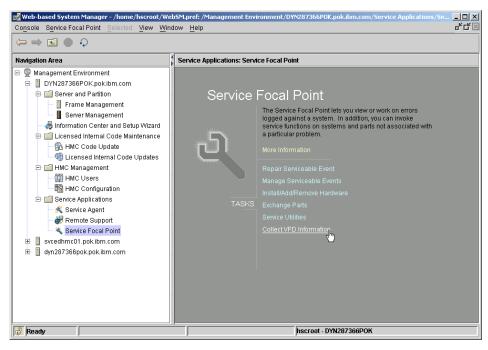

| 8.8.2 Service Focal Point                              |     |

| 8.9 HMC service utilities and tasks                    |     |

| 8.9.1 HMC boot up fails with fsck required             |     |

| 8.9.2 Determining HMC serial number                    |     |

| Appendix A. Facts and features reference               |     |

| Appendix A. 1 dots and leatures reference              | 240 |

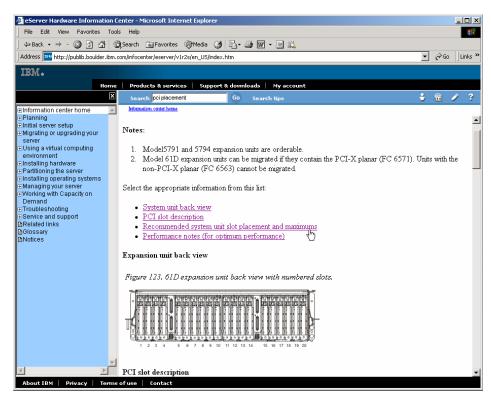

| Appendix B. PCI adapter placement guide                | 253 |

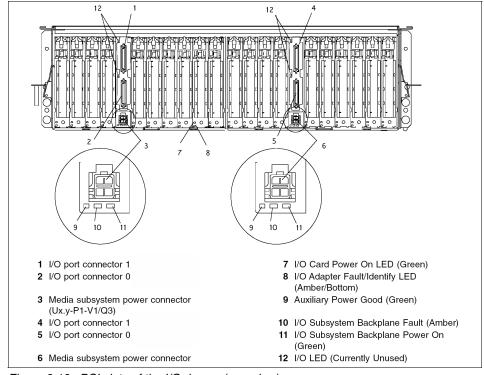

| Expansion unit back view PCI                           |     |

| PCI slot description                                   | 254 |

| Recommended system unit slot placement and maximums    | 255 |

| Annondiv C. Installation planning                      | OEO |

| Appendix C. Installation planning                      |     |

| Enhanced acoustical cover option                       |     |

| Slimline cover option                                  |     |

| Raised-floor requirements and preparation              |     |

| Securing the rack                                      |     |

| Considerations for multiple system installations       | 261 |

|                                                        |     |

| Index                                      | 281 |

|--------------------------------------------|-----|

| Abbreviations and acronyms                 | 277 |

| Help from IBM                              | 275 |

| How to get IBM Redbooks                    |     |

| Online resources                           |     |

| Other publications                         |     |

| IBM Redbooks                               |     |

| Related publications                       |     |

| How do I use the application?              | 268 |

| How do I get updates?                      |     |

| How do I get it?                           |     |

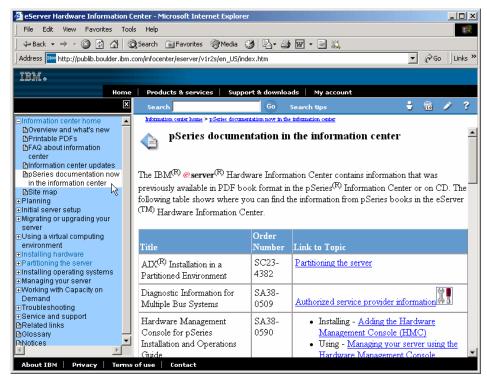

| What is the Hardware Information Center?   |     |

| IBM @server Hardware Information Center    |     |

| Appendix D. System documentation           |     |

| Planning and installation documentation    | 262 |

| Dual power installation                    |     |

| Moving the system to the installation site |     |

# **Figures**

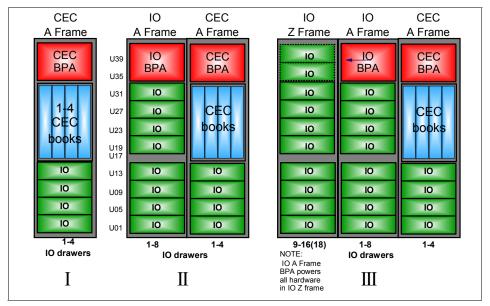

| 1-1  | Primary system frame organization                         | 4  |

|------|-----------------------------------------------------------|----|

| 1-2  | Powered and bolt on frames                                | 5  |

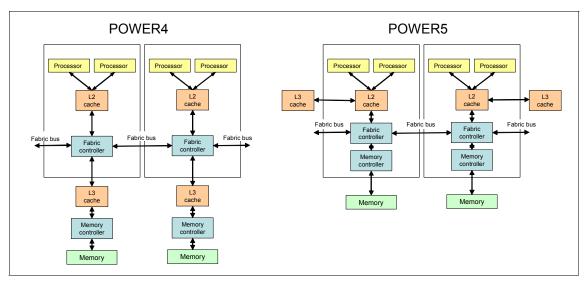

| 1-3  | POWER4 and POWER5 architecture comparison                 | 7  |

| 1-4  | POWER4 and POWER5 memory structure comparison             | 9  |

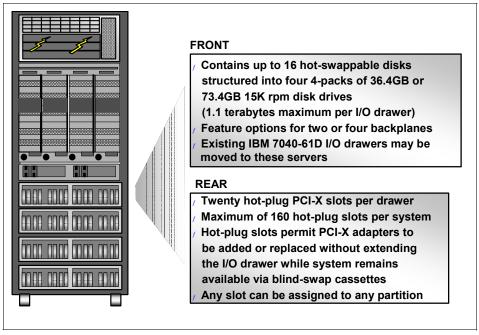

| 1-5  | p5-590 and p5-595 I/O drawer organization                 | 10 |

| 2-1  | POWER4 and POWER5 system structures                       | 19 |

| 2-2  | The POWER chip evolution                                  | 23 |

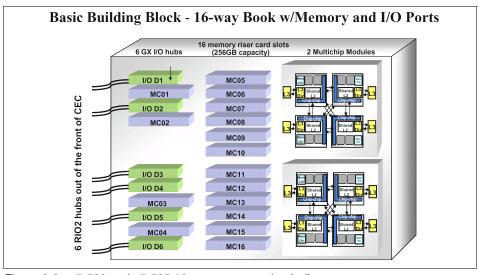

| 2-3  | p5-590 and p5-595 16-way processor book diagram           | 24 |

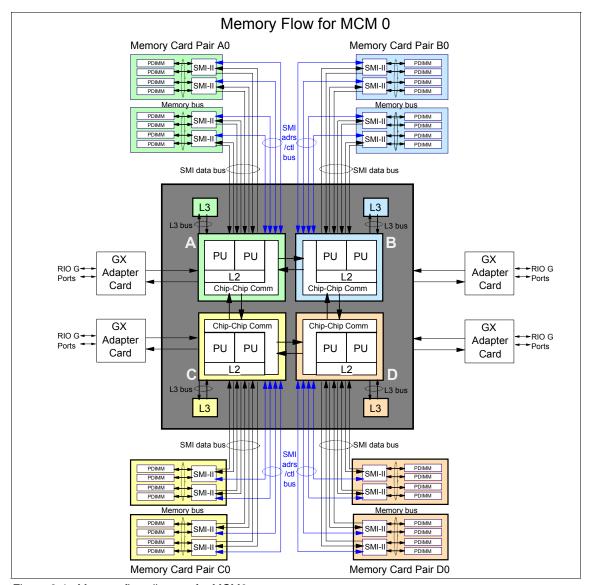

| 2-4  | Memory flow diagram for MCM0                              | 26 |

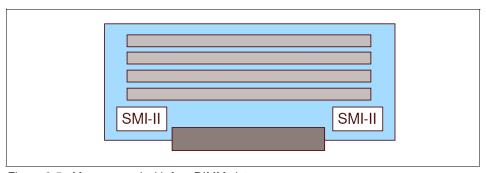

| 2-5  | Memory card with four DIMM slots                          | 27 |

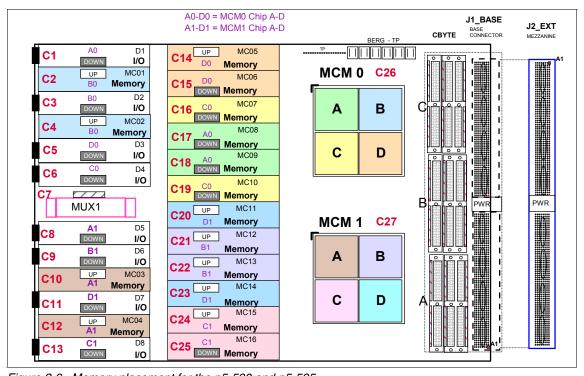

| 2-6  | Memory placement for the p5-590 and p5-595                | 28 |

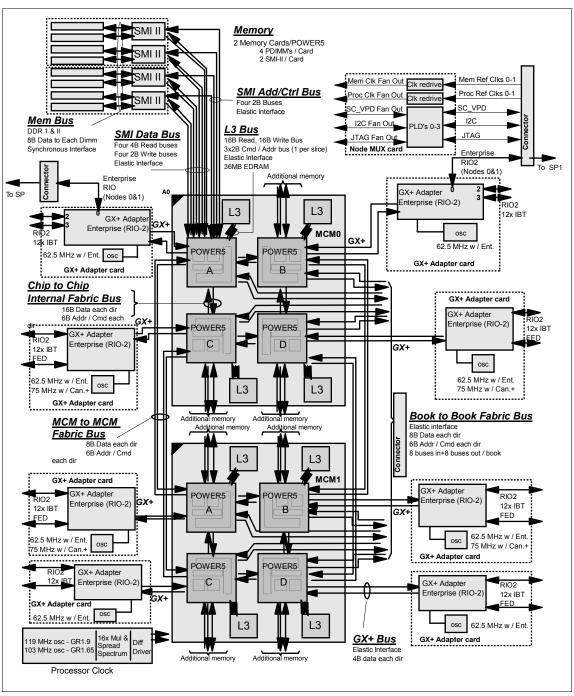

| 2-7  | p5-595 and p5-590 CEC logic diagram                       | 31 |

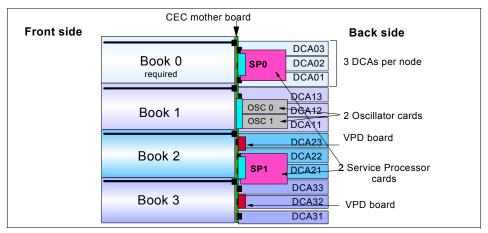

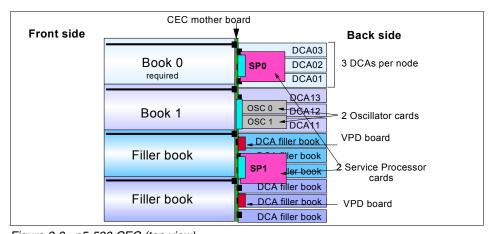

| 2-8  | p5-595 CEC (top view)                                     | 32 |

| 2-9  | p5-590 CEC (top view)                                     |    |

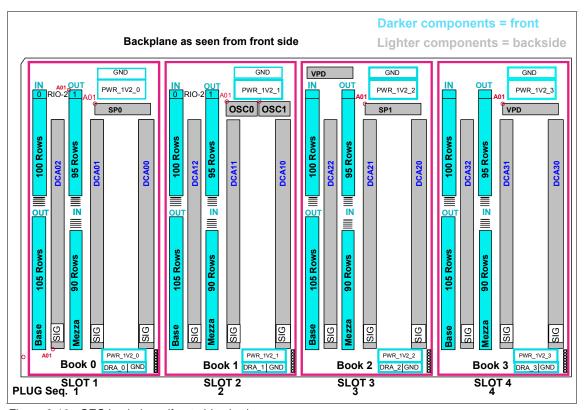

| 2-10 | CEC backplane (front side view)                           |    |

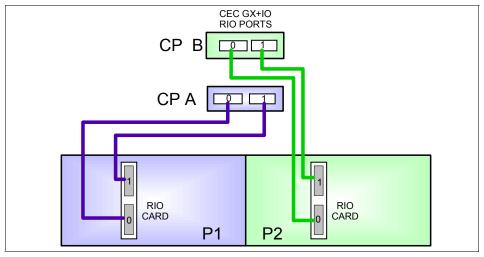

| 2-11 | Single loop 7040-61D                                      | 39 |

| 2-12 | Dual loop 7040-61D                                        | 40 |

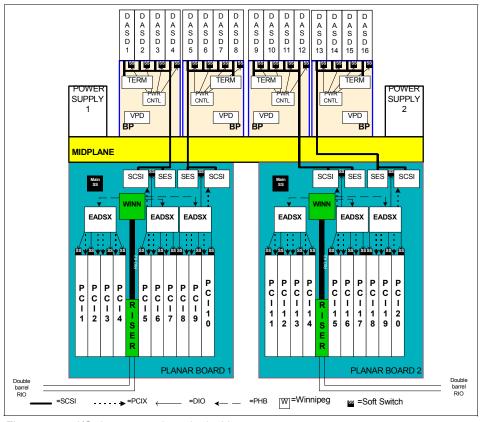

| 2-13 | I/O drawer -GX+                                           | 41 |

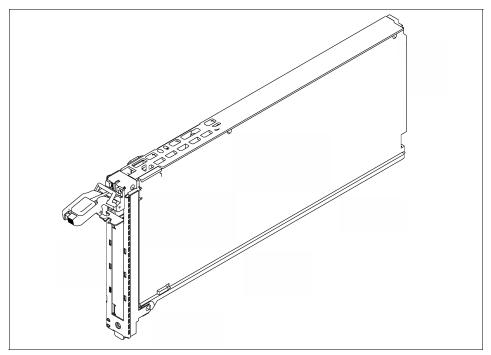

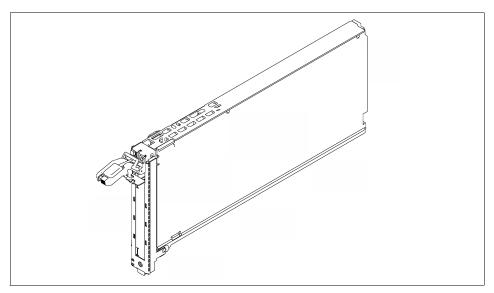

| 2-14 | Blind-swap cassette                                       | 42 |

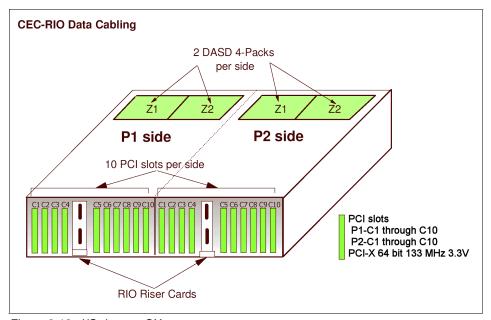

| 2-15 | I/O drawer top view - logical layout                      |    |

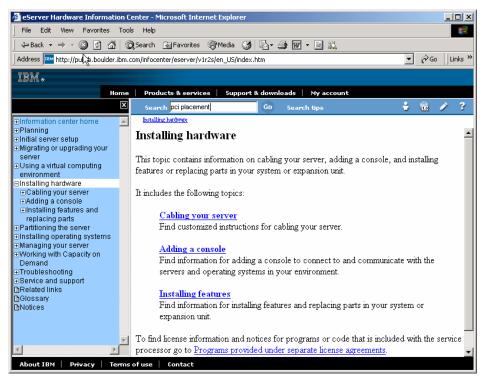

| 2-16 | Hardware Information Center search for PCI placement      |    |

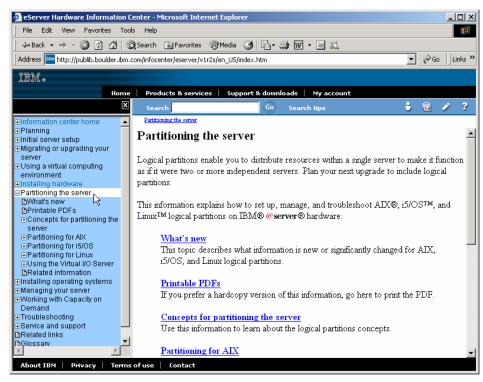

| 2-17 | Select Model 590 or 595 placement                         | 47 |

| 2-18 | PCI slots of the I/O drawer (rear view)                   |    |

| 2-19 | PCI placement guide on IBM @server information center     |    |

| 2-20 | Minimum to maximum I/O configuration                      |    |

| 2-21 | I/O frame configuration example                           |    |

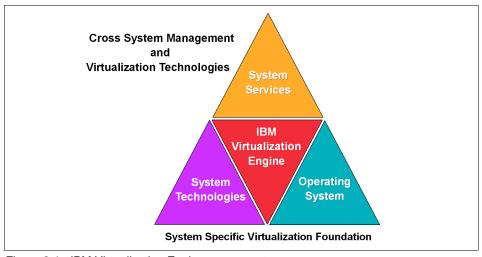

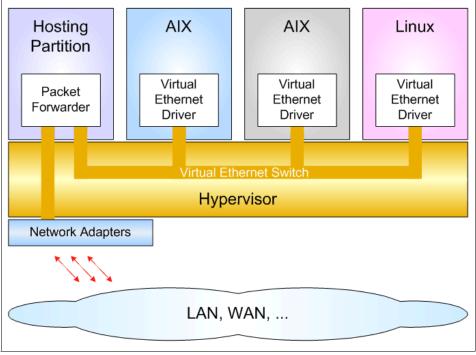

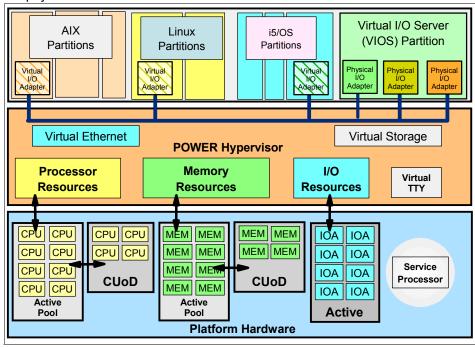

| 3-1  | IBM Virtualization Engine components                      |    |

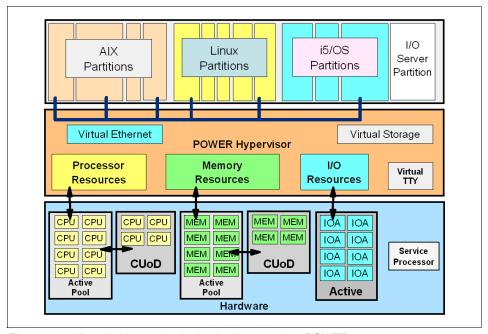

| 3-2  | Virtualization technologies implemented on POWER5 servers |    |

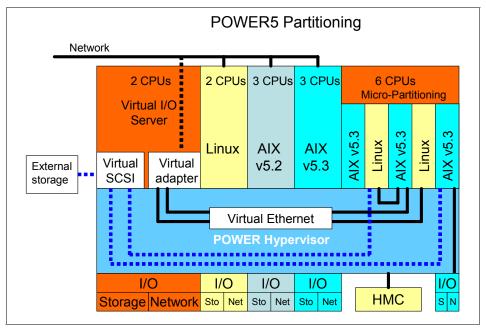

| 3-3  | POWER5 partitioning concept                               | 59 |

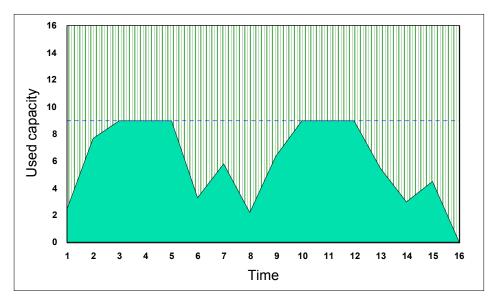

| 3-4  | Capped shared processor partitions                        |    |

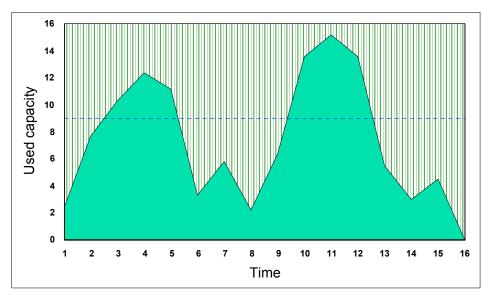

| 3-5  | Uncapped shared processor partitions                      |    |

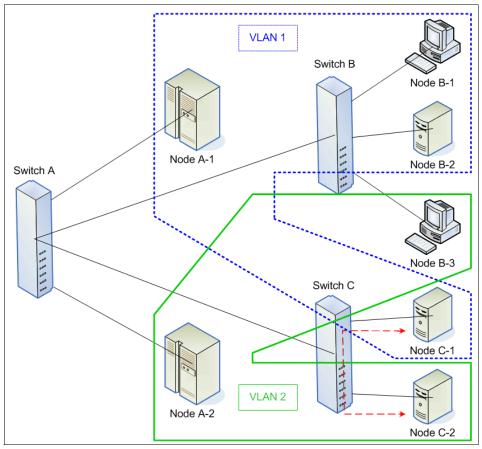

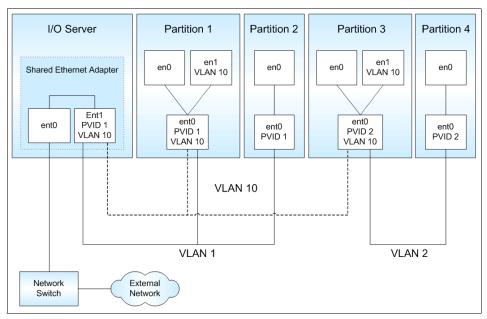

| 3-6  | Example of a VLAN                                         | 66 |

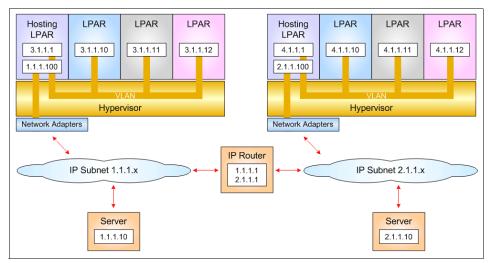

| 3-7  | VLAN configuration                                        |    |

| 3-8  | Logical view of an inter-partition VLAN                   |    |

| 3-9  | Connection to external network using AIX routing          |    |

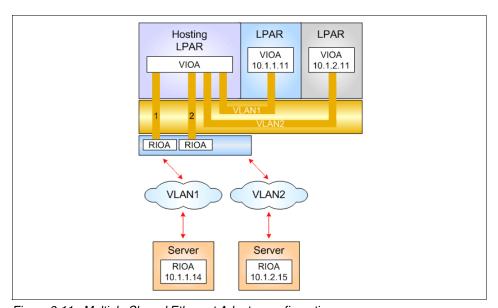

| 3-10 | Shared Ethernet Adapter configuration                     |    |

| 3-11 | Multiple Shared Ethernet Adapter configuration            |    |

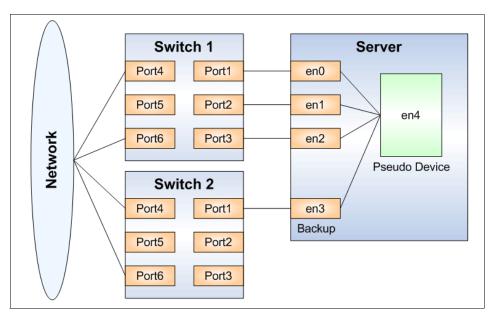

| 3-12 | Link Aggregation (EtherChannel) pseudo device             | 77 |

| 3-13 | IBM p5-590 and p5-595 Virtualization Technologies                   | . 79 |

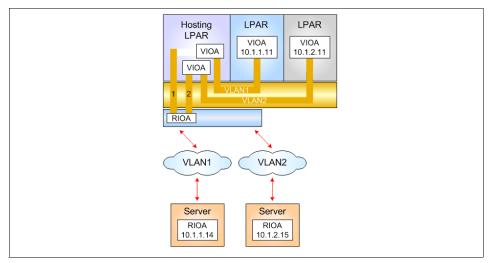

|------|---------------------------------------------------------------------|------|

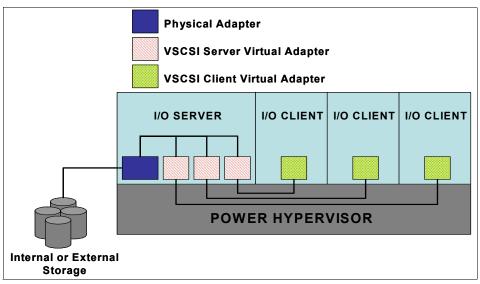

| 3-14 | AIX 5L Virtual I/O Server and Client Partitions                     | . 81 |

| 4-1  | HMC Capacity on Demand Order Selection Panel                        | . 89 |

| 4-2  | Enter CoD Enablement Code (HMC Screen)                              | . 90 |

| 4-3  | HMC Billing Selection Wizard                                        | . 94 |

| 4-4  | Manage On/Off CoD Processors HMC Activation Screen                  | . 95 |

| 4-5  | Manage On/Off CoD HMC Confirmation Panel and Legal Statement .      | . 96 |

| 4-6  | HMC Reserve CoD Processor Activation Screen                         | . 97 |

| 4-7  | CoD Processor Capacity Settings Overview HMC screen                 | 100  |

| 4-8  | CoD Processor Capacity Settings On/Off CoD HMC screen               | 100  |

| 4-9  | CoD Processor Capacity Settings Reserve CoD HMC screen              | 101  |

| 4-10 | CoD Processor Capacity Settings "Trial CoD" HMC Screen              | 101  |

| 5-1  | LPAR Validation Tool - creating a new partition                     | 112  |

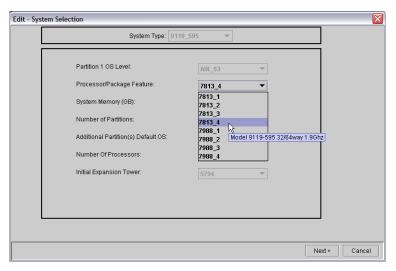

| 5-2  | LPAR Validation Tool - System Selection dialog                      | 112  |

| 5-3  | LPAR Validation Tool - System Selection processor feature selection | 113  |

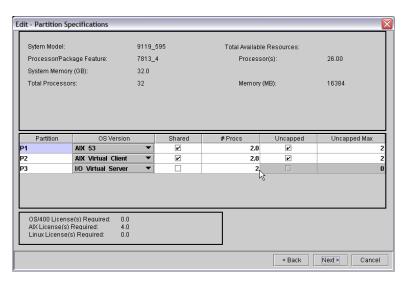

| 5-4  | LPAR Validation Tool - Partition Specifications dialog              | 113  |

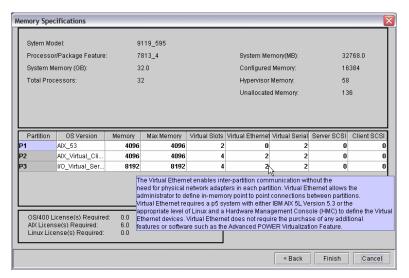

| 5-5  | LPAR Validation Tool - Memory Specifications dialog                 | 114  |

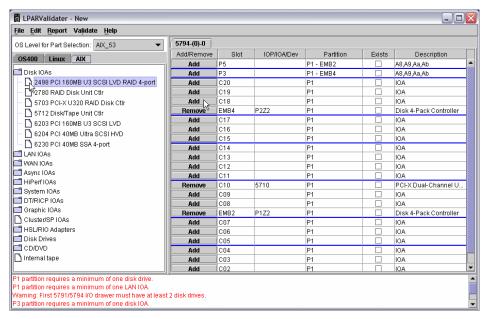

| 5-6  | LPAR Validation Tool - slot assignments                             | 115  |

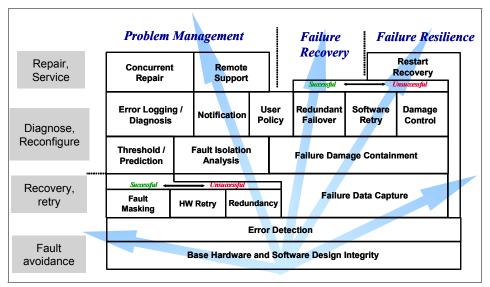

| 6-1  | IBMs RAS philosophy                                                 | 139  |

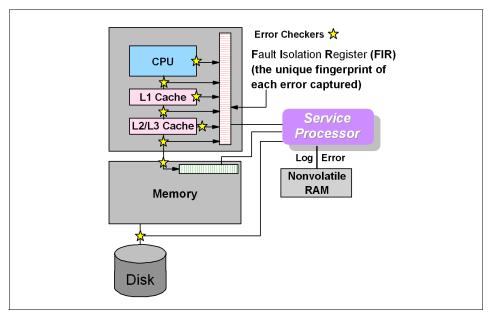

| 6-2  | FFDC error checkers and fault isolation registers                   | 141  |

| 6-3  | Memory error recovery mechanisms                                    | 145  |

| 6-4  | EEH on POWER5                                                       | 150  |

| 6-5  | Blind-swap cassette                                                 | 155  |

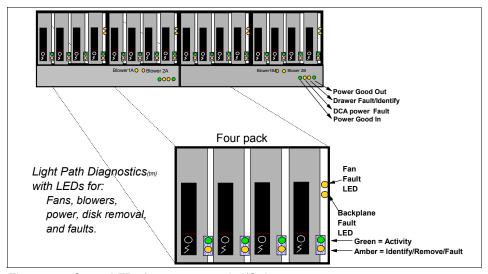

| 6-6  | Status LEDs for components in I/O drawers                           | 156  |

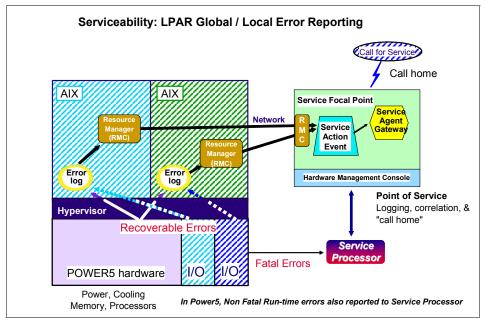

| 6-7  | Error reporting structure of POWER5                                 | 161  |

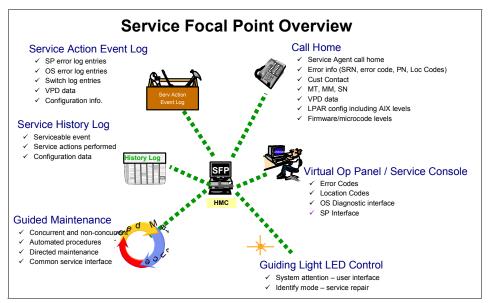

| 6-8  | Service focal point overview                                        | 165  |

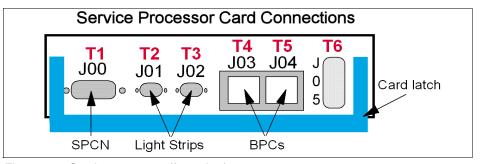

| 7-1  | Service processor (front view)                                      | 172  |

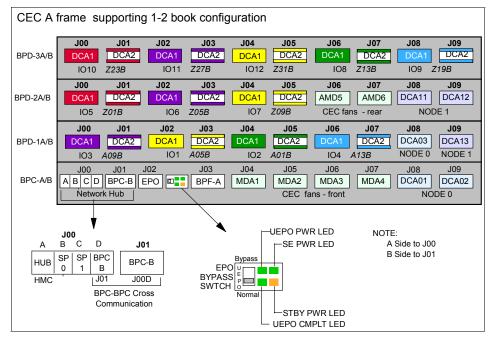

| 7-2  | Bulk power controller connections                                   | 174  |

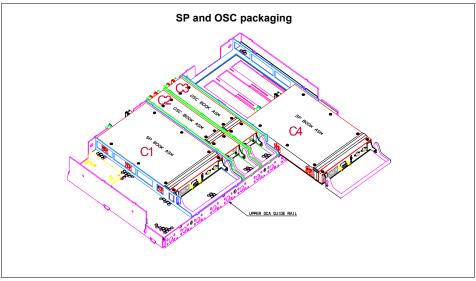

| 7-3  | Oscillator and service processor                                    |      |

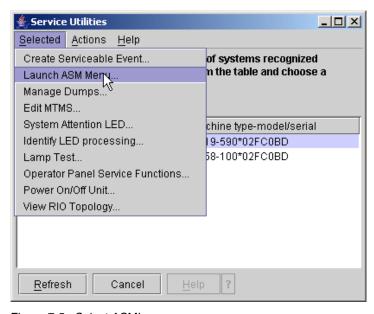

| 7-4  | Select service processor                                            |      |

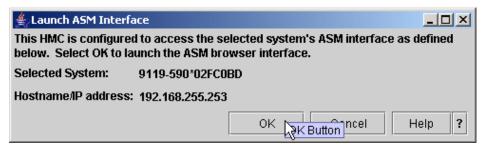

| 7-5  | Select ASMI                                                         | 176  |

| 7-6  | OK to launch                                                        | 177  |

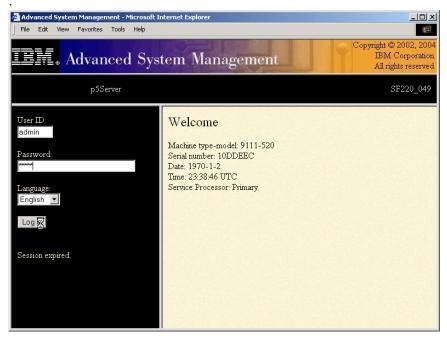

| 7-7  | ASMI login                                                          | 178  |

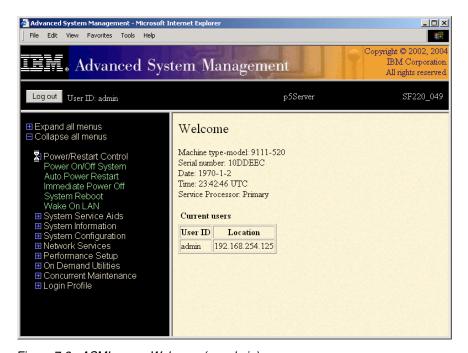

| 7-8  | ASMI menu: Welcome (as admin)                                       | 179  |

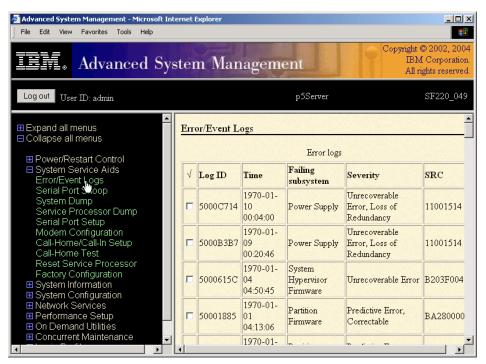

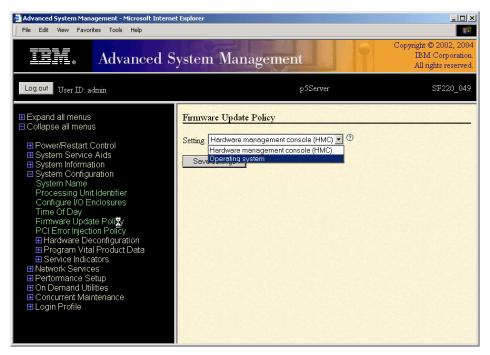

| 7-9  | ASMI menu: Error /Event Logs                                        | 181  |

| 7-10 | ASMI menu: Detailed Error Log                                       |      |

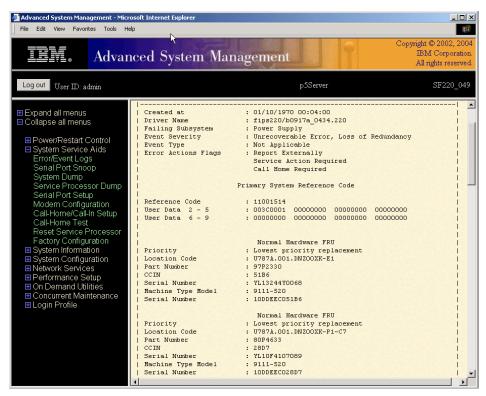

| 7-11 | ASMI menu: Factory Configuration                                    | 183  |

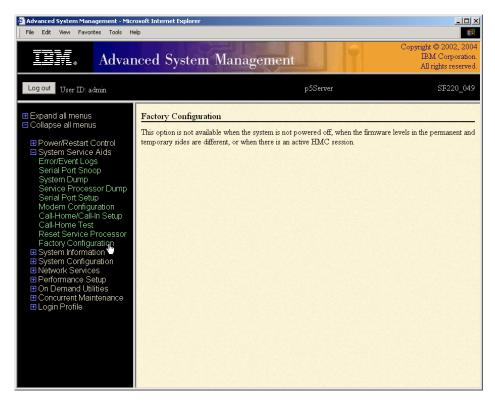

| 7-12 | ASMI Menu: Firmware Update Policy                                   | 184  |

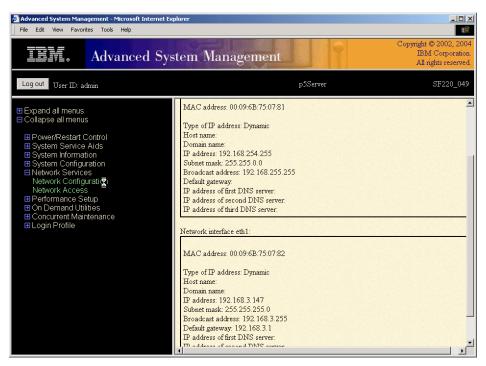

| 7-13 | ASMI menu: Network Configuration                                    | 185  |

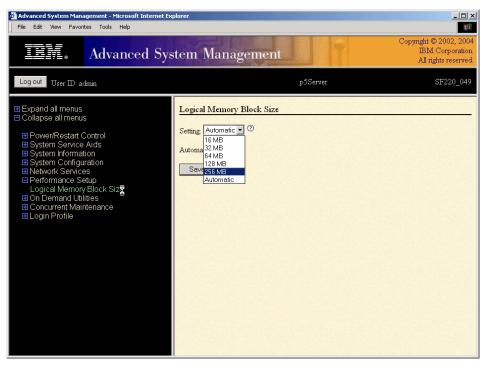

| 7-14 | ASMI menu: Logical Memory Block Size                                |      |

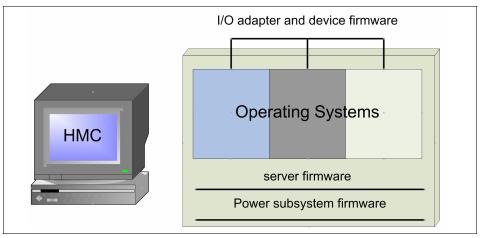

| 7-15 | Potential system components that require fixes                      |      |

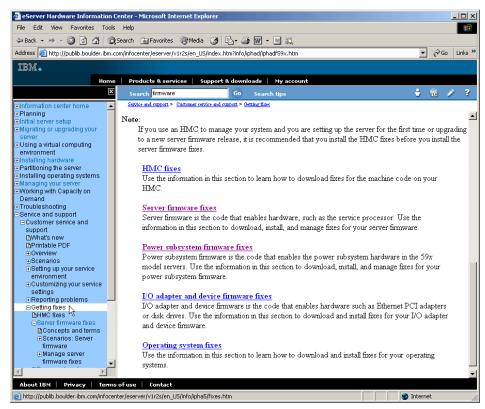

| 7-16 | Getting fixes from the IBM $@server$ Hardware Information Center    | 188  |

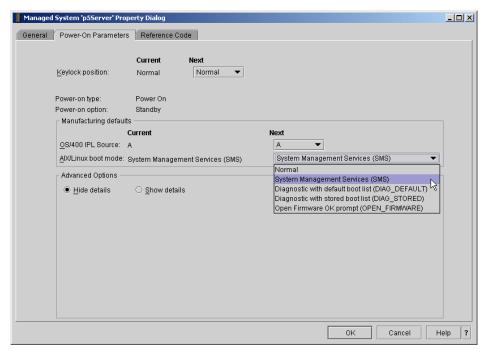

| 7-17 | Partition profile power-on properties                               | 189  |

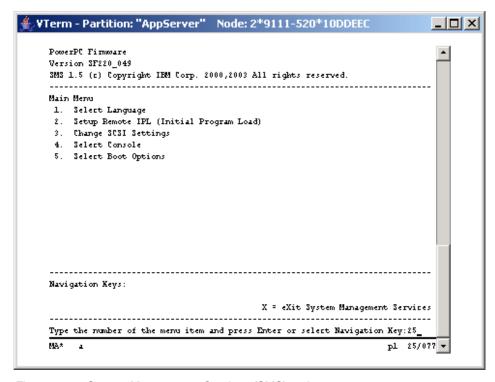

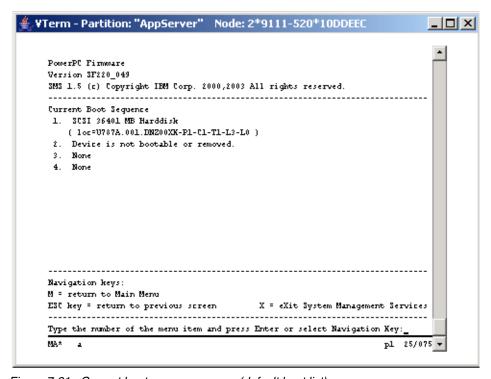

| 7-18 | System Management Services (SMS) main menu      |       |

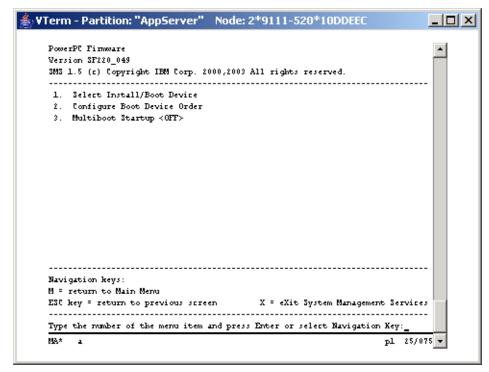

|------|-------------------------------------------------|-------|

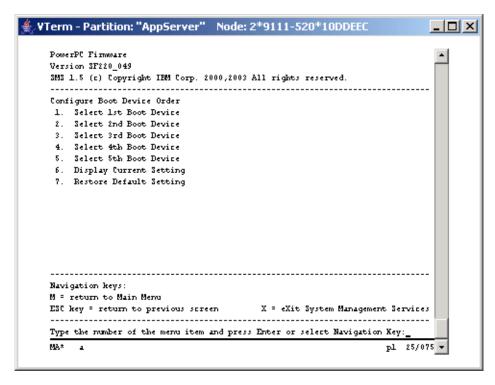

| 7-19 | Select Boot Options menu options                | . 191 |

| 7-20 | Configure Boot Device Order menu                | . 192 |

| 7-21 | Current boot sequence menu (default boot list)  | . 193 |

| 8-1  | Private direct network                          | . 203 |

| 8-2  | HMC with hub/switch attachment                  | . 204 |

| 8-3  | HMC attached to both private and public network | . 205 |

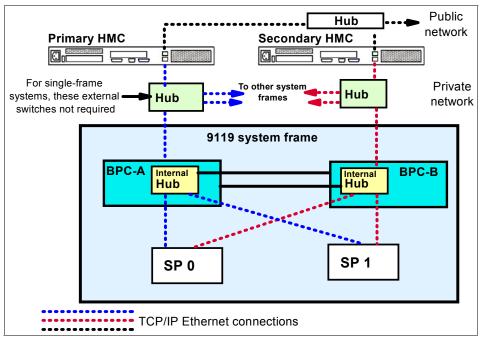

| 8-4  | Primary and secondary HMC to BPC connections    | . 206 |

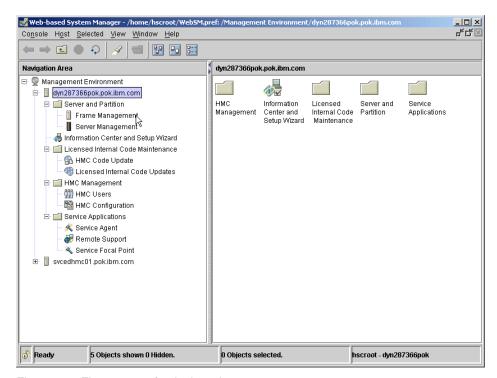

| 8-5  | First screen after login as hscroot user        |       |

| 8-6  | Guided Setup Wizard                             | . 210 |

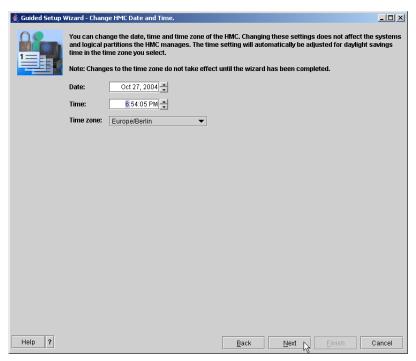

| 8-7  | Date and Time settings                          | . 211 |

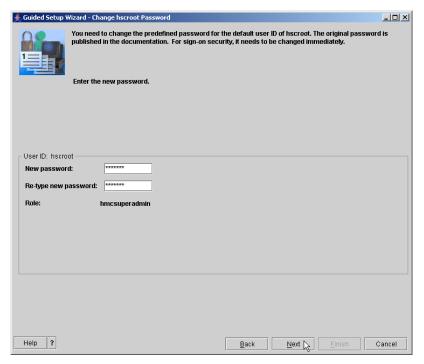

| 8-8  | The hscroot password                            | . 212 |

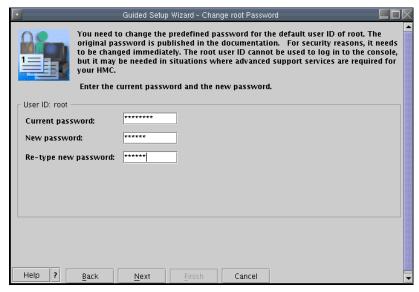

| 8-9  | The root password                               | . 213 |

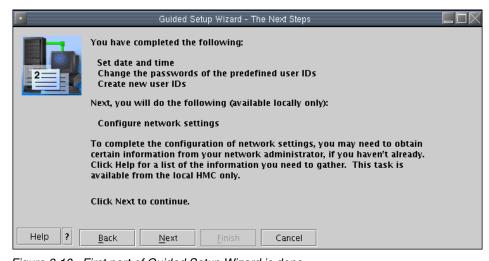

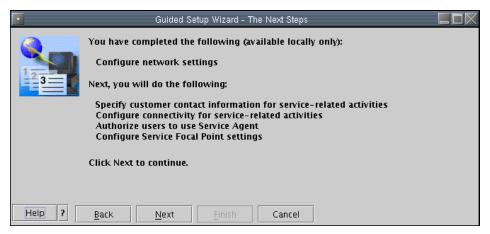

| 8-10 | First part of Guided Setup Wizard is done       | . 213 |

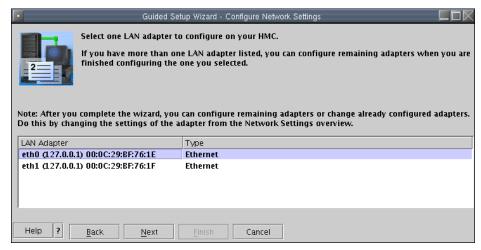

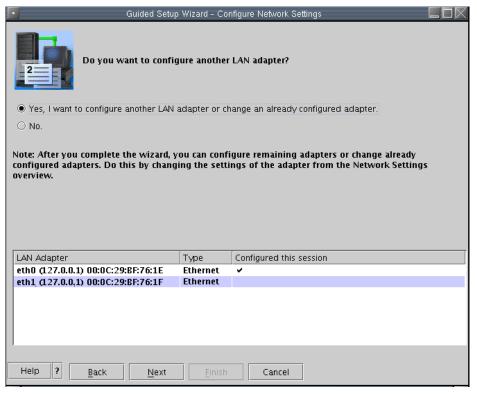

| 8-11 | Select LAN adapter                              |       |

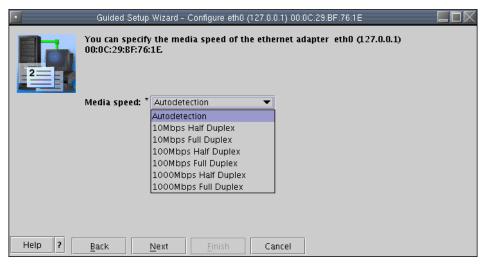

| 8-12 | Speed selection                                 | . 215 |

| 8-13 | Network type                                    | . 215 |

| 8-14 | Configure eth0 DHCP range                       | . 217 |

| 8-15 | Second LAN adapter                              | . 218 |

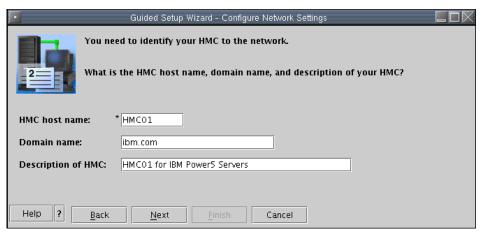

| 8-16 | Host name and domain name                       | . 219 |

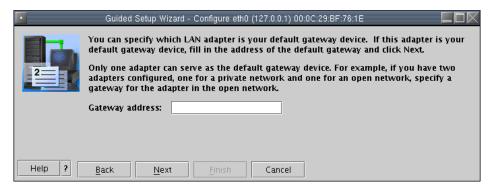

| 8-17 | Default gateway IP address                      | . 219 |

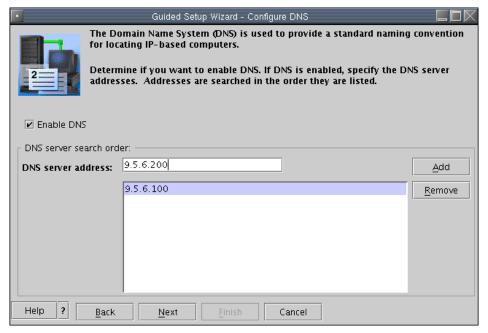

| 8-18 | DNS IP address                                  |       |

| 8-19 | End of network configuration                    | . 220 |

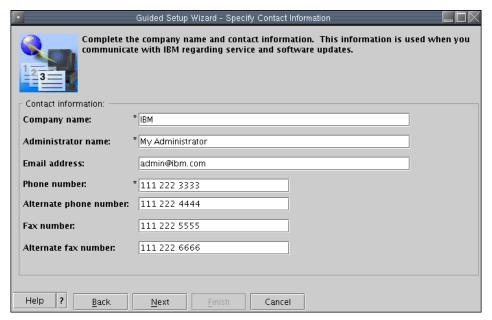

| 8-20 | Client contact information                      | . 221 |

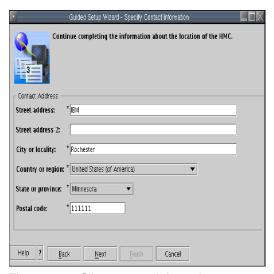

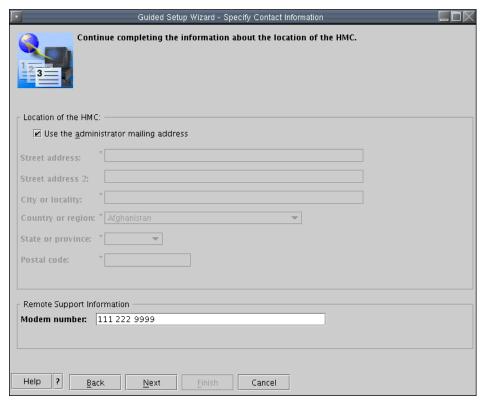

| 8-21 | Client contact information                      | . 221 |

| 8-22 | Remote support information                      | . 222 |

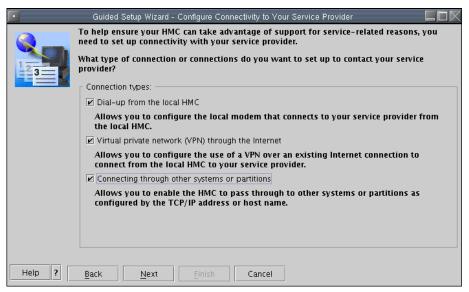

| 8-23 | Callhome connection type                        |       |

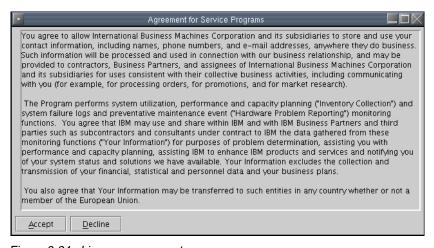

| 8-24 | Licence agreement                               |       |

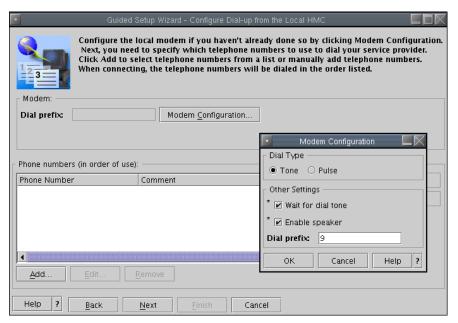

| 8-25 | Modem configuration                             | . 225 |

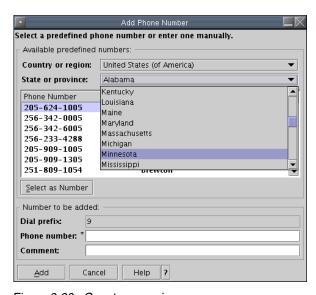

| 8-26 | Country or region                               |       |

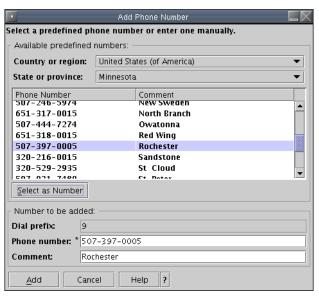

| 8-27 | Select phone number for modem                   | . 226 |

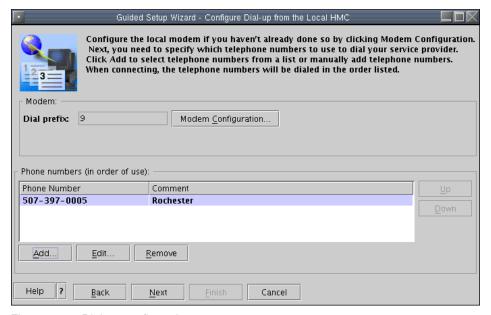

| 8-28 | Dial-up configuration                           | . 226 |

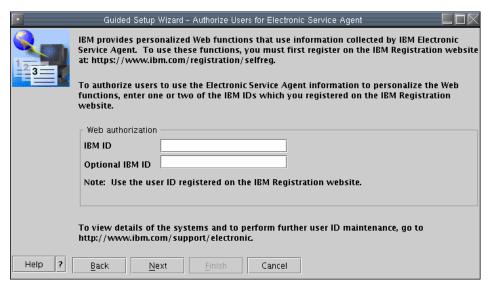

| 8-29 | Authorized user for ESA                         | . 227 |

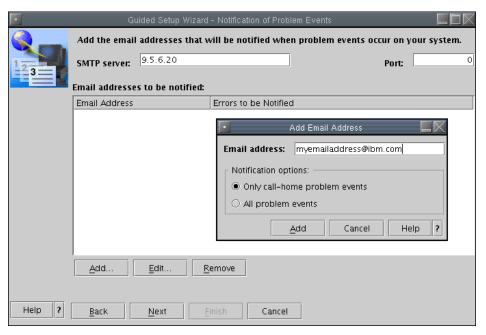

| 8-30 | The e-mail notification dialog                  | . 228 |

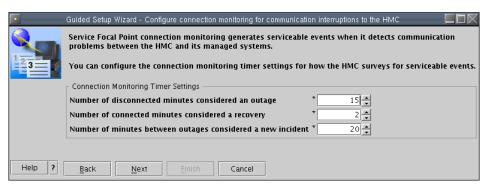

| 8-31 | Communication interruptions                     | . 229 |

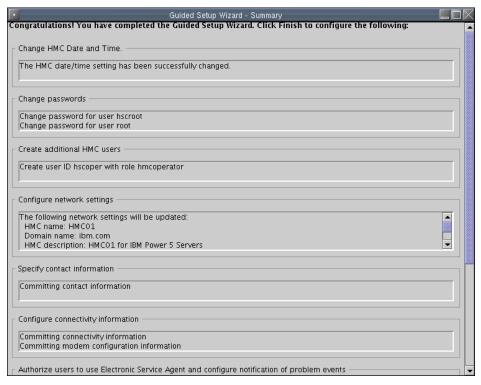

| 8-32 | Summary screen                                  |       |

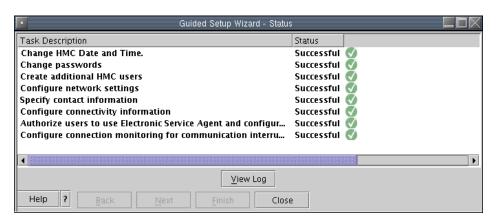

| 8-33 | Status screen                                   | . 230 |

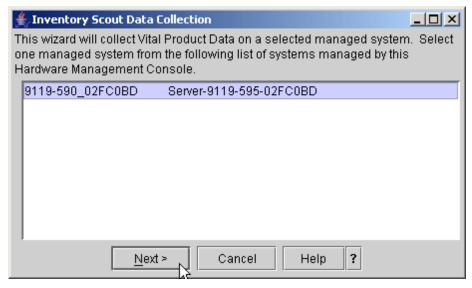

| 8-34 | Inventory Scout                                 |       |

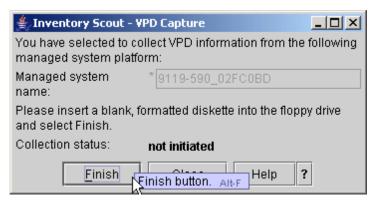

| 8-35 | Select server to get VPD data                   | . 236 |

| 8-36 | Store data                                      |       |

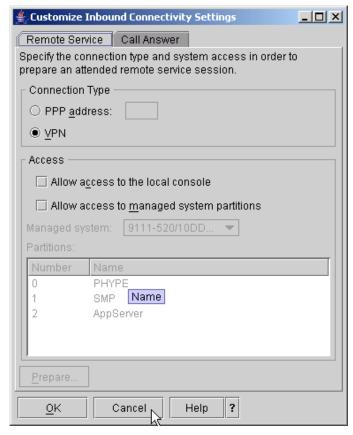

| 8-37 | PPP or VPN connection                           | . 239 |

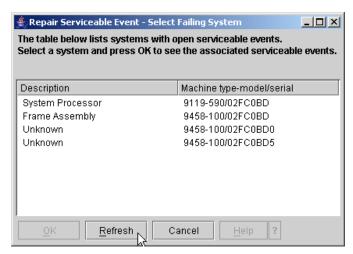

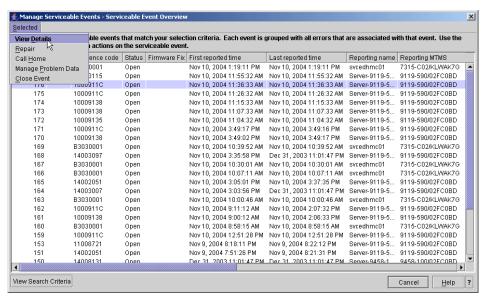

| 8-38 | Open serviceable events                         | . 240 |

| 8-39 | Manage service events                           | . 241 |

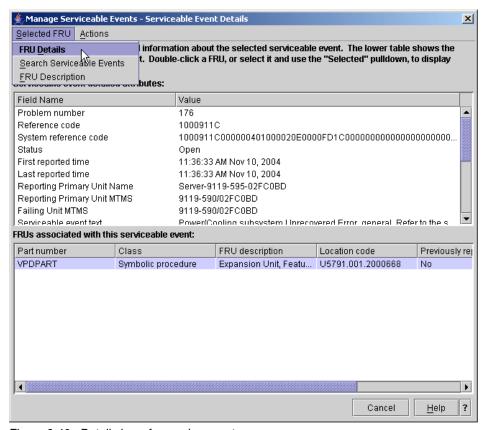

| 8-40 | Detail view of a service event                        | . 242 |

|------|-------------------------------------------------------|-------|

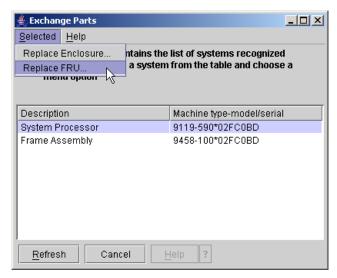

| 8-41 | Exchange parts                                        | . 243 |

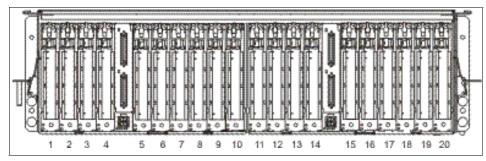

| B-1  | 7040-61D expansion unit back view with numbered slots | . 254 |

| C-1  | Search for planning                                   | . 263 |

| C-2  | Select 9119-590 and 9119-595                          | . 263 |

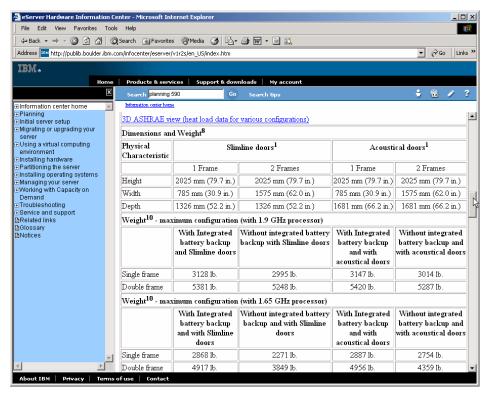

| C-3  | Planning information                                  | . 264 |

| D-1  | Information Center                                    | . 268 |

| D-2  | Search field                                          | . 269 |

| D-3  | Navigation bar                                        | . 270 |

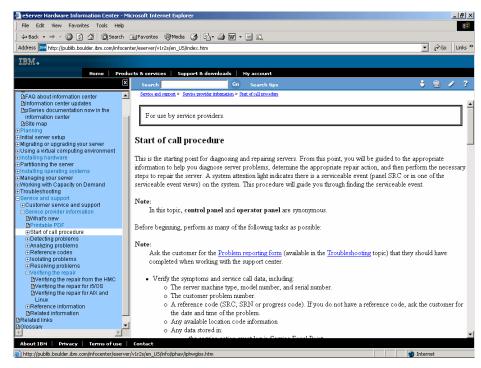

| D-4  | Toolbar with start off call                           | . 271 |

| D-5  | Previous pSeries documentation                        | . 272 |

# **Tables**

| 1-1 | p5-590 and p5-595 features summary                               | 12    |

|-----|------------------------------------------------------------------|-------|

| 1-2 | p5-590 and p5-595 operating systems compatibility                | 13    |

| 2-1 | Memory configuration table                                       |       |

| 2-2 | Types of available memory cards for p5-590 and p5-595            | 28    |

| 2-3 | Number of possible I/O loop connections                          | 38    |

| 3-1 | Micro-Partitioning overview on p5 systems                        | 59    |

| 3-2 | Interpartition VLAN communication                                |       |

| 3-3 | VLAN communication to external network                           | 69    |

| 3-4 | Main differences between EC and LA aggregation                   | 76    |

| 4-1 | CoD feature comparisons                                          | 85    |

| 4-2 | Types of Capacity on Demand (functional categories)              | 88    |

| 4-3 | Permanently activated processors by MCM                          | . 102 |

| 4-4 | License entitlement example                                      | . 105 |

| 4-5 | p5-590 and p5-595 CoD Feature Codes                              | . 107 |

| 5-1 | p5-590 minimum system configuration                              | . 116 |

| 5-2 | p5-595 minimum system configuration                              |       |

| 5-3 | Configurable memory-to-default memory block size                 | . 123 |

| 5-4 | p5-590 I/O drawers quantity with different loop mode             |       |

| 5-5 | p5-595 I/O drawers quantity with different loop mode             |       |

| 5-6 | Required Hardware Management Console                             | . 131 |

| 6-1 | Hot-swappable FRUs                                               |       |

| 7-1 | Table of service processor card location codes                   |       |

| 7-2 | Summary of BPC Ethernet hub port connectors                      | . 173 |

| 7-3 | ASMI user accounts                                               |       |

| 7-4 | ASMI user-level access (menu options)                            | . 180 |

| 8-1 | HMC user passwords                                               |       |

| A-1 | Facts and Features for p5-590 and p5-595                         |       |

| A-2 | System unit details                                              |       |

| A-3 | Server I/O attachment                                            | . 249 |

| A-4 | Peak bandwidth                                                   |       |

| A-5 | Standard warranty in United States, other countries may vary     | . 250 |

| A-6 | Physical planning characteristics                                | . 250 |

| A-7 | Racks                                                            | . 251 |

| A-8 | I/O device options list                                          | . 252 |

| B-1 | Model 61D expansion unit slot location description (PHB 1 and 2) | . 254 |

| B-2 | Model 61D expansion unit slot location description (PHB 3)       | . 254 |

| B-3 | p5-590 and p5-595 PCI adapter placement table                    | . 255 |

## **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Any performance data contained herein was determined in a controlled environment. Therefore, the results obtained in other operating environments may vary significantly. Some measurements may have been made on development-level systems and there is no guarantee that these measurements will be the same on generally available systems. Furthermore, some measurement may have been estimated through extrapolation. Actual results may vary. Users of this document should verify the applicable data for their specific environment.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in

any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy, modify, and distribute these sample programs in any form without payment to IBM for the purposes of developing, using, marketing, or distributing application programs conforming to IBM's application programming interfaces.

#### **Trademarks**

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

400@IBM®POWERTMBladeCenterTMMicro Channel®PS/2®ChipkillTMMicro-PartitioningTMPTX®

Electronic Service Agent™ OpenPower™ Redbooks (logo)

™Balance®

Enterprise Storage Server® Power Architecture™ Redbooks™

ESCON® Power PC® RS/6000®

@server® POWER2™ S/390®

@server® POWER4+™ TotalStorage®

Extreme Blue™ POWER4™ Versatile Storage Server™ HACMP™ POWER5™ Virtualization Engine™

Hypervisor<sup>™</sup> PowerPC®

The following terms are trademarks of other companies:

Java and all Java-based trademarks and logos are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

Microsoft, Windows, Windows NT, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Intel, Intel Inside (logos), MMX, and Pentium are trademarks of Intel Corporation in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries.

Linux is a trademark of Linus Torvalds in the United States, other countries, or both.

Other company, product, and service names may be trademarks or service marks of others.

# **Preface**

This IBM Redbook explores the IBM @server p5 models 590 and 595 (9119-590, 9119-595), a new level of UNIX servers providing world-class performance, availability, and flexibility. Ideal for on demand computing environments, data center implementation, application service providers, and high performance computing, this new class of high-end servers include mainframe-inspired self-management and security designed to meet your most demanding needs. The IBM @server p5 590 and p5 595 provide an expandable, high-end enterprise solution for managing the computing requirements needed to become an on demand business.

This publication includes the following topics:

- ▶ p5-590 and p5-595 overview

- ▶ p5-590 and p5-595 hardware architecture

- Virtualization features overview

- Capacity on Demand overview

- Reliability, availability, and serviceability overview

- Hardware Management Console features and functions

This publication is an ideal desk-side reference for IBM professionals, IBM Business Partners, and technical specialists who support the p5-590 and p5-595, and for those who want to learn more about this radically new server in a clear, single-source handbook.

#### The team that wrote this redbook

This redbook was produced by a team of specialists from around the world working at the International Technical Support Organization, Austin Center.

**Ding Wei** is an Advisory IT Specialist working for IBM China ATS. He has eight years of experience in the Information Technology field. His areas of expertise include pSeries and storage products and solutions. He has been working for IBM for six years.

**Peter Domberg** (Domi) is a Technical Support Specialist in Germany. He has 27 years of experience in the ITS hardware service. His areas of expertise include pSeries, RS/6000®, networking, and SSA storage. He is also an AIX

certified specialist and hardware support specialist for the North and East Germany regions.

**TaiJung Kim** is a pSeries systems product engineer at the pSeries post-sales technical support team in IBM Korea. He has three years of experience working on RS/6000 and pSeries products. He is an IBM Certified Specialist in pSeries systems and AIX. He provides clients with technical support on pSeries systems, AIX, and system management.

Nia Kelley is a Staff Software Engineer based in IBM Austin with over four years of experience in the pSeries firmware development field. She holds a Bachelors of Science degree in Electrical Engineering from the University of Maryland at College Park. Her areas of expertise include system bringup and firmware development. She has led several project teams working in her areas of expertise, in addition to holding various architectural positions for existing and future pSeries products. Ms. Kelley is an alumni of the IBM Extreme Blue program and has filed numerous patents for the IBM corporation.

Thanks to the following people for their contributions to this project:

International Technical Support Organization, Austin Center Scott Vetter

IBM Austin

Anis Abdul, George Ahrens, Doug Bossen, Pat Buckland, Mark Dewalt, Bob Foster, Iggy Haider, Dan Henderson, Richard (Jamie) Knight, Andy McLaughlin, Cathy Nunez, Jayesh Patel, Craig Shempert, Guillermo Silva, Joel Tendler

IBM Endicott Brian Tolan

IBM Raleigh Andre Metelo

**IBM Rochester**

Salim Agha, Diane Knipfer, Dave Lewis, Matthew Spinler, Stephanie Swanson

IBM Poughkeepsie Doug Baska

IBM Boca Raton Arthur J. Prchlik

IBM Somers Bill Mihaltse IBM UK

Derrick Daines, Dave Williams

IBM France Jacques Noury

**IBM Germany**

Hans Mozes, Wolfgang Seiwald

IBM Australia Cameron Ferstat

BM Italy

Carlo Costantini

IBM Redbook "Partitioning Implementations for IBM @server p5 and pSeries Servers" Team

Nic Irving (CSC Corporation - Australia), Matthew Jenner (IBM Australia), Arsi Kortesnemi (IBM Finland)

#### Become a published author

Join us for a two- to six-week residency program! Help write an IBM Redbook dealing with specific products or solutions, while getting hands-on experience with leading-edge technologies. You'll team with IBM technical professionals, Business Partners and/or customers.

Your efforts will help increase product acceptance and customer satisfaction. As a bonus, you'll develop a network of contacts in IBM development labs, and increase your productivity and marketability.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

#### **Comments welcome**

Your comments are important to us!

We want our Redbooks to be as helpful as possible. Send us your comments about this or other Redbooks in one of the following ways:

▶ Use the online **Contact us** review redbook form found at:

ibm.com/redbooks

Send your comments in an email to:

redbook@us.ibm.com

► Mail your comments to:

IBM Corporation, International Technical Support Organization Dept. JN9B Building 905 11501 Burnet Road Austin, Texas 78758-3493

# 1

# **System overview**

In this chapter we provide a basic overview of the p5-590 and p5-595 servers, highlighting the new features, marketing position, main features, and operating systems.

- ► Section 1.1, "Introduction" on page 2

- ► Section 1.2, "What's new" on page 2

- Section 1.3, "General overview and characteristics" on page 4

- ► Section 1.4, "Features summary" on page 12

- ► Section 1.5, "Operating systems support" on page 13

#### 1.1 Introduction

The IBM @server p5 590 and IBM @server p5 595 are the servers redefining the IT economics of enterprise UNIX and Linux computing. The up to 64-way p5-595 server is the new flagship of the product line with nearly three times the commercial performance and twice the capacity of its predecessor, the IBM @server pSeries 690. Accompanying the p5-595 is the up to 32-way p5-590 that offers enterprise-class function and more performance than the pSeries 690 at a significantly lower price for comparable configurations.

Both systems are powered by IBMs most advanced 64-bit Power Architecture microprocessor, the IBM POWER5 microprocessor, with simultaneous multi-threading that makes each processor function as two to the operating system, thus increasing commercial performance and system utilization over servers without this capability. The p5-595 features a choice of IBMs fastest POWER5 processors running at 1.90 GHz or 1.65 GHz, while the p5-590 offers 1.65 GHz processors.

These servers come standard with mainframe-proven reliability, availability, serviceability (RAS) capabilities and IBM Virtualization Engine systems technology with breakthrough innovations such as Micro-Partitioning. Micro-Partitioning allows as many as ten dynamic logical partitions (LPARs) per processor to be defined. Both systems can be configured with up to 254 virtual servers with a choice of AIX 5L, Linux, and i5/OS operating systems in a single server, opening the door to vast cost-saving consolidation opportunities.

#### 1.2 What's new

The p5-590 and p5-595 bring the following features:

#### ► POWER5 microprocessor

Designed to provide excellent application performance and high reliability. Includes simultaneous multi-threading to help increase commercial system performance and processor utilization. See Section 1.3.1, "Microprocessor technology" on page 6 and Section 2.2, "The POWER5 microprocessor" on page 18 for more information.

#### ► High memory / I/O bandwidth

Fast processors wait less for data to be moved through the system. Delivers data faster for the needs of high performance computing and other memory-intensive applications. See Section 2.3, "Memory subsystem" on page 26 for more information.

#### Flexibility in packaging

High-density 24-inch system frame for maximum growth. See Section 1.3, "General overview and characteristics" on page 4 for more information.

#### \* Indicates this feature is optional, is available on selected models, or requires separate software.

#### Shared processor pool\*

Provides the ability to transparently share processing power between partitions. Helps balance processing power and ensures the high priority partitions receive the processor cycles they need. See Section 3.2.1, "Shared processor partitions" on page 58 for more information.

#### ► Micro-Partitioning\*

Allows each processor in the shared processor pool to be split into as many as ten partitions. Fine-tuned processing power to match workloads. See Section 3.2, "Micro-Partitioning" on page 57 for more information.

#### ▶ Virtual I/O\*

Shares expensive resources to help reduce costs. See Section 3.6, "Virtual SCSI" on page 80 for more information.

#### ▶ Virtual LAN\*

Provides the capability for TCP/IP communication between partitions without the need for additional network adapters. See Section 3.3, "Virtual Ethernet" on page 64 for more information.

#### Dynamic logical partitioning

Allows reallocation of system resources without rebooting affected partitions. Offers greater flexibility in using available capacity and more rapidly matching resources to changing business requirements.

#### Mainframe-inspired RAS

Delivers exceptional system availability using features usually found on much more expensive systems including service processor, Chipkill memory, first failure data capture, dynamic deallocation of selected system resources, dual system clocks, and more. See Chapter 6, "Reliability, availability, and serviceability" on page 137 for more information.

#### Broad range of CoD offerings\*

Provides temporary access to processors and memory to meet predictable business spikes. Prepaid access to processors to meet intermittent or seasonal demands. Offers a one-time 30 day trial to test increased processor or memory capacity before permanent activation. Allow processors and memory to be permanently added to meet long term workload increases. See Chapter 4, "Capacity on Demand" on page 83 for more information.

#### Grid Computing support\*

Allows sharing of a wide range of computing and data resources across heterogeneous, geographically dispersed environments.

#### Scaling through Cluster Systems Management support

Allows for more granular growth so end-user demands can be readily satisfied. Provides centralized management of multiple interconnected systems. Provides ability to handle unexpected workload peaks by sharing resources.

#### Multiple operating system support

Allows clients the flexibility to select the right operating system and the right application to meet their needs. Provides the ability to expand applications choices to include many open source applications. See Section 1.5, "Operating systems support" on page 13for more information.

#### 1.3 General overview and characteristics

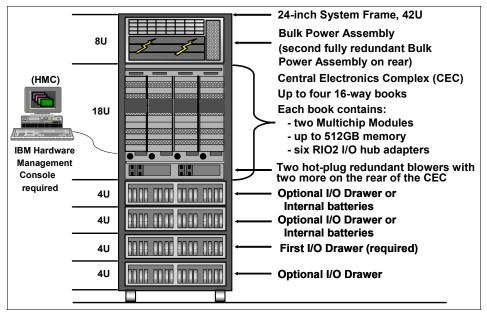

The p5-590 and p5-595 servers are designed with a basic server configuration that starts with a single rack, sometimes called a *frame* (Figure 1-1), and is featured with optional and required components.

Figure 1-1 Primary system frame organization

Both systems are powered by IBMs most advanced 64-bit Power Architecture microprocessor, the IBM POWER5 microprocessor, with simultaneous multi-threading that makes each processor logically appear as two to the operating system, thus increasing commercial throughput and system utilization over servers without this capability. The p5-595 features a choice of IBMs fastest POWER5 microprocessors running at 1.9 GHz or 1.65 GHz, while the p5-590 offers 1.65 GHz processors.

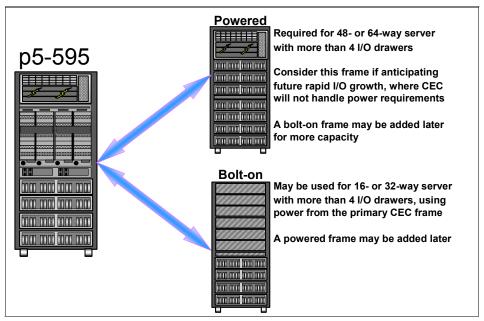

For additional capacity, either a powered or non-powered frame can be configured for a p5-595, as shown in .

Figure 1-2 Powered and bolt on frames

The p5-590 can be expanded by an optional bolt-on frame.

Every p5-590 and p5-595 server comes standard with Advanced POWER Virtualization, providing Micro-Partitioning, Virtual I/O Server, and Partition Load Manager (PLM). Micro-Partitioning enables system configurations with more partitions than processors. Processing resources can be allocated in units as small as 1/10th of a processor and be fine-tuned in increments of 1/100th of a processor. So a p5-590 or p5-595 system can define up to ten *virtual servers* per processor (maximum of 254 per system), controlled in a shared processor pool for automatic, non-disruptive resource balancing. Virtualization features of the p5-590 and the p5-595 are introduced in Chapter 3, "POWER5 virtualization capabilities" on page 55.

The ability to communicate between partitions using virtual Ethernet is part of the Advanced POWER Virtualization feature and it is extended with the Virtual I/O Server to include shared Ethernet adapters. Also part of the Virtual I/O Server is virtual SCSI for sharing SCSI adapters and the attached disks.

The Virtual I/O Server requires APAR IY62262 and is supported by AIX 5L Version 5.3 with APAR IY60349, as well as by SLES 9 and RHEL AS 3. Also included in Advanced POWER Virtualization is PLM, a powerful policy based tool for automatically managing resources among LPARs running AIX 5L Version 5.3 or AIX 5L Version 5.2 with the 5200-04 Recommended Maintenance package.

IBM @server p5 590 and p5 595 servers also offer optional Capacity on Demand (CoD) capability for processors and memory. CoD functionality is outlined in Chapter 4, "Capacity on Demand" on page 83.

IBM @server p5 590 and p5 595 servers provide significant extensions to the mainframe-inspired reliability, availability, and serviceability (RAS) capabilities found in IBM @server p5 and pSeries systems. They come equipped with multiple resources to identify and help resolve system problems rapidly. During ongoing operation, error checking and correction (ECC) checks data for errors and can correct them in real time. First Failure Data Capture (FFDC) capabilities log both the source and root cause of problems to help prevent the recurrence of intermittent failures that diagnostics cannot reproduce. Meanwhile, Dynamic Processor Deallocation and dynamic deallocation of PCI bus slots help to reallocate resources when an impending failure is detected so applications can continue to run unimpeded. RAS function is discussed in Chapter 6, "Reliability, availability, and serviceability" on page 137.

Power options for these systems are described in Section 5.2.10, "Rack, power, and battery backup configuration rules" on page 128.

A description of RAS features, such redundant power and cooling, can be found in Section 6.4, "Redundancy in components" on page 144.

The following sections detail some of the technologies behind the p5-590 and p5-595.

#### 1.3.1 Microprocessor technology

The IBM POWER4 microprocessor, which was introduced in 2001, was a result of advanced research technologies developed by IBM to create a high-performance, high-scalability chip design to power future IBM @server systems. The POWER4 design integrates two processor cores on a single chip, a shared second-level cache, a directory for an off-chip third-level cache, and the

necessary circuitry to connect it to other POWER4 chips to form a system. The dual-processor chip provides natural thread-level parallelism at the chip level.

The POWER5 microprocessor is IBMs second generation dual core microprocessor and extends the POWER4 design by introducing enhanced performance and support for a more granular approach to computing. The POWER5 chip features single- and multi- threaded execution and higher performance in the single-threaded mode than the POWER4 chip at equivalent frequencies.

The primary design objectives of the POWER5 microprocessor are:

- ► Maintain binary and structural compatibility with existing POWER4 systems

- Enhance and extend symmetric multiprocessing (SMP) scalability

- Continue to provide superior performance

- Deliver a power efficient design

- Enhance reliability, availability, and serviceability

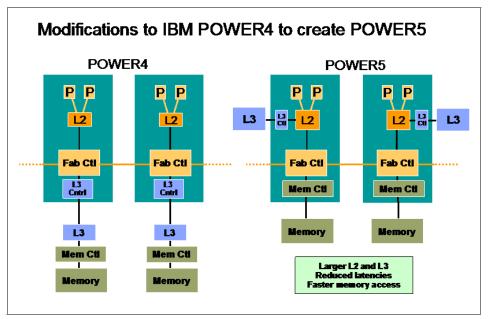

#### **POWER4 to POWER5 comparison**

There are several major differences between POWER4 and POWER5 chip designs, and they include the following areas shown in Figure 1-3, and as discussed in the following sections:

|                                                                        | POWER4+ design                                 | POWER5 design                                       | Benefit                                              |  |

|------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|--|

| L1 cache                                                               | 2-way associative                              | 4-way associative                                   | Improved L1 cache performance                        |  |

| L2 cache                                                               | 8-way associative<br>1.5MB                     | 10-way associative<br>1.9MB                         | Fewer L2 cache misses<br>Better performance          |  |

| L3 cache                                                               | 32MB<br>8-way associative<br>118 clock cycles  | 36MB<br>12-way associative<br>Reduced latency       | Better cache performance                             |  |

| Simultaneous<br>multi-threading                                        | No                                             | Yes                                                 | Better processor utilization 30%* system improvement |  |

| Partitioning support                                                   | 1 processor                                    | 1/10 <sup>th</sup> of processor                     | Better usage of processor resources                  |  |

| Floating-point rename registers                                        | 72                                             | 120                                                 | Better performance                                   |  |

| Chip interconnect:<br>Type<br>Intra MCM data bus<br>Inter MCM data bus | Distributed switch ½ proc. speed ½ proc. speed | Enhanced dist. switch Processor speed ½ proc. speed | Better systems throughput<br>Better performance      |  |

| Size                                                                   | 412mm <sup>2</sup>                             | 389mm²                                              | 50% more transistors in the same space               |  |

Figure 1-3 POWER4 and POWER5 architecture comparison

#### Introduction to simultaneous multi-threading

Simultaneous multi-threading is a hardware design enhancement in POWER5 Architecture that allows two separate instruction streams (threads) to execute simultaneously on the processor. It combines the capabilities of super scaler processors with the latency hiding abilities of hardware multithreading.

Using multiple on-chip thread contexts, the simultaneous multi-threading processor executes instructions from multiple threads each cycle. By duplicating portions of logic in the instruction pipeline and increasing the capacity of the register rename pool, the POWER5 processor can execute several elements of two instruction streams, or threads, concurrently. Through hardware and software thread prioritization, greater utilization of the hardware resources can be realized without an impact to application performance.

The benefit of simultaneous multi-threading is realized more in commercial environments over numeric intensive environments, since the number of transactions performed outweighs the actual speed of the transaction. For example, the simultaneous multi-threading environment would be much better suited for a Web server or database server than it would be for a Fortran weather prediction application. In the rare case that applications are tuned to optimize the use of processor resources and see a decrease in performance due to increased contention to cache and memory, simultaneous multi-threading may be disabled.

Although it is the operating system that determines whether simultaneous multi-threading is used, simultaneous multi-threading is otherwise completely transparent to the applications and operating system, and implemented entirely in hardware.

#### 1.3.2 Memory subsystem

With the enhanced architecture of larger 7.6 MB L2 and 144 MB L3 caches, each mutichip module (MCM) can stage information more effectively from processor memory to applications. These caches allow the p5-590 and p5-595 to run workloads significantly faster than predecessor servers.

The difference of memory hierarchy between POWER4 and POWER5 systems is represented in Figure 1-4 as follows:

Figure 1-4 POWER4 and POWER5 memory structure comparison

There are two types of memory technologies offered, namely DDR1 and DDR2. Equipped with 8 GB of memory in its minimum configuration, the p5-590 can be scaled to 1 TB using DDR1 266 MHz memory. From 8 GB to 128 GB of DDR2 533 MHz memory, useful for high-performance applications, is available. The p5-595 can be scaled from 8 GB to 2 TB of DDR1 266 MHz memory; From 8 GB to 256 GB of DDR2 533 MHz memory (at the time of writing).

Additional information about memory can be found in Chapter 2.3, "Memory subsystem" on page 26 and Section 5.2.4, "Memory configuration rules" on page 121.

#### 1.3.3 I/O subsystem

Using the RIO-2 ports in the processor books, up to twelve I/O drawers can be attached to a p5-595 and up to eight I/O drawers to the p5-590, providing up to 9.3 TB and 14 TB of 15 K RPM disk storage, respectively. Each 4U (4 EIA unit) drawer provides 20 hot plug, blind-swap PCI-X I/O adapter slots, 16 front-accessible, hot-swappable disk drive bays and four integrated Ultra3 SCSI controllers. I/O drawers can be installed in the primary 24-inch rack or in an optional expansion rack. Attachment to a wide range of IBM TotalStorage storage system offerings – including disk storage subsystems, storage area network components, tape libraries, and external media drives – is also supported.

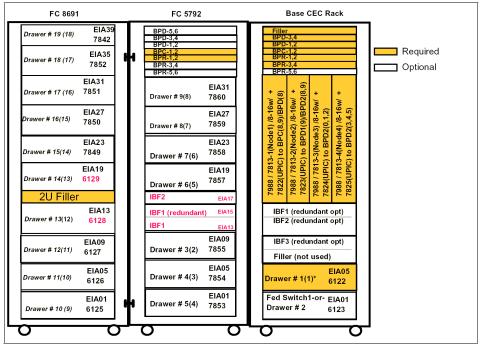

A minimum of one I/O drawer (FC 5791 or FC 5794) is required per system. I/O drawer FC 5791 contains 20 PCI-X slots and 16 disk bays, and FC 5794 contains 20 PCI-X slots and 8 disk bays. Existing 7040-61D I/O drawers may also be attached to a p5-595 or p5-590 servers as additional I/O drawers (when correctly featured). For more information on the I/O system, refer to Chapter 2.7, "I/O drawer" on page 35. The I/O features are shown in Figure 1-5.

Figure 1-5 p5-590 and p5-595 I/O drawer organization

#### 1.3.4 Virtualization

The IBM Virtualization Engine can help simplify IT infrastructure by reducing management complexity and providing integrated virtualization technologies and systems services for a single IBM @server p5 server or across multiple server platforms. It brings together existing offerings and new technologies. The IBM Virtualization Engine systems technologies added or enhanced the systems using the POWER5 Architecture are as follows:

#### ► POWER Hypervisor

Is responsible for time slicing and dispatching the logical partition workload across the physical processors. The POWER Hypervisor also enforces partition security, and can provide Virtual LAN channels between partitions, reducing the need for physical Ethernet adapters using I/O adapter slots.

#### ► Simultaneous multi-threading

Allows two separate instruction streams (threads) to run concurrently on the same physical processor, improving overall throughput and improving overall hardware resource utilization.

#### ► Dynamic LPAR

Allows system resources (processors, memory, and I/O adapters and attached devices) to be grouped logically into separate systems within the same server.

#### Micro-Partitioning

Allows processor resources to be allocated to partitions in units as small as 1/10th of a processor, with increments in units of 1/100th of a processor.

#### ▶ Virtual I/O

Includes Virtual SCSI for sharing SCSI attached disks and virtual networking to enable sharing of Ethernet adapters.

#### Virtual LAN (VLAN)

Enables high-speed, secure, partition-to-partition communications using the TCP/IP protocol to help improve performance.

#### Capacity on Demand

Allows system resources such as processors and memory to be made available on an as-needed basis.

#### Multiple operating system support

The POWER5 processor-based @server p5 products supports IBM AIX 5L Version 5.2, IBM AIX 5L Version 5.3, SUSE Linux Enterprise Server 9 (SLES9), and Red Hat Enterprise AS Linux 3 (RHEL AS 3). IBM i5/OS V5R3 is also available on @server p5 models 570, 590, and 595.

A detailed description of these features can be found in Chapter 3, "POWER5 virtualization capabilities" on page 55.

### 1.4 Features summary

Table 1-1 summarizes the major features of the p5-590 and p5-595 servers. For mroe information, see Appendix A, "Facts and features reference" on page 245.

Table 1-1 p5-590 and p5-595 features summary

| IBM @server p5 system                                             | p5-590                                                                                                               | p5-595           |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------|--|

| Machine type - Model                                              | 9119-590                                                                                                             | 9119-595         |  |

| Packaging                                                         | 24-inch system frame                                                                                                 |                  |  |

| Number of expansion frames                                        | 1                                                                                                                    | 1 or 2           |  |

| Number of processors per system                                   | 8 to 32                                                                                                              | 16 to 64         |  |

| POWER5 processor speed                                            | 1.65 GHz                                                                                                             | 1.65 or 1.90 GHz |  |

| Number of 16-way processor books (2 MCMs per book)                | 1 or 2                                                                                                               | 1, 2, 3, or 4    |  |

| Memory                                                            | 8 GB - 1024 GB*                                                                                                      | 8 GB - 2048 GB*  |  |

| CoD features ( All memory CoD features apply to DDR1 memory only) | Processor/Memory CUoD<br>Reserve CoD<br>On/Off Processor/Memory CoD<br>Trial Processor/Memory CoD<br>Capacity BackUp |                  |  |

| Maximum micro-partitions                                          | 10 times the number of processors (254 maximum)                                                                      |                  |  |

| PCI-X slots                                                       | 20 per I/O drawer                                                                                                    |                  |  |

| Media bays                                                        | Optional                                                                                                             |                  |  |

| Disk bays                                                         | 16 per I/O drawer                                                                                                    |                  |  |

| Optional I/O drawers                                              | Up to 8                                                                                                              | Up to 12         |  |

| Maximum PCI-X slots with maximum I/O drawers                      | 160                                                                                                                  | 240              |  |

| Maximum disk bays with maximum I/O drawers                        | 128                                                                                                                  | 192              |  |

| Maximum disk storage maximum with I/O drawers                     | 9.3 TB                                                                                                               | 14.0 TB          |  |

<sup>\* 32</sup> GB memory cards to enable maximum memory are planned for availability April 8, 2005. Until that time, maximum memory is half as much (512 GB on p5-590 and 1024 GB on p5-595).

#### 1.5 Operating systems support

All new POWER5 processor-based servers are capable of running IBM AIX 5L Version 5.3 or AIX 5L Version 5.2 for POWER and support appropriate versions of Linux. Both of the aforementioned supported versions of AIX 5L have been specifically developed and enhanced to exploit and support the extensive RAS features on IBM @server pSeries systems. Table 1-2 lists operating systems compatibility.

Table 1-2 p5-590 and p5-595 operating systems compatibility

| Operating system                                              | p5-590 | p5-595 |

|---------------------------------------------------------------|--------|--------|

| AIX 5L V5.1                                                   | No     | No     |

| AIX 5L V5.2(5765-E62)                                         | Yes    | Yes    |

| AIX 5L V5.3(5765-G03)                                         | Yes    | Yes    |

| AIX 5L LPAR                                                   | Yes    | Yes    |

| Red Hat Enterprise Linux AS 3 for POWER (5639-RDH)            | Yes    | Yes    |

| SUSE LINUX Enterprise Server 8                                | No     | No     |

| SUSE LINUX Enterprise Server 9 for POWER (5639-SLP)           | Yes    | Yes    |

| Linux LPAR                                                    | Yes    | Yes    |

| i5/OS                                                         | Yes    | Yes    |

| HACMP for AIX 5L V5.2 (5765-F62)                              | Yes    | Yes    |

| Cluster Systems Management for AIX 5L V1.4 (5765-F67)         | Yes    | Yes    |

| Cluster Systems Management for Linux on POWER V1.4 (5765-G16) | Yes    | Yes    |

<sup>&</sup>lt;sup>1</sup>Many of the features described in this document are operating system dependent and may not be available on Linux. For more information, check: http://www.ibm.com/servers/eserver/pseries/linux/whitepapers/linux\_pseries.html

#### 1.5.1 AIX 5L

The p5-590 and p5-595 requires AIX 5L Version 5.3 or AIX 5L Version 5.2 Maintenance Package 5200-04 (IY56722) or later.

The system requires the following media:

- AIX 5L for POWER V5.2 5765-E62, dated 08/2004, or later (CD# LCD4-1133-04) plus APAR IY60347 (Required AIX 5.2 updates for @server p5 590/595)

- AIX 5L for POWER Version 5.3 5765-G03, dated 08/2004, or later.

(CD# LCD4-7463-00) with APAR IY60349 (Required AIX 5.3 updates for @server p5 590/595)

IBM periodically releases maintenance packages for the AIX 5L operating system. These packages are available on CD-ROM (FC 0907) and can be downloaded from the Internet at:

http://www.ibm.com/servers/eserver/support/pseries/aixfixes.html

You can also get individual operating system fixes and information about obtaining AIX 5L service at this site. AIX 5L Version 5.3 has the Service Update Management Assistant (SUMA) tool, which helps the administrator to automate the task of checking and downloading operating system downloads.

The Advanced POWER Virtualization feature is not supported on AIX 5L Version 5.2. AIX 5L Version 5.3 is required to take full advantage of Advanced POWER Virtualization feature.

#### 1.5.2 Linux

For the p5-590 and p5-595, Linux distributions are available through SUSE and Red Hat at the time this publication was written. The p5-590 and p5-595 requires the following version of Linux distributions:

- SUSE LINUX Enterprise Server 9 for POWER, or later

- ▶ Red Hat Enterprise Linux AS 3 for POWER, or later

The Advanced POWER Virtualization feature, DLPAR, and other features require SUSE SLES 9.

In Japan, Turbolinux is also available. In the Latin America sales region, Conectiva is also available. For related information and an overview, see:

http://www.ibm.com/servers/eserver/pseries/linux

Find full information about Red Hat Enterprise Linux AS 3 for POWER at:

http://www.redhat.com/software/rhel/as/

Find full information about SUSE Linux Enterprise Server 9 for POWER at:

http://www.suse.com/us/business/products/server/sles/i pseries.html

For information about UnitedLinux for pSeries from Turbolinux, see:

```

http://www.turbolinux.co.jp

```

For the latest in IBM Linux news, subscribe to the Linux Line. See:

```

https://www6.software.ibm.com/reg/linux/linuxline-i

```

Many of the features that are described in this document are OS-dependent and may not be available on Linux. For more information, check:

```

\verb|http://www.ibm.com/servers/eserver/pseries/linux/whitepapers/linux_pseries.| \\ \verb|html| \\

```

IBM only supports the Linux systems of customers with a SupportLine contract that covers Linux. Otherwise, the Linux distributor should be contacted for support.

# 2

# Hardware architecture

This chapter reviews the contents in Chapter 1, "System overview" on page 1, but provides deeper technical descriptions of the topics, including hardware architectures that are implemented in the p5-590 and p5-595 servers, the POWER5 processor, memory subsystem, and I/O subsystem in the following topics:

- ► Section 2.1, "Server overview" on page 18

- ► Section 2.2, "The POWER5 microprocessor" on page 18

- ► Section 2.3, "Memory subsystem" on page 26

- ► Section 2.4, "Central electronics complex" on page 29

- ► Section 2.5, "System flash memory configuration" on page 34

- ► Section 2.6, "Vital product data and system smart chips" on page 35

- ► Section 2.7, "I/O drawer" on page 35

### 2.1 Server overview

The IBM @server p5 595 and p5 590 provides an expandable, high-end enterprise solution for managing the computing requirements needed to become an on demand business. With the introduction of the POWER5 Architecture, there has been numerous improvements over the previous POWER4 architecture based systems.

Both the p5-590 and p5-595 are rack-based servers, based on the same 24-inch wide, 42 EIA height rack. Inside this rack all the server components are placed in predetermined positions. This design and mechanical organization offers advantages in optimization of floor space usage.

The p5-595 is a 16/32/48/64-way (at 1.9 GHz or 1.65 GHz) SMP system packaged in a 24-inch wide 18 EIA by 36 inch deep CEC. The CEC is installed in the 42 EIA base primary rack that also include two top mounted front and back bulk power assemblies (BPAs) and support for up to four I/O drawers. A powered I/O rack (FC 5792) and a bolt-on expansion frame (FC 8691) is also available to support additional I/O drawers for the p5-595 system. Up to 12 I/O drawers can be attached to a p5-595.

The p5-590 has identical architecture with p5-595. It differs from p5-595 in the following areas:

- Only 1.65 GHz processor are support in a p5-590.

- ► The maximum configuration is a 32-way system with up to eight I/O drawers.

- ► A powered I/O rack (FC 5792) is not required in the p5-590.

# 2.2 The POWER5 microprocessor

The POWER5 processor features single-threaded and multi-threaded execution, providing higher performance in the single-threaded mode than its POWER4 predecessor provides at equivalent frequencies. The POWER5 microprocessor maintains both binary and architectural compatibility with existing POWER4 systems to ensure that binaries continue executing properly and that all application optimizations carry forward to newer systems. The POWER5 microprocessor provides additional enhancements such as virtualization, simultaneous multi-threading support, improved reliability, availability, and serviceability at both chip and system levels, and it has been designed to support interconnection of 64 processors along with higher clock speeds.

Figure 2-1 shows the high-level structures of POWER4 and POWER5 processor-based systems. The POWER4 processors scales up to a 32-way

symmetric multi-processor. Going beyond 32 processors with POWER4 Architecture could increase interprocessor communication, resulting in higher traffic on the interconnection fabric bus. This can cause greater contention and negatively affect system scalability.

Moving the L3 cache reduces traffic on the fabric bus and enables POWER5 processor-based systems to scale to higher levels of symmetric multi-processing. The POWER5 processor supports a 1.9 MB on-chip L2 cache, implemented as three identical slices with separate controllers for each. Either processor core can independently access each L2 controller. The L3 cache, with a capacity of 36 MB, operates as a backdoor with separate buses for reads and writes that operate at half processor speed.

Because of the higher transistor density of the POWER5 0.13-µm technology, it was possible to move the memory controller on-chip and eliminate a chip that was previously needed for the memory controller function. These changes in the POWER5 processor also have the significant side benefits of reducing latency to the L3 cache and main memory, as well as reducing the number of chips that are necessary to build a system.

The POWER5 processor supports the 64-bit PowerPC architecture. A single die contains two identical processor cores, each supporting two logical threads. This architecture makes the chip appear as a four-way symmetric multi-processor to the operating system. The POWER5 processor core has been designed to support both enhanced simultaneous multi-threading and single-threaded (ST) operation modes.

Figure 2-1 POWER4 and POWER5 system structures

### 2.2.1 Simultaneous multi-threading

As a permanent requirement for performance improvements at the application level, simultaneous multi-threading functionality is embedded in the POWER5 chip technology. Developers are familiar with process-level parallelism (multi-tasking) and thread-level parallelism (multi-threads). simultaneous multi-threading is the next stage of processor for achieving higher processor utilization for throughput-oriented applications to introduce the method of instruction group-level parallelism to support multiple pipelines to the processor. The instruction groups are chosen from different hardware threads belonging to a single OS image.

simultaneous multi-threading is activated by default when an OS that supports it is loaded. On a 2-way POWER5 processor-based system, the operating system discovers the available processors as a 4-way system. To achieve a higher performance level, simultaneous multi-threading is also applicable in Micro-Partitioning, capped or uncapped, and dedicated partition environments.

Simultaneous multi-threading is supported on POWER5 processor-based systems running AIX 5L Version 5.3 or Linux-based systems at a required 2.6 kernel. AIX provides the **smtct1** command that turns simultaneous multi-threading on and off without subsequent reboot. For Linux, an additional boot option must be set to activate simultaneous multi-threading after a reboot.

The simultaneous multi-threading mode increases the usage of the execution units. In the POWER5 chip, more rename registers have been introduced (both Floating Point registers (FPR) and general-purpose registers (GPR) are increased to 120), that are essential for out-of-order execution and vital for the simultaneous multi-threading.

### **Enhanced simultaneous multi-threading features**

To improve simultaneous multi-threading performance for various workload mixes and provide robust quality of service, POWER5 provides two features:

Dynamic resource balancing

The objective of dynamic resource balancing is to ensure that the two threads executing on the same processor flow smoothly through the system.

Depending on the situation, the POWER5 processor resource balancing logic has a different thread throttling mechanism.

► Adjustable thread priority

Adjustable thread priority lets software determine when one thread should have a greater (or lesser) share of execution resources.

The POWER5 processor supports eight software-controlled priority levels for each thread.

### Single threaded operation