# **Programmer's Guide** to the mach32 Registers

Information in this document is proprietary and confidential.

### **Technical Reference Manuals**

P/N: REG688000-15

ATI Technologies Inc. 3761 Victoria Park Ave. Scarborough, Ontario Canada M1W 3S2

User Support: 416-756-0711 Offices:

416-756-0718 416-756-0720 416-756-4591 Fax: BBS:

Perfecting the PC

P/N: REG688000-15 Release 1.5

© Copyright 1992, 1993 ATI Technologies, Inc.

The information contained in this document has been carefully checked and is believed to be entirely reliable. No responsibility is assumed for inaccuracies. ATI reserves the right to make changes at any time to improve design and supply the best product possible.

All rights reserved. This document is subject to change without notice and is not to be reproduced or distributed in any form or by any means without prior permission in writing from ATI Technologies Inc.

ATI, VGAWonder, mach8, mach32, 8514-ULTRA, GRAPHICS ULTRA, GRAPHICS VANTAGE, GRAPHICS ULTRA+, and GRAPHICS ULTRA PRO are trademarks of ATI Technologies Inc. All other trademarks and product names are properties of their respective owners.

- Graphics Accelerators

User's Guide

- •Graphics Ultra Pro User's Guide

- •Graphics Ultra + User's Guide

- •mach32 Graphics Controller Specifications (GCS688xxx-xx)

- •Programmer's Guide to the *mach32* Registers (REG688000-xx)

- Graphics Accelerators and VGA BIOS Kits (BIO688000-xx)

- Programmer's Guide to the *mach32* Adapter Interface (AIF688000-xx)

## **Record of Revisions**

| Release | Date  | Description of changes                                                                          |

|---------|-------|-------------------------------------------------------------------------------------------------|

| 1.0     | 92-06 | Original release.                                                                               |

| 1.1     | 92-06 | Reprinted with minor, typographical changes.                                                    |

| 1.2     | 92-07 | Reprinted with minor, typographical changes.                                                    |

| 1.21    | 92-12 | Registers 46E8h-W, 12EEh-R, 16EEh-R revised.                                                    |

| 1.3     | 93-03 | Reprinted with minor, typographical changes.                                                    |

| 1.4     | 93-03 | ATI68800 "LX", "-6" and "AX" updates.                                                           |

| 1.5     | 93-05 | PCI updates — 22EE-RW, 32EE-RW, 36EE-RW, 5EEE-RW, 62EE-W, 6AEE-RW, and configuration registers. |

| PA | RTI                          |      |

|----|------------------------------|------|

| 1. | Introduction                 | 1-1  |

|    | About This Manual            | 1-   |

|    | Features                     | 1-   |

|    | Notation Convention          | 1-3  |

| 2. | Programmer's Overview        | 2-3  |

|    | Overview                     | 2-   |

|    | Power On Setup Registers     | 2-3  |

|    | PCI Configuration Registers  | 2-8  |

| PA | RT II                        |      |

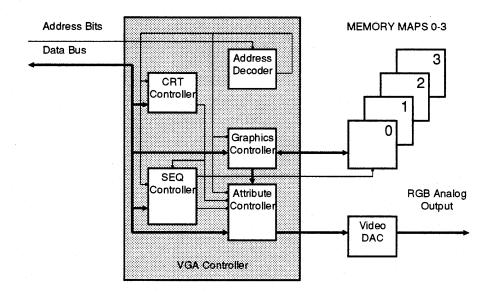

| 3. | VGA Controller               | 3-1  |

|    | Overview                     | 3-1  |

|    | Functional Blocks            | 3-3  |

|    | Address Decoder              | 3-3  |

|    | Sequencer Controller         | 3-3  |

|    | CRT Controller               | 3-4  |

|    | Graphics Controller          | 3-4  |

|    | Attribute Controller         | 3-4  |

|    | VGA Display Modes            | 3-4  |

|    | VGA Alphanumeric Modes (A/N) | 3-5  |

|    | VGA Graphics Modes (APA)     | 3-7  |

|    | Display Mode Specifications  | 3-10 |

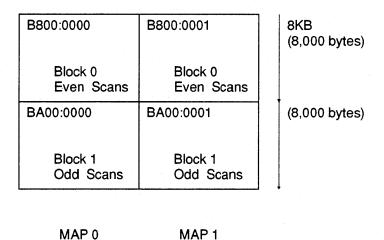

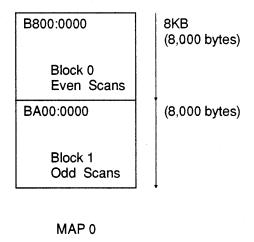

| 4. | VGA Memory Organization      | 4-1  |

|    | Overview                     | 4-1  |

|    | Memory Maps                  | 4-2  |

| 5. | VGA-Compatible Registers     | 5-1  |

|    | Overview                     | 5-1  |

#### Table of Contents

|    | VGA Compatible Registers — by I/O Port |    |     |   |   |   |   |   |   | • |    |   |   | 5-2  |

|----|----------------------------------------|----|-----|---|---|---|---|---|---|---|----|---|---|------|

|    | Register Descriptions                  |    |     | • |   |   |   |   |   |   |    |   |   | 5-4  |

| 6. | VGA Register Extensions                |    | • • | • |   | • |   |   |   |   |    |   |   | 6-1  |

|    | Configuring VGA Extended Registers     |    |     |   |   |   |   |   |   |   |    |   |   | 6-1  |

|    | VGA Extended Registers — by Name .     |    |     |   | • |   | • |   | • | • |    |   | • | 6-2  |

| PA | RT III                                 |    |     |   |   |   |   |   |   |   |    |   |   |      |

| 7. | Coprocessor Functions                  |    |     |   |   |   | • | • |   |   |    |   | • | 7-1  |

|    | Logical Register Groupings             |    |     |   |   |   |   |   |   |   |    |   |   | 7-1  |

|    | Pixel Data Path                        |    |     |   |   |   |   |   |   |   |    |   |   | 7-2  |

|    | CRT Controller                         |    |     |   |   |   |   |   |   |   |    |   |   | 7-3  |

|    | Pixel Transfer ALU                     |    |     |   |   |   |   |   |   |   |    |   |   | 7-4  |

|    | Command FIFO                           |    |     |   |   |   |   |   |   |   |    |   |   | 7-5  |

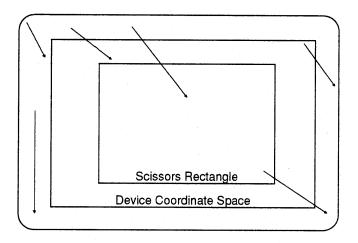

|    | Scissor Registers                      |    |     |   |   |   |   |   |   |   |    |   |   | 7-5  |

|    | Drawing Operations                     |    |     |   |   |   |   |   |   |   |    |   |   | 7-5  |

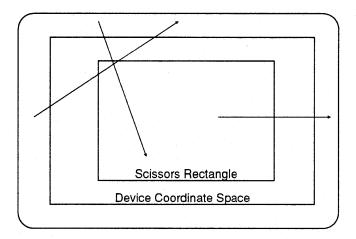

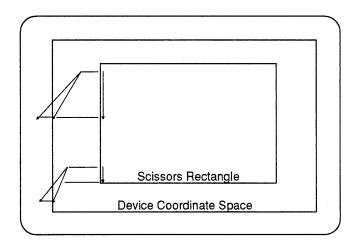

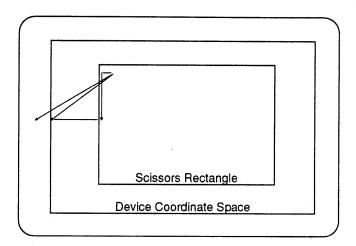

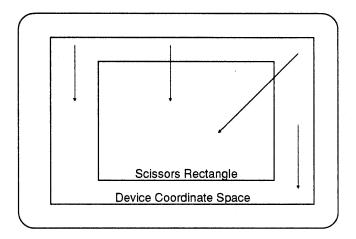

|    | Line Clipping                          |    |     |   |   |   |   |   |   |   |    |   |   | 7-11 |

|    | Off-Screen Memory Management           |    |     |   | ٠ |   |   |   |   |   |    |   |   | 7-12 |

|    | Linear Memory Aperture                 |    |     |   |   |   | • | • |   |   |    |   |   | 7-12 |

|    | Scalable Gray Scale Fonts              |    |     |   |   |   |   |   |   |   |    |   |   | 7-13 |

|    | Mono Pattern                           |    |     |   |   |   |   |   |   |   |    |   |   | 7-13 |

|    | Block Write and 64-Bit Fill Draw       |    |     |   |   |   |   |   |   |   |    | • |   | 7-14 |

|    | Split Transfer Cycle                   | •  |     |   |   |   |   |   |   |   |    |   |   | 7-15 |

|    | Separate Display/Drawing Pixel Sizes   |    |     |   |   |   |   |   |   |   |    |   | • | 7-15 |

|    | Memory Mapped Registers                |    |     |   |   |   |   |   |   |   |    |   |   | 7-16 |

|    | FIFO Discipline                        |    |     |   |   |   |   |   |   |   |    |   |   | 7-16 |

| 8. | 8514/A-Compatible Coprocessor Register | rs |     |   |   |   |   |   |   |   |    |   |   | 8-1  |

|    | DAC Operations                         |    |     |   |   |   |   |   |   |   |    |   |   | 8-1  |

|    | CRT Operations                         |    |     |   |   |   |   |   |   |   |    |   |   |      |

|    | Engine Control                         |    |     | • |   |   |   |   |   |   | ٠. |   |   | 8-13 |

|    | Drawing Control                        |    |     |   |   |   |   |   |   |   |    |   |   | 8-21 |

| 9. | Coprocessor Register Extensions        |    |     |   |   |   |   |   |   |   | •  |   |   | 9-1  |

|    | CRT Control                            |    |     |   |   |   |   |   |   |   |    |   |   |      |

|    | Engine Setup                           |    |     |   |   |   |   |   |   |   |    |   |   |      |

|    | Engine Control                         |    |     |   |   |   |   |   |   |   |    |   |   |      |

|    | Drawing Operations                     |    |     |   |   |   |   |   |   |   |    |   |   |      |

|    | Overview                              |   |   |    |   |   |   |   |   |   | •  |    |   |   |     | 9-26 |

|----|---------------------------------------|---|---|----|---|---|---|---|---|---|----|----|---|---|-----|------|

|    | General Drawing Control Registers .   |   |   |    |   |   |   |   |   |   |    |    |   |   |     | 9-27 |

|    | Scissor Registers                     |   |   |    |   |   |   |   |   |   |    |    |   |   |     | 9-27 |

|    | Direct Linedraw Registers             |   |   |    |   |   |   |   |   |   |    |    |   |   |     | 9-37 |

|    | Extended Short-Stroke Vector Register |   |   |    |   |   |   |   |   |   |    |    |   |   |     | 9-37 |

|    | Raw Bresenham Linedraw Registers .    | • |   |    |   |   |   |   |   |   |    | •  |   |   |     | 9-37 |

|    | Blit Registers                        |   |   |    |   |   |   |   |   |   |    |    |   |   |     | 9-38 |

|    | Miscellaneous Drawing Commands .      |   |   |    |   |   |   |   |   |   |    |    |   |   | •   | 9-46 |

|    | Pattern Registers                     |   |   |    |   |   |   |   | • |   | •  |    |   |   |     | 9-46 |

|    | Pixel Transfer Control Registers      |   |   |    | • |   |   |   | • |   | •  |    |   |   |     | 9-46 |

|    | Pixel Transfer Function Registers     |   |   |    |   |   |   |   |   |   |    |    |   |   |     | 9-46 |

|    | Pixel Transfer Registers              |   |   |    |   |   |   | • |   |   | •  |    |   |   |     | 9-47 |

|    | Status Registers                      |   |   |    |   |   |   |   |   |   | ٠. |    |   |   |     | 9-63 |

|    | Overscan                              |   |   |    |   |   | • | • |   |   |    | •  | • |   | •   | 9-70 |

|    | Memory Boundary                       | • |   |    |   |   |   |   |   |   | •  |    |   |   |     | 9-74 |

|    | Memory Interface                      |   | • |    |   |   |   | • |   |   | •  |    |   | • | • , | 9-75 |

|    | Hardware Cursor                       |   |   |    |   |   |   | • | • | • |    |    |   |   |     | 9-77 |

|    | Cursor Definition Mapping             | · |   |    |   |   |   |   |   |   |    |    |   |   |     | 9-78 |

|    | Miscellaneous Registers               |   |   |    |   | • |   |   |   |   |    |    |   |   |     | 9-83 |

|    | DAC Registers                         |   |   | ٠. |   |   |   |   | • |   |    | •  |   |   |     | 9-90 |

|    |                                       |   |   |    |   |   |   |   |   |   |    |    |   |   |     |      |

| AP | PENDIXES                              |   |   |    |   |   |   |   |   |   |    |    |   |   |     |      |

| A. | Coprocessor Registers                 |   |   |    |   |   |   |   | • |   |    |    |   |   |     | A-1  |

| B. | BIOS Interface                        |   |   |    |   |   |   |   |   |   |    |    |   |   |     | B-1  |

| C. | EEPROM Map                            | • |   |    |   |   | • |   |   |   | •  |    |   |   |     | C-1  |

|    | CRT Parameters                        |   |   |    |   |   |   |   |   |   |    |    |   |   |     | D-1  |

|    | Pixel Clock Specifications            |   |   |    |   |   |   |   |   |   |    |    |   |   |     | E-1  |

| F. | RAMDAC Programming                    |   |   |    |   |   |   |   |   |   |    |    |   |   |     | E-1  |

|    |                                       |   |   |    |   |   |   |   |   |   |    |    |   |   |     |      |

|    | ATI68800-6 and ATI68800LX Features    |   |   |    |   |   |   |   |   |   |    |    |   |   |     | G-1  |

| H. | ATI68800AX Features                   |   |   |    | • |   |   |   |   |   |    | ١. |   |   |     | H-1  |

This page intentionally left blank.

# Part I

| - 발표 회사 전에 발표한 경험 프로그램 프로그램 프로그램 및 경험 및 경                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                     |

| - 보기 보고 보는 경기에 가고 있다. 보고 있는 것이 보고 하면 가는 것이 되는 것이 되었다. 그 보고 있는 것이 되었다.<br>- 보고 있는 것이 살으로 그렇게 되는 것으로 가고 있다. 그런 것이 되는 것이 있는 모두 하는 것이 되었다. 하는 것이 되었다. 보고                                                                                                                                                                                                |

| 는 최근 현실 사용 전에 발생하는 하는 하는 이 보다는 사용을 받아 하는 사용을 받아 보고 있다. 그는 사용이 들어 가는 사용이 들어 보고 보고 있다.<br>- 회사 보통을 찾아 하는 사용을 받아 되었는 경소 교육을 하는 사용을 하는 것이다. 그는 사용을 하는 것이 되었다는 것이 없는 사용을 하는 것이다.                                                                                                                                                                         |

| 도 있다면 하다는 사람들은 사용 전로 관련하다. 그리고 하는 나라고 불량하는 그로 그런 사용하는 그들은 이 유명이라고 하는 것이 없었다. 그는 사용하는 것이 되었다.<br>- "#REM NOTE 등 "그 그는 다른 사용에 있는 이 이번 기를 만든 그는 사용이를 하는 사람들이 되었다. 그는 사용이 그는 사용이 그는 사용이 나를 받는 것이 하나 없다.                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                     |

| 도 사용하게 되고 있으면 한 것 같은 사용에 가장하여 하게 되고 있으면 하는데 그런데 그는 그는 그는 그는 그는 그를 보고 하는데 함께 하는데 하는데 하는데 하는데 하는데 되었다.<br>- 그렇게 되고 있는데 그릇이 하는데 된다는데 보고 하는데                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                     |

| - 그 사용하는 보다는 전 2015년 전 1일 등에 가장 보는 사용 보다는 보다 있는데 가장 하는 말로 하는데 보다는 것이 되었다. 그렇게 되는데 보다는 보다 보다는 것이다.<br>                                                                                                                                                                                                                                               |

| 는 사용하는 것이 되는 생각을 하는 사용이 가능하는 사용이 되었다. 그는 생각에 가는 생각이 되었다. 그는 사용이 되었다. 그는 사용이 되었다. 그는 사용이 되었다. 그는 사용이 되었다. 그는 사용<br>- 사용이 생각되는 생각이 생각하는 사용이 되었다. 그는 사용이 되었<br>- 사용이 사용이 사용이 사용이 사용이 되었다. 그는 사용이 되었다. 사용이 되었다. 그는 사용이 사용이 사용이 사용이 되었다. 그는 사용이 사용이 사용이 사용이 되었다. 그는 사용이 사용이 되었다. |

| 도 생기는 이 집에 가는 것들은 그 사람들이 되고 있다. 그리고 있는 것이 되었는데 보고 있다. 그런 그리고 있는데 그런데 그런데 그런데 그런데 그런데 그런데 그런데 그런데 그런데 그런                                                                                                                                                                                                                                             |

# Introduction

### About This Manual

This manual is a register description written for OEM designers and developers who wish to integrate ATI's **mach32** graphics controller accelerators in their hardware. It is also written for programmers who wish to program directly to hardware registers to optimize graphics performance. A working knowledge of the 80x86 family of PCs, Assembler, "C", and 2D graphics is assumed.

The contents of this manual cover the following controllers — ATI68800AX, ATI68800-6, ATI68800LX, and ATI68800-3. In general, the "LX" and "AX" are quite similar to the ATI68800-6 — the "LX" is basically a "-6" without VRAM support, the "AX" a "-6" with support for an additional local bus type, PCI. Therefore register descriptions marked as "-6 specific" are equally applicable to both these controllers unless otherwise indicated. (Refer to the appendixes for controller differences.) The registers of these controllers are backward-compatible with the ATI68800-3.

This manual has three parts. The first part contains an introduction and a programmer's overview. Part II describes the VGA controller, the display modes, memory organization, and both VGA-compatible and ATI-extended registers. Part III describes the coprocessor engine, pixel data paths, draw engine functions, and both 8514/A-compatible and ATI-extended registers. Functional and bit-field differences are indicated in the register descriptions (Part III) as well as summarized for each product family in the appendixes (G and H).

#### Features

- Low cost, high performance single chip graphics solution suitable for board or system level implementations

- 100% register-level hardware compatible to the IBM VGA as well as the IBM 8514/A graphics adapter

- I/O Bus Types: ISA (8 and 16 bit), EISA (32 bit), and Microchannel (16-bit and 32-bit)

- Local Buses: 486, 386DX, 386SX, VESA VL-bus, and PCI

- Fully programmable direct memory interface

- Memory Types: VRAM 256Kx4, 256Kx16; DRAM 256Kx4, 256Kx16

- Memory Sizes: 512KB, 1MB, 2MB, 4MB (using VRAM 256Kx16 only)

- Colors/Resolutions:

4 and 8 bpp (Bits Per Pixel) to 1280x1024

16 bpp to 1024x768

24 bpp to 800x600

- High-speed point-to-point line draw; coprocessor supports 16 bpp modes

- Supports memory mapped registers (except ATI68800-3)

- Hardware support for ATI's Crystal Font technology

- Support for overscan monitors in both VGA and 8514/A modes

- Hardware cursor: 64x64x2; XGA function compatible

- High-speed polygon fill

- Hardware assisted line and polygon pre-clipping

- Support for packed bitmap data transfers

- 32 8-bit pixel color pattern registers

- 32 1-bit monochrome pattern registers

- Enhanced bit block transfer (blit) operation to allow for better off-screen memory management

- Extended 16-entry data FIFO

- Improved FIFO status registers providing dramatic improvements in data throughput

- Card ID feature supports up to seven display adapters simultaneously in a system

- 0.7 micron CMOS VLSI technology

- 208-pin PQFP

## **Notation Convention**

Mnemonics are used throughout this manual in place of hardware register names. The naming convention for registers and/or bit fields is as follows:

- Register Mnemonic

- Register\_Mnemonic[Bit\_Numbers or Field\_Name]

The example below is the mnemonic for the Miscellaneous Output register.

#### **GENMO**

The examples below describe the same entity in two different ways — as bits 2 and 3 or as the Clock\_Select field of the GENMO register. Note that *square brackets* are used.

GENMO[3:2] or GENMO[CLOCK\_SELECT]

The convention for naming signals is similar to that used for naming hardware registers.

#### Signal Name

When several signals of an identical function are described, the part of the signalname that differs may be shown in brackets. For example, the four Select signals — SEL0#, SEL1#, SEL2#, and SEL3# — may be represented as follows. Note that *round brackets* are used.

SEL(0:3)#

This page intentionally left blank.

# **Programmer's Overview**

### **Overview**

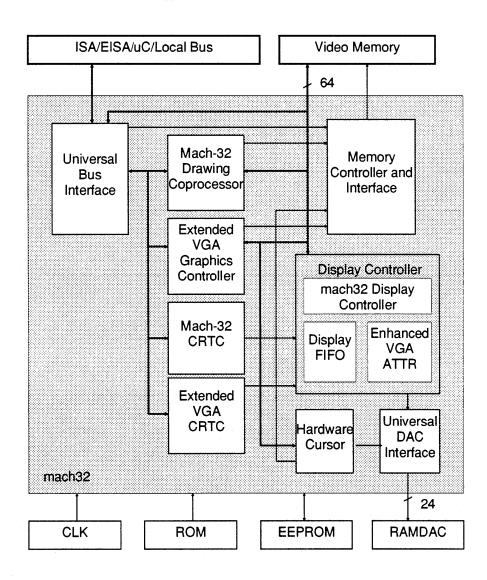

The *mach32* is a VLSI graphics controller chip consisting of an 8514/A-compatible accelerator and a VGA-compatible graphics controller. The accelerator is also known as the coprocessor or the draw engine. This chip may be used to implement board or system level solutions supporting a range of I/O bus types, memory types, memory sizes, screen resolutions, and color depths. In addition the chip supports a number of extended registers and enhancements.

The built-in VGA controller can be disabled to allow the accelerator to co-exist with an alternate external VGA. This manual will concentrate mostly on the programming of the draw engine.

The draw engine is 100% 8514/A-compatible in 4bpp and 8bpp display modes, and is mostly 8514/A-compatible in 16bpp modes. All ATI draw engine extensions are available in 4, 8, and 16bpp modes. The draw engine supports the 16bpp modes in the following RGB weightings — 555, 565, 655, and 664. It supports 24 or 32bpp modes as follows — RGB, BGR, RGBa, and aBGR.

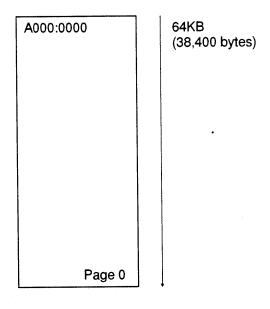

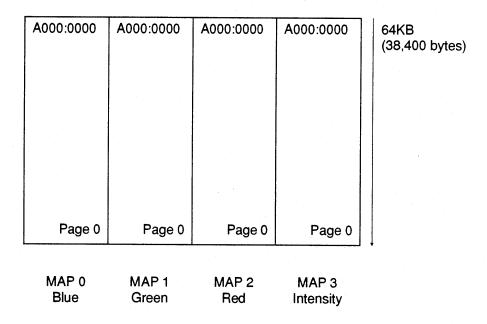

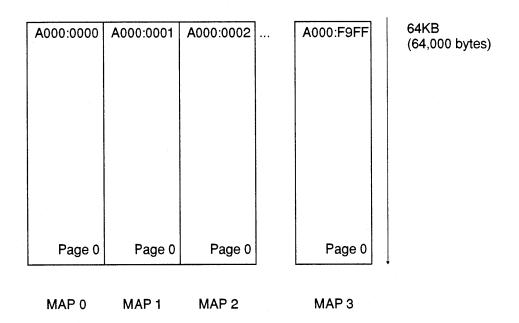

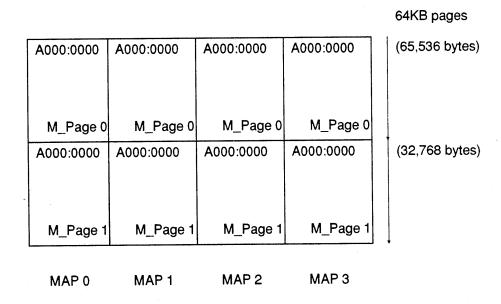

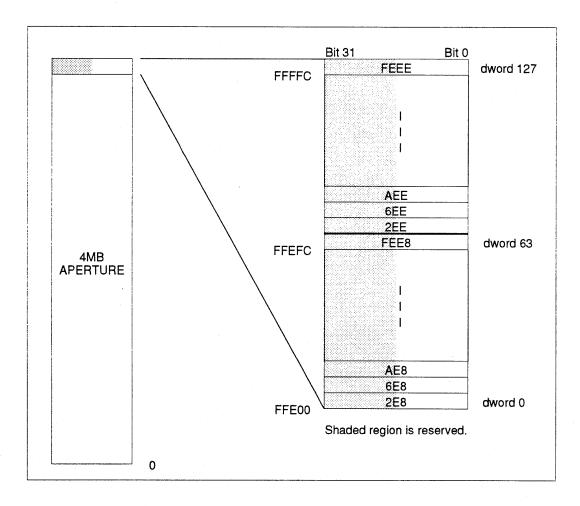

A configurable linear memory aperture is available for all modes, including VGA. It may be configured to 64K paged at A000h or to 1M paged or 4M linear on any 1MB boundary. The aperture is primarily used for increasing throughput on host-to-screen and screen-to-host data transfers. Screen memory can be shared between the VGA and the draw engine. **mach32**-aware applications may re-configure the memory boundary (register) dynamically to give more or less memory to the VGA or the accelerator.

Since *mach32* boards may be equipped with a number of different RAMDACs, a protocol has been established for accelerator mode switching by ROM calls. VGA mode switching is accomplished with the standard INT 10h interface. The VGA and accelerator should be treated as two logically separate entities. Bus type and memory type should be transparent to applications programmers.

A variable size hardware cursor is available for all non-VGA modes. This cursor may be composed of 2 colors, transparent, or complement. It is XGA function compatible.

All I/O writes to the draw engine are written to the 16-word command FIFO. Since standard 8514/A adapters only have an 8-word command FIFO, this draw engine use the FIFO status extensions to poll the state of the eight extra words.

8514/A-compatible draw primitives include rectangle fill, blit, line draw, short stroke vector, and in-place polygon fill. ATI extensions provide for non-conforming rectangle fill, non-conforming blit, point-to-point line draw, line draw, short stroke vector, horizontal raster draw, and blit polyfill. Extended data paths are available for packed monochrome and color patterns in addition to existing color, host, RAM, or monochrome pattern selections. The pixel ALU has 16 logical and 16 arithmetic functions available in 4bpp and 8bpp modes; and 16 logical functions in 16bpp modes.

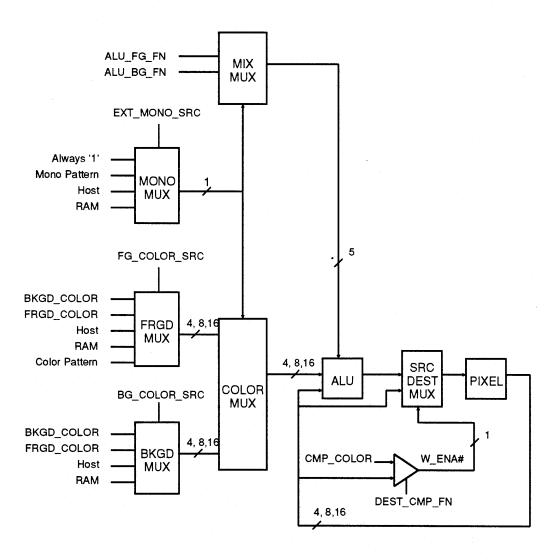

Figure 2-1. Mach32 Drawing Coprocessor

# Power On Setup Registers

## Microchannel POS Registers

POS register addresses for the Microchannel configuration (uC) are from 100h to 105h inclusive. The input signal -CD SETUP must be active for these registers to be accessed.

|        | uC Setup Mode ID Byte 1 Register |                  |                                                                                                                                    |             |         |  |  |  |  |  |  |

|--------|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|--|--|--|--|--|--|

| 0100 ( | (B)                              |                  | SETUP_ID1, uC                                                                                                                      |             |         |  |  |  |  |  |  |

| 0100 ( | (11)                             | VGA              | <b>-</b>                                                                                                                           | -           | Mach 32 |  |  |  |  |  |  |

| Bit    | I                                | <b>I</b> nemonic |                                                                                                                                    | Description |         |  |  |  |  |  |  |

| 7:0    | SET                              | UP_ID1(uC)       | Setup Identification byte 1 is as follows: ATI68800-3 is 89h. ATI68800-6 is 89h. (8Ah when VGA is disabled by external strap bit.) |             |         |  |  |  |  |  |  |

|      | uC Setup Mode ID Byte 2 Register |             |                   |                     |         |  |  |  |  |

|------|----------------------------------|-------------|-------------------|---------------------|---------|--|--|--|--|

| 0101 | (D)                              |             | SETUP_            |                     |         |  |  |  |  |

| 0101 | (n)                              | VGA         | -                 | -                   | Mach 32 |  |  |  |  |

| Bit  |                                  | Mnemonic    |                   | Description         | U       |  |  |  |  |

| 7:0  | SE                               | ΓUP_ID2(uC) | Setup Identificat | tion byte 2 is 80h. |         |  |  |  |  |

|        | uC Setup Mode Option Select Register |            |                                                                                        |             |         |  |  |  |  |  |  |

|--------|--------------------------------------|------------|----------------------------------------------------------------------------------------|-------------|---------|--|--|--|--|--|--|

| 0102 ( | D/W/\                                |            | SETUP_                                                                                 | OPT, uC     |         |  |  |  |  |  |  |

| 0102 ( | 13/00)                               | VGA        | -                                                                                      | -           | Mach 32 |  |  |  |  |  |  |

| Bit    | N                                    | Anemonic   |                                                                                        | Description | ,       |  |  |  |  |  |  |

| 0      | SETU                                 | JP_OPT(uC) | 0 = Video adapter disabled — responds only to POS registers. 1 = Video adapter enabled |             |         |  |  |  |  |  |  |

| 7:1    | -                                    |            | Reserved                                                                               |             |         |  |  |  |  |  |  |

|        | uC ROM Base Address Setup Register |          |                                                                                                           |             |         |  |  |  |  |  |  |

|--------|------------------------------------|----------|-----------------------------------------------------------------------------------------------------------|-------------|---------|--|--|--|--|--|--|

| 0102 ( | 0103 (W) ROM_SETUP, uC             |          |                                                                                                           |             |         |  |  |  |  |  |  |

| 0103 ( | vv)                                | VGA      | -                                                                                                         | -           | Mach 32 |  |  |  |  |  |  |

| Bit    |                                    | Mnemonic |                                                                                                           | Description |         |  |  |  |  |  |  |

| 0      | -                                  |          | 0 = BIOS ROM decodes disabled 1 = BIOS ROM decodes enabled This bit is readable in all except ATI68800-3. |             |         |  |  |  |  |  |  |

| 7:1    |                                    |          |                                                                                                           |             |         |  |  |  |  |  |  |

|         | uC Setup Byte 1 Register |          |             |             |         |  |  |  |  |  |  |

|---------|--------------------------|----------|-------------|-------------|---------|--|--|--|--|--|--|

| 0104 (\ | Λ/\                      |          | SETUP_1, uC |             |         |  |  |  |  |  |  |

| 0104 (  | vv <i>j</i>              | VGA      | -           | -           | Mach 32 |  |  |  |  |  |  |

| Bit     |                          | Mnemonic |             | Description |         |  |  |  |  |  |  |

| 7:0     |                          |          |             |             |         |  |  |  |  |  |  |

|          | uC Setup Byte 2 Register |          |       |             |         |  |  |  |  |  |

|----------|--------------------------|----------|-------|-------------|---------|--|--|--|--|--|

| 0105 (W) |                          |          | SETUP | _2, uC      |         |  |  |  |  |  |

| 0105 (1  | vv <i>j</i>              | VGA      | -     | •           | Mach 32 |  |  |  |  |  |

| Bit      |                          | Mnemonic |       | Description |         |  |  |  |  |  |

| 7:0      |                          |          |       |             |         |  |  |  |  |  |

## EISA Bus POS Registers

POS register address for EISA are from 0zC80h to 0zC87h inclusive. The input signal AEN must be "0" for these registers to be accessed. The "z" in the address represents the bus slot number.

|           | EISA Setup Mode ID Byte 1 Register |                    |                 |           |              |         |  |  |  |  |

|-----------|------------------------------------|--------------------|-----------------|-----------|--------------|---------|--|--|--|--|

| 0zC80     | / <b>P</b> \                       |                    | SETUP_ID1, EISA |           |              |         |  |  |  |  |

| 02000     | (17)                               | VGA                | •               |           | -            | Mach 32 |  |  |  |  |

| Blt       |                                    | Mnemonic           |                 | De        | scription    |         |  |  |  |  |

| 7:0       | SET                                | TUP_ID1(EISA)      | Setup Identifi  | ication b | yte 1 is 06h | •       |  |  |  |  |

| Note: The | "z" in                             | the address is the | bus slot numb   | er.       |              |         |  |  |  |  |

|           |          | EISA Setup         | Mode ID Byte                        | e 2 Register |         |

|-----------|----------|--------------------|-------------------------------------|--------------|---------|

| 0zC81     | (B)      | SETUP_ID2, EISA    |                                     |              |         |

| 02001     | (11)     | VGA                | -                                   | -            | Mach 32 |

| Bit       |          | Mnemonic           |                                     | Description  |         |

| 7:0       | SET      | UP_ID2(EISA)       | Setup Identification byte 2 is 89h. |              |         |

| Note: The | e "z" in | the address is the | e bus slot number.                  |              |         |

|           |          | EISA Setup        | Mode ID By                          | te 3 Register |         |

|-----------|----------|-------------------|-------------------------------------|---------------|---------|

| 0zC82 (R) |          | SETUP_ID3, EISA   |                                     |               |         |

| 02002     | . (n)    | VGA               | •                                   | -             | Mach 32 |

| Bit       |          | Mnemonic          |                                     | Description   |         |

| 7:0       | SET      | UP_ID3(EISA)      | Setup Identification byte 3 is 44h. |               |         |

| Note: Th  | e "z" in | the address is th | e bus slot number                   | •             |         |

| EISA Setup Mode ID Byte 4 Register |      |              |                                                                                                                 |             |         |

|------------------------------------|------|--------------|-----------------------------------------------------------------------------------------------------------------|-------------|---------|

| n-000                              | /D)  |              | SETUP                                                                                                           | ID4, EISA   |         |

| 0zC83 (R)                          |      | VGA          | -                                                                                                               | •           | Mach 32 |

| Bit                                | N    | Inemonic     |                                                                                                                 | Description |         |

| 7:0                                | SETU | JP_ID4(EISA) | Setup Identification byte 4 is as follows: ATI68800-3 is 00h ATI68800LX is 01h ATI68800-6: 01h ATI68800AX: 00h. |             |         |

|      | E               | SA Setup N        | <b>Node Option</b> | <b>Select Registe</b>                             | r             |

|------|-----------------|-------------------|--------------------|---------------------------------------------------|---------------|

| 0zC8 | 34              | SETUP_OPT, EISA   |                    |                                                   |               |

| (R/W | <b>/</b> )      | VGA               | -                  | -                                                 | Mach 32       |

| Bit  | 1               | Mnemonic          |                    | Description                                       |               |

| 0    | SET             | UP_OPT(uC)        | POS regi           | apter disabled — resp<br>isters.<br>apter enabled | oonds only to |

| 7:1  | -               |                   | Reserved           |                                                   |               |

|      | -<br>e "z" in 1 | the address is th | Reserved           | er.                                               | -             |

| EISA ROM Base Address Setup Register |       |         |                 |                                         |         |  |

|--------------------------------------|-------|---------|-----------------|-----------------------------------------|---------|--|

| <b>0-0</b> 05                        | /\A/\ |         | ROM_SETUP, EISA |                                         |         |  |

| 0zC85                                | (vv)  | VGA     | -               | -                                       | Mach 32 |  |

| Bit                                  | M     | nemonic |                 | Description                             |         |  |

| 6:0                                  | -     |         |                 | M base address corress A17:A11, in 8514 |         |  |

| 7                                    | -     |         |                 | A decodes disabled A decodes enabled    |         |  |

|           |   | EISA     | Setup Byte 1 F                                                                 | Register    |                 |

|-----------|---|----------|--------------------------------------------------------------------------------|-------------|-----------------|

| 0zC86 (W) |   |          | SETUP_1, EISA                                                                  |             |                 |

|           |   | VGA      | -                                                                              | -           | Mach 32         |

| Bit       |   | Mnemonic |                                                                                | Description |                 |

| 7:0       | - |          | General purpose R/W register. The value of thi register is read back at 52EEh. |             | e value of this |

|              |   | EISA          | Setup Byte 2 F                                                                  | Register |         |

|--------------|---|---------------|---------------------------------------------------------------------------------|----------|---------|

| 0zC87 (W)    |   | SETUP_2, EISA |                                                                                 |          |         |

|              |   | VGA           | -                                                                               | -        | Mach 32 |

| Bit Mnemonic |   |               | Description                                                                     |          |         |

| 7:0          | - |               | General purpose R/W register. The value of this register is read back at 52EFh. |          |         |

# PCI Configuration Registers

The ATI68800AX *mach32* accelerator supports the Intel Peripheral Component Interconnect (PCI) local bus. Please refer to the *PCI Local Bus Specification* for detailed descriptions of the PCI Configuration Space registers. A brief summary is listed as follows:

| Address | Bits | R/W | Functions                                | Power Up Default                             |

|---------|------|-----|------------------------------------------|----------------------------------------------|

| 0h      | 15:0 | R   | Vendor ID                                | 1002                                         |

| 2h      | 15:0 | R   | Device ID                                | 4158 (AX)                                    |

| 4h      | 0    | R/W | I/O Access Enable                        | 0 (Disabled)                                 |

|         | 1    | R/W | Memory Access Enable                     | 0 (Disabled)                                 |

|         | 2    | R   | Bus Master Enable                        | 0 Always (Disabled)                          |

|         | 3    | R   | Special Cycle Enable                     | 0 Always (Disabled)                          |

|         | 4    | R   | Mem. Write & Invalidate Enable           | 0 Always (Disabled)                          |

|         | 5    | R/W | Palette Snooping Enable                  | 0 (Disabled)                                 |

|         | 6    | R   | Parity Error Enable                      | 0 Always (Disabled)                          |

| -       | 7    | R/W | Read Wait Cycle Control                  | 1 (Add 1WS)                                  |

|         | 8    | R   | SERR# Enable                             | 0 Always (Disabled)                          |

|         | 15:9 | -   | Reserved                                 | 0                                            |

| 6h      | 8:0  | -   | Reserved                                 | 0                                            |

|         | 10:9 | R   | DEVSEL Timing                            | 1 (Medium)                                   |

|         | 11   | R/W | Signalled Target Abort                   | 0 (No Target Abort)                          |

|         | 12   | R   | Received Target Abort                    | 0 Always (Inactive)                          |

|         | 13   | R   | Received Master Abort                    | 0 Always (Inactive)                          |

|         | 14   | R   | Signalled System Error                   | 0 Always (Inactive)                          |

|         | 15   | R   | Parity Error Detected                    | 0 Always (Inactive)                          |

| 8h      | 7:0  | R   | Revised ID                               | 0                                            |

| 9h      | 7:0  | R   | Register-Level Prog. Interface           | 0                                            |

| Ah      | 7:0  | R   | Sub-Class<br>Code/Programmable Interface | 00 (VGA Compat. Device)<br>80 (VGA Disabled) |

| Bh      | 7:0  | R   | Base-Class Code                          | 03 (Display Controller)                      |

| Ch      | 7:0  | R   | Cache Line Size                          | 0 (Not Used)                                 |

| Dh      | 7:0  | R   | Latency Timer                            | 0 (Not Used)                                 |

| Eh      | 7:0  | R   | Header Type                              | 0                                            |

| Address | Bits  | R/W | Functions                  | Power Up Default |

|---------|-------|-----|----------------------------|------------------|

| Fh      | 7:0   | R   | BIST                       | 0 (Not Used)     |

| 10h     | 21:0  | R   | Mem. Aperture Base Address | 0                |

|         | 31:22 | R/W |                            |                  |

| 2F:14h  | -     | -   | Reserved                   | 0 Always         |

| 30h     | 0     | R/W | BIOS ROM Enable            | 0                |

|         | 7:1   | R   | Reserved                   | 0 Always         |

| 31h     | 7:0   | R   | Reserved                   | 0 Always         |

| 32h     | 15:0  | R/W | BIOS ROM Base Address      | 0                |

| 3B:34h  | -     | -   | Reserved                   | 0                |

| 3Ch     | 7:0   | R/W | Interrupt Line             | 0                |

| 3Dh     | 7:0   | R   | Interrupt Pin              | 1                |

| 3F:3Eh  | -     | -   | Reserved                   | 0                |

| FF:40h  | -     | -   | Reserved                   | 0                |

| PCI  | Configu | uration    | Registers  | 3 |

|------|---------|------------|------------|---|

| , ,, | CUITING | 21 au 01 1 | , icaisic, | , |

This page intentionally left blank.

# Part II

| and the surface of th | naturist kindi suri i di veluli e ti kin. Me       | ander en en ekkelengen blanke in Nation bes | on stopp through the financial law or a 1999. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------|-----------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

| 그 생살이 발범하는 제가 되지 않는다.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |

| 경험적의 기능하다는 경험을 하고 하는 것같다면                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |                                             |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                               |