## Advanced Programmer's Guide to SuperVGAs

George Sutty Steve Blair

3

New York London Toronto Sydney Tokyo Singapore

Copyright © 1990 by George Sutty and Steve Blair. All rights reserved, including the right of reproduction in whole or in part in any form.

Simon & Schuster, Inc. 15 Columbus Circle New York, NY 10023

#### DISTRIBUTED BY PRENTICE HALL TRADE

Manufactured in the United States of America

$10\,9\,8\,7\,6\,5\,4\,3\,2\,1$

#### Library of Congress Cataloging-in-Publication Data

Sutty, George J. Advanced programmer's guide to SuperVGAs [computer file]. 1 computer disk;  $5^{1/4}$  in. + 1 v. System requirements: IBM PC, XT, AT, PS/2, or compatibles; 640K; MS-DOS 3.0 or higher; one 1.2M disk drive; monochrome monitor; SuperVGA board. Title from t.p. of book. Not copy-protected. Audience: Adult reference/general. Summary: Offers a graphics programming utility with drawing routines for 256, sixteen, and four color graphics. The text is designed to enable users to utilize fully the many advanced features of the SuperVGAs. 1. Computer graphics-Software. I. Blair, Steve. II. Title. 004.7 90-69814 T385.S84 1990 ISBN 0-13-010455-8

## Limits of Liability and Disclaimer of Warranty

The authors and the publisher of this book have used their best efforts in preparing this book and the programs contained in it. These efforts include the development, research, and testing of the theories and programs to determine their effectiveness. The author and publisher make no warranty of any kind, expressed or implied, with regard to these programs or the documentation contained in this book. The author and publisher shall not be liable in any event for incidental or consequential damages in connection with or rising out of the furnishing, performance, or use of these programs.

## Trademarks

IBM PC, PC/XT, PC/AT, PCjr, and PS/2 are trademarks of International Business Machines Corporation.

Hercules is a trademark of Hercules Computer Techology, Inc.

MS-DOS is a trademark of MicroSoft Corporation.

Turbo Pascal is a trademark of Borland International.

Multisync is a trademark of NEC Corporation.

## **Dedication**

To our families for their support and encouragement.

## Acknowledgments

We would like to thank all of the VGA manufacturers who were gracious enough to supply us with technical material and sample products, especially those who participated in the review of the manuscript. This book would not have been possible without their support.

We would particularly like to thank Mr. Gary Lorensen, whose expert and thorough review of the manuscript (in several different versions) contributed greatly to the quality of the finished result.

Special thanks are also due Susan Hunt and the rest of the team at Brady Books for their patience, encouragement, and assistance with the manuscript.

## **Contents**

| PART I—A VGA Review                           | 1        |

|-----------------------------------------------|----------|

| Introduction                                  | 3        |

| Why We Wrote this Book                        | 3        |

| The History of VGA                            | 4        |

| How the Book is Organized                     | 5        |

| 1. Standard VGA Display Modes                 | 7        |

| Introduction                                  | 8        |

| Standard VGS display Modes                    | 9        |

| Modes 0 and 1 (40-column Color Text)          | 9        |

| Modes 2 and 3 (80-column Color Text)          | 10       |

| Modes 4 and 5 (Four-color 320 x 200 Graphics) | 10       |

| Mode 6 (Two-color 640 x 200 Graphics)         | 11       |

| Mode 7 (Monochrome Text)                      | 11       |

| Mode D (Sixteen-color 320 x 200 Graphics)     | 11       |

| Mode E (Sixteen-color 640 x 200 Graphics)     | 11<br>12 |

| Mode F (Monochrome 640 x 350 Graphics)        | 12       |

| Mode 10 (Sixteen-color 640 x 350 Graphics)    | 12       |

| Mode 11 (Two-color 640 x 480 Graphics)        | 12<br>13 |

| Mode 12 (Sixteen-color 640 x 480 Graphics)    | 13       |

| Mode 13 (256-color 320 x 200 Graphics)        | 1.5      |

| 2. Architecture of the VGA                    | 15       |

| Introduction                                  | 16       |

| Packed Pixels vs. Color Planes                | 16       |

| Text Modes vs. Graphics Modes                 | 17       |

| Functional Blocks                             | 18       |

| Display Memory                                | 19       |

| Display Memory in Text Modes                  | 20       |

| Display Memory in Graphics Modes              | 25       |

| The Graphics Controller                       | 30       |

| Processor Read Latches                        | 30       |

| Logical Unit                                  | 31       |

| Color Compare                                 | 32       |

| Data Serializer                               | 32       |

| The Attribute Controller and DACs             | 32       |

| The CRT Controller                            | 34       |

| The Sequencer                                 | 35       |

| 3. | VGA Registers                                                     | 37 |

|----|-------------------------------------------------------------------|----|

|    | Introduction                                                      | 38 |

|    | Control Registers                                                 | 41 |

|    | Miscellaneous Output Register (I/O Address Write 3C2h, Read 3CCh) | 41 |

|    | Input Status Register 0 (I/O Address 3C2, Readonly)               | 42 |

|    | Input Status Register 1 (I/O Address 3BAh/3DAh, Readonly)         | 42 |

|    | VGA Enable Register (I/O Address 3C3h/46E8h)                      | 42 |

|    | The CRT Controller Registers                                      | 43 |

|    | Index 0 - Horizontal Total                                        | 45 |

|    | Index 1 - Horizontal Display Enable                               | 45 |

|    | Index 2 - Start Horizontal Blanking                               | 45 |

|    | Index 3 - End Horizontal Blanking                                 | 45 |

|    | Index 4 - Start Horizontal Retrace                                | 45 |

|    | Index 5 - End Horizontal Retrace                                  | 45 |

|    | Index 6 - Vertical Total                                          | 45 |

|    | Index 7 - Overflow Register                                       | 46 |

|    | Index 8 - Preset Row Scan                                         | 46 |

|    | Index 9 - Maximum Scan Line/Character Height                      | 46 |

|    | Index 0Ah - Cursor Start                                          | 47 |

|    | Index 0Bh - Cursor End                                            | 47 |

|    | Index 0Ch - Start Address (High Byte)                             | 48 |

|    | Index 0Dh - Start Address (Low Byte)                              | 48 |

|    | Index 0Eh - Cursor Location (High Byte)                           | 48 |

|    | Index OF - Cursor Location (Low Byte)                             | 48 |

|    | Index 10h - Vertical Retrace Start                                | 48 |

|    | Index 11h - Vertical Retrace End                                  | 48 |

|    | Index 12h - Vertical Display Enable End                           | 49 |

|    | Index 13h - Offset/Logical Screen Width                           | 49 |

|    | Index 14h - Underline Location Register                           | 49 |

|    | Index 15h - Start Vertical Blanking                               | 49 |

|    | Index 16h - End Vertical Blanking                                 | 49 |

|    | Index 17h - Mode Control Register                                 | 49 |

|    | Index 18h - Line Compare Register                                 | 50 |

|    | Sequencer Registers                                               | 50 |

|    | Index 0 - Reset Register                                          | 50 |

|    | Index 1 - Clock Mode Register                                     | 51 |

|    | Index 2 - Color Plane Write Enable Register                       | 51 |

|    | Index 3 - Character Generator Select Register                     | 51 |

|    | Index 4 - Memory Mode Register                                    | 52 |

|    | Graphics Controller Registers                                     | 52 |

|    | Index 0 - Set/Reset Register                                      | 52 |

|    | Index 1 - Set/Reset Enable Register                               | 53 |

#### viii Advanced Programmer's Guide to Super VGAs

| Index 2 - Color Compare Register                              | 53 |

|---------------------------------------------------------------|----|

| Index 3 - Data Rotate/Function Select Register                | 54 |

| Index 4 - Read Plane Select Register                          | 54 |

| Index 5 - Mode Register                                       | 54 |

| Index 6 - Miscellaneous Register                              | 56 |

| Index 7 - Color Don't Care Register                           | 56 |

| Index 8 - Bit Mask Register                                   | 56 |

| Attribute Controller and Video DAC Registers                  | 57 |

| Attribute Controller Registers                                | 57 |

| Video DAC Registers (I/O Addresses 3C6, 3C7, 3C8, and 3C9)    | 61 |

| 4. The ROM BIOS                                               | 63 |

| What is the ROM BIOS                                          | 64 |

| Individual BIOS Functions                                     | 64 |

| Function 0 - Mode Select                                      | 64 |

| Function 1 - Set Cursor Size                                  | 64 |

| Function 2 - Set Cursor Position                              | 64 |

| Function 3 - Read Cursor Size and Position                    | 65 |

| Function 4 - No Standard Support (Get Light Pen)              | 65 |

| Function 5 - Select Active Page                               | 65 |

| Function 6 - Scroll Text Window Up (or Blank Window)          | 65 |

| Function 7 - Scroll Text Window Down (or Blank Window)        | 66 |

| Function 8 - Read Character and Attribute at Cursor Position  | 66 |

| Function 9 - Write Character and Attribute at Cursor Position | 66 |

| Function 0Ah - Write Character Only at Cursor Position        | 67 |

| Function 0Bh - Set CGA Color Palette (Modes 4,5,6)            | 67 |

| Function 0Ch - Write Graphics Pixel                           | 67 |

| Function 0Dh - Read Graphics Pixel                            | 68 |

| Function 0Eh - Write Character and Advance Cursor             | 68 |

| Function 0Fh - Get Current Display Mode                       | 69 |

| Function 10h - Set EGA Palette Registers                      | 69 |

| Subfunction 0 - Program a Palette Register                    | 69 |

| Subfunction 1 - Set Border Color (Overscan)                   | 69 |

| Subfunction 2 - Set All Palette Registers                     | 69 |

| Subfunction 3 - Blink/Intensity Attribute Control             | 70 |

| Subfunction 7 - Read a Single Palette Register                | 70 |

| Subfunction 8 - Read Border Color (Overscan) Register         | 70 |

| Subfunction 9 - Read All Palette Registers                    | 70 |

| Subfunction 10h - Set a Single DAC Register                   | 71 |

| Subfunction 12h - Set Block of DAC Registers                  | 71 |

| Subfunction 13h - Select Color Subset                         | 71 |

| Subfunction 15h - Read a Single DAC Register                  | 72 |

### x Advanced Programmer's Guide to Super VGAs

| 5. Architecture of the SuperVGAs           | 97         |

|--------------------------------------------|------------|

| Introduction                               | 98         |

| Mapping of Display Memory                  | 98         |

| Host Address Space / Host Window           | 98         |

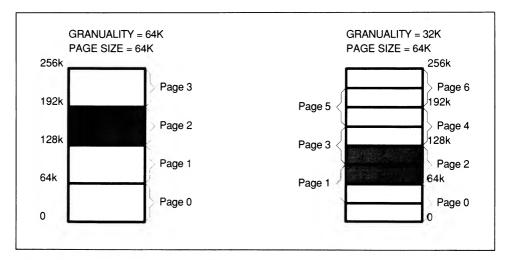

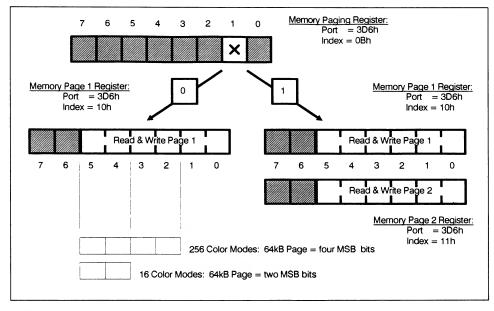

| Memory Planes vs. Memory Pages             | 100        |

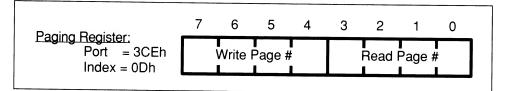

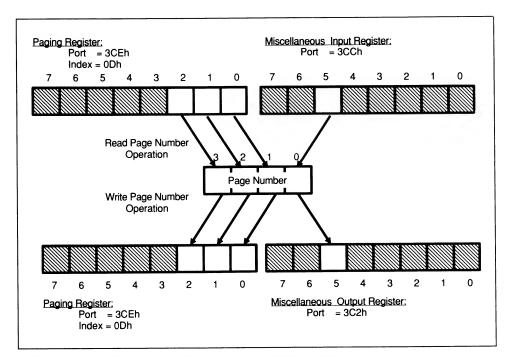

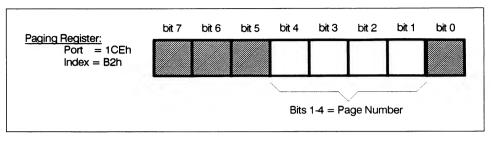

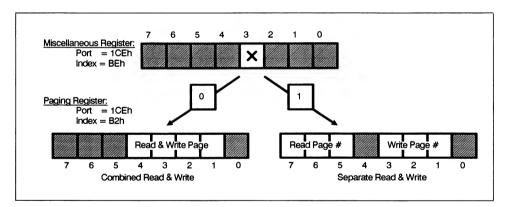

| Display Memory Paging                      | 100        |

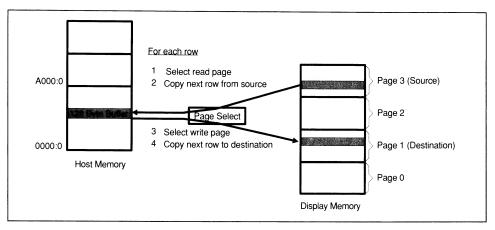

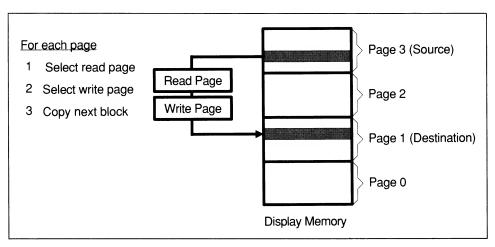

| Graphics Programming with Paged Display Me | mory 104   |

| Page Boundary Detection                    | 104        |

| Enhanced Modes                             | 106        |

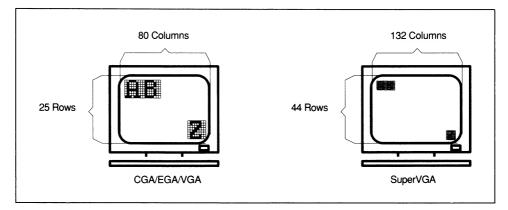

| Enhanced Text Modes                        | 107        |

| Enhanced Graphics Modes                    | 107        |

| The BIOS                                   | 110        |

| Other Features                             | 111        |

| Application Software Drivers               | 111        |

| 16 Bit Data Buses                          | 111        |

| Automatic Display Detection                | 112        |

| Adapter Identification                     | 112        |

| Selecting a SuperVGA                       | 113        |

| Know Your Application                      | 113        |

| Know Your Operating System                 | 113        |

| Evaluate Compatibility                     | 114        |

| Know Which Displays are Supported          | 114        |

| Evaluate Features                          | 114<br>114 |

| Evaluate Performance                       | 114        |

| 6. Programming Examples Overview           | 117        |

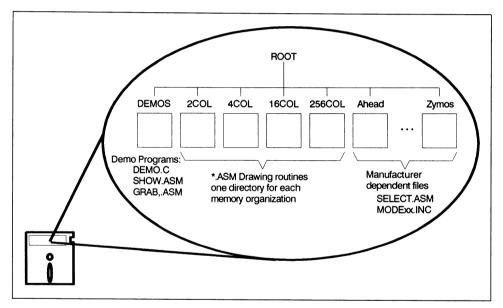

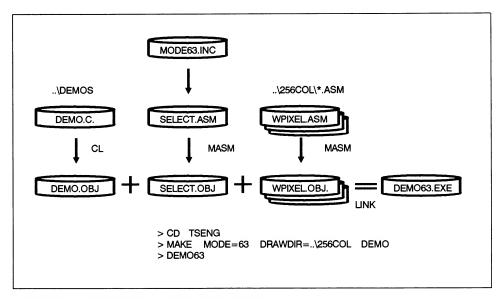

| How The Programming Examples Are Organized | 118        |

| What is on the Diskette                    | 119        |

| How to Use the Programming Examples        | 120        |

| Board- and Mode-Dependent Variables        | 121        |

| Board- and Mode-Dependent Routines         | 122        |

| Computing which Page to Select             | 123        |

| Drawing Routines                           | 124        |

| Write Pixel                                | 124        |

| Read Pixel                                 | 125        |

| Draw Solid Line                            | 125        |

| Draw Scan Line                             | 125        |

| Fill Solid Rectangle                       | 125        |

| Copy Block                                 | 125<br>126 |

| Set Cursor, Move Cursor, Remove Cursor     | 120        |

| Load DACs                                  | 120        |

| Subfunction 17h - Read Block of DAC Registers                       | 72 |

|---------------------------------------------------------------------|----|

| Subfunction 18h - Set PEL Mask                                      | 72 |

| Subfunction 19h - Read PEL Mask                                     | 73 |

| Subfunction 1Ah - Read Subset Status                                | 73 |

| Subfunction 1Bh - Convert DAC Registers to Gray Scale               | 73 |

| Function 11h - Load Character Generator                             | 73 |

| Subfunction 0 - Load Custom Character Generator                     | 74 |

| Subfunction 1 - Load 8 x 14 Character Set                           | 74 |

| Subfunction 2 - Load 8 x 8 Character Set                            | 74 |

| Subfunction 3 - Select Active Character Set(s)                      | 74 |

| Subfunction 4 - Load 8 x 16 Character Set                           | 75 |

| Subfunctions 10h, 11h, 12h, 14h                                     | 75 |

| Subfunction 20h - Initialize INT 1Fh Vector (Modes 4-6)             | 75 |

| Subfunction 21h - Set Graphics Mode to Display Custom Character Set | 75 |

| Subfunction 22h - Set Graphics to 8 x 14 Text                       | 76 |

| Subfunction 23h - Initialize Graphics Mode to Display 8 x 8 Text    | 76 |

| Subfunction 24h - Initialize Graphics Mode to Display 8 x 16 Text   | 77 |

| Subfunction 30h - Return Information About Current Character Set    | 77 |

| Function 12h - Get VGA Status (Set Alternate Print Screen)          | 78 |

| Subfunction 10h - Return VGA Information                            | 78 |

| Subfunction 20h - Revector Print Screen (INT 05h) Interrupt         | 78 |

| Subfunction 30h - Select Scan Line Count for Next Text Mode         | 78 |

| Subfunction 31h - Enable/Disable Palette Load During Mode Set       | 79 |

| Subfunction 32h - Enable/Disable VGA Access                         | 79 |

| Subfunction 33h - Enable/Disable Gray Scale Summing                 | 79 |

| Subfunction 34h - Enable/Disable CGA/MDA Cursor Emulation           | 79 |

| Subfunction 35h - Switch Displays.                                  | 80 |

| Subfunction 36h - Display On/Off                                    | 80 |

| Function 13h - Write Text String                                    | 80 |

| Function 1Ah - Read or Write Configuration                          | 81 |

| Subfunction 0 - Read Display Configuration Code                     | 81 |

| Subfunction 1 - Write Display Configuration Code                    | 82 |

| Function 1Bh - Return VGA Status Information                        | 82 |

| Function 1Ch - Save/Restore Display Adapter State                   | 85 |

| Subfunction 0 - Return Required Buffer Size                         | 85 |

| Subfunction 1 - Save Display Adapter State                          | 86 |

| Subfunction 2 - Restore Display Adapter State<br>The BIOS Data Area | 86 |

| me dios Dala Area                                                   | 86 |

| PART II SuperVCA                                                    |    |

| PART II—SuperVGAs                                                   | 93 |

|                                                                     |    |

Introduction

95

|    | Load Palette                                        | 127 |

|----|-----------------------------------------------------|-----|

|    | Write Raster, Read Raster                           | 127 |

| 7. | Programming Examples—256-Color Graphics             | 129 |

|    | Introduction                                        | 130 |

|    | Display Memory Organization                         | 130 |

|    | Drawing Routines                                    | 131 |

|    | Write Pixel                                         | 131 |

|    | Read Pixel                                          | 132 |

|    | Draw Solid Line                                     | 133 |

|    | Draw Scan Line                                      | 140 |

|    | Fill Solid Rectangle                                | 142 |

|    | Clear Screen                                        | 145 |

|    | Copy Block                                          | 146 |

|    | Set Cursor, Move Cursor, Remove Cursor<br>Load DACs | 165 |

|    | Read Raster Line                                    | 172 |

|    | Write Raster Line                                   | 174 |

|    | while haster line                                   | 176 |

| 8. | Programming Examples—16-Color Graphics              | 179 |

|    | Introduction                                        | 180 |

|    | Display Memory Organization                         | 181 |

|    | Drawing Routines                                    | 181 |

|    | Write Pixel                                         | 181 |

|    | Read Pixel                                          | 184 |

|    | Draw Solid Line<br>Draw Scan Line                   | 185 |

|    | Fill Solid Rectangle                                | 194 |

|    | Clear Screen                                        | 197 |

|    | Copy Block                                          | 200 |

|    | Set Cursor, Move Cursor, Remove Cursor              | 201 |

|    | Load Palette                                        | 210 |

|    |                                                     | 216 |

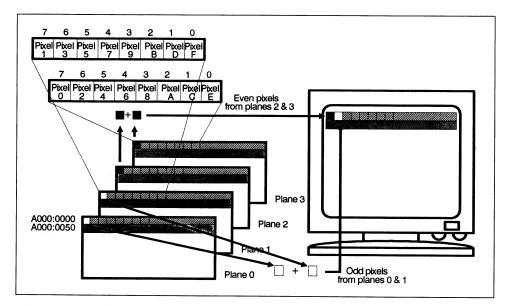

| 9. | Programming Examples—4-Color Graphics               | 219 |

|    | Introduction                                        | 220 |

|    | Four Planes                                         | 220 |

|    | Write Pixel                                         | 222 |

|    | Read Pixel                                          | 224 |

|    | Two Even Planes                                     | 225 |

|    | Write Pixel                                         | 226 |

|    | Read Pixel                                          | 228 |

| Two Consecutive Planes                                      | 229 |

|-------------------------------------------------------------|-----|

| Write Pixel                                                 | 230 |

| Read Pixel                                                  | 232 |

| Four Aalternating Pplanes                                   | 233 |

| Write Pixel                                                 | 234 |

| Read Pixel                                                  | 236 |

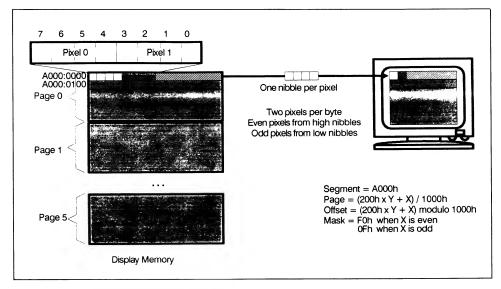

| Packed Ppixels                                              | 238 |

| Write Pixel                                                 | 239 |

| Read Pixel                                                  | 240 |

|                                                             |     |

| 10. Ahead V5000 Ahead VGA Wizard/Deluxe                     | 243 |

| Introduction                                                | 244 |

| Chip Versions                                               | 244 |

| New Display Modes                                           | 244 |

| Memory Organization                                         | 244 |

| High Resolution Text Modes                                  | 244 |

| 2-Color Graphics Mode                                       | 245 |

| 4-Color Graphics Mode                                       | 245 |

| 16-Color Graphics Modes                                     | 245 |

| 256-Color Graphics Modes                                    | 246 |

| New Registers                                               | 246 |

| Master Enable Register                                      | 248 |

| Programming Examples                                        | 249 |

| Display Memory Paging                                       | 249 |

| Detection and Identification                                | 250 |

| 11. ATI 18800 ATI VGAWONDER                                 | 257 |

| Introduction                                                | 258 |

| Versions of the Adapter                                     | 258 |

| New Display Modes                                           | 258 |

| Memory Organization                                         | 259 |

| High Resolution Text Modes                                  | 259 |

| High Resolution Graphics Modes                              | 260 |

| New Registers                                               | 263 |

| ATI Register 0                                              | 264 |

| ATI Register 1-EGA Compatibility and Double Scanning Enable | 264 |

| ATI Register 2-Memory Page Select                           | 265 |

| ATI Register 3                                              | 265 |

| ATI Register 4                                              | 266 |

| ATI Register 5                                              | 266 |

| ATI Register 6                                              | 267 |

|     | ATI Register 7                              | 267 |

|-----|---------------------------------------------|-----|

|     | ATI Register 8                              | 267 |

|     | ATI Register 9                              | 267 |

|     | ATI Register A                              | 267 |

|     | ATI Register B                              | 268 |

|     | ATI Register C                              | 268 |

|     | ATI Register D                              | 268 |

|     | ATI Register E                              | 268 |

|     | The BIOS                                    | 269 |

|     | Extended BIOS Functions                     | 269 |

|     | Extended BIOS Data Area                     | 270 |

|     | Programming Examples                        | 271 |

|     | Accessing Extended Registers                | 271 |

|     | Display Memory Paging                       | 271 |

|     | Mode 65h-1024x768 16-Color Graphics         | 279 |

|     | Eight Simultaneous Fonts                    | 282 |

|     | Detection and Identification                | 290 |

| 12. | Cirrus CL-GD 510, CL-GD 520 MaxLogic MaxVGA | 293 |

|     | Introduction                                | 294 |

|     | Expanded Display Modes                      | 294 |

|     | Memory Organization                         | 295 |

|     | High Resolution Text Modes                  | 295 |

|     | 16-Color Graphics Modes                     | 295 |

|     | 256-Color Graphics Modes                    | 295 |

|     | Expanded Register Set                       | 296 |

|     | Programming Examples                        | 299 |

|     | 256-Color Drawing                           | 299 |

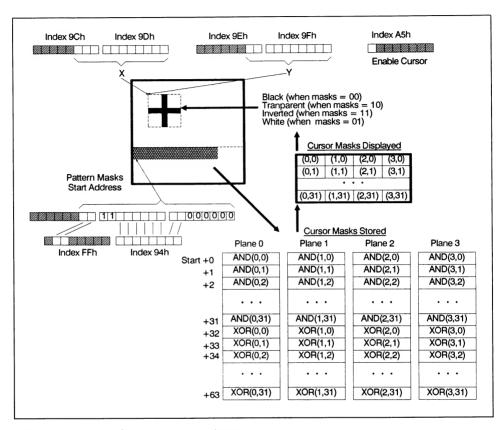

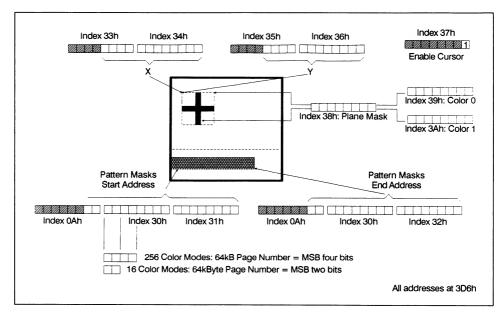

|     | Graphics Cursor Control                     | 301 |

|     | Detection and Identification                | 312 |

| 13. | Chips and Technologies 82C452 Boca 1024VGA  | 315 |

|     | Introduction                                | 316 |

|     | New Display Modes                           | 316 |

|     | Memory Organization                         | 316 |

|     | High Resolution Text Modes                  | 317 |

|     | New Registers                               | 317 |

|     | Setup Control Register                      | 319 |

|     | Extended Enable Register                    | 319 |

|     | Global ID Register                          | 320 |

|     | Extended Register Bank                      | 320 |

#### xiv Advanced Programmer's Guide to Super VGAs

|    | The BIOS                                                               | 325        |

|----|------------------------------------------------------------------------|------------|

|    | Function 5Fh-Subfunction 00h: Return 82C54X Information                | 325        |

|    | Function 5Fh-Subfunction 01h: Preprogrammed Emulation Control          | 326        |

|    | Function 5Fh-Subfunction 02h: Auto-emulation Control                   | 326        |

|    | Function 5Fh-Subfunction 03h: Set Power-on Video Conditions            | 327        |

|    | Function 5Fh-Subfunction 90h: Enhanced Save/Restore Video State Buffer | <b>J</b>   |

|    | Size                                                                   | 327        |

|    | Function 5Fh-Subfunction 91h: Save Video State                         | 328        |

|    | Function 5Fh-Subfunction 92h: Restore Video State                      | 328        |

|    | Programming Examples                                                   | 328        |

|    | Accessing Extended Registers                                           | 328        |

|    | Display Memory Paging                                                  | 329        |

|    | Graphics Cursors                                                       | 336        |

|    | Detection and Identification                                           | 343        |

|    | Detection and Renuncation                                              | 00         |

| 14 | Genoa 6400 Genoa SuperVGA                                              | 345        |

|    | -                                                                      | 346        |

|    | Introduction                                                           | 340<br>346 |

|    | New Display Modes                                                      | 347        |

|    | Memory Organization                                                    | 347        |

|    | High Resolution Text Modes                                             | 348        |

|    | 256-Color Graphics Modes                                               | 348        |

|    | 16-Color Graphics Modes                                                | 348        |

|    | 4-Color Graphics Modes                                                 | 348        |

|    | New Registers                                                          | 340<br>349 |

|    | Interface Control Register                                             | 549<br>349 |

|    | Herchi Register                                                        | 349<br>349 |

|    | Configuration Register                                                 | 349<br>349 |

|    | Memory Page Select Register                                            | 350        |

|    | Enhanced Control Register 2                                            | 350        |

|    | Enhanced Control Register 3                                            | 350        |

|    | Enhanced Control Register 4                                            | 350        |

|    | Program Status Registers 1 and 2                                       | 351        |

|    | Programming Examples                                                   | 351        |

|    | Display Memory Paging                                                  | 356        |

|    | Detection and Identification                                           | 550        |

| 15 | . Headland HT-208 (V7VGA) Headland Video Seven VGA1024i                | 357        |

|    | Introduction                                                           | 358        |

|    | New Display Modes                                                      | 358        |

|    | Memory Organization                                                    | 359        |

|    | High Resolution Text Modes                                             | 359        |

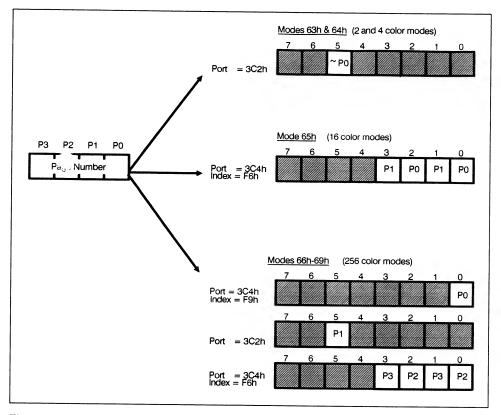

| 2-Color Graphics Mode                                  | 360 |

|--------------------------------------------------------|-----|

| 4-Color Graphics Mode                                  | 360 |

| 16-Color Graphics Mode                                 | 360 |

| 256-Color Graphics Mode                                | 360 |

| New Registers                                          | 360 |

| Index 6-Extension Control Register                     | 362 |

| Index 1Fh-Identification Register                      | 362 |

| Index 8Fh and Index 8Fh-VGAS Chips Revision Register   | 362 |

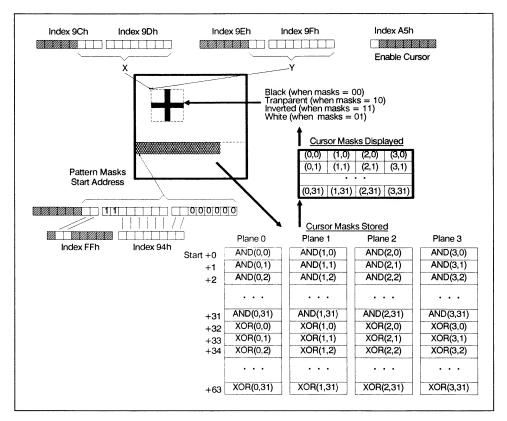

| Hardware Graphics Cursor                               | 363 |

| Index A0h through A3h-Graphics Controller Data Latches | 365 |

| Foreground/Background Operations                       | 365 |

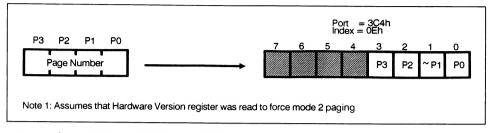

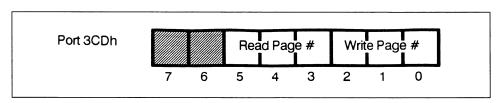

| Display Memory Paging                                  | 368 |

| Index FFh-The16 Bit Interface Control Register         | 369 |

| The BIOS                                               | 370 |

| Interrupt Vectors Used by the BIOS                     | 370 |

| Added BIOS Functions                                   | 370 |

| Programming Examples                                   | 373 |

| Display Memory Paging                                  | 373 |

| Graphics Cursor Control                                | 380 |

| Detection and Identification                           | 392 |

| 16. Trident TVGA 8800CS Everex Viewpoint VGA           | 395 |

| Introduction                                           | 396 |

| Chip Versions                                          | 396 |

| New Display Modes                                      | 396 |

| Memory Organization                                    | 396 |

| High Resolution Text Modes                             | 398 |

| High Resolution Graphics Modes                         | 398 |

| New Registers                                          | 399 |

| Hardware Version Register                              | 400 |

| Mode Control Register                                  | 400 |

| Scratch Pad Register                                   | 400 |

| Processor Latch Read Back Register                     | 401 |

| Attribute Controller Index Read Back                   | 401 |

| The BIOS                                               | 401 |

| Extended Mode Select                                   | 401 |

| Return Emulation Status                                | 402 |

| Set Operating Mode                                     | 403 |

| VGA Register Protect                                   | 403 |

| Enable/Disable Fast Mode                               | 403 |

| Get Paging Function Pointer                            | 403 |

| Get Mode Supported Information                         | 404 |

|     | Program Mode Parameters                                   | 405 |

|-----|-----------------------------------------------------------|-----|

|     | Everex Set Mode                                           | 405 |

|     | Programming Examples                                      | 406 |

|     | Display Memory Paging-Version 1 Mode                      | 406 |

|     | Display Memory Paging-Version 2 Mode                      | 406 |

|     | Detection and Identification                              | 412 |

| 17. | Tseng ET 3000 STB VGA EM-16                               | 415 |

|     | Introduction                                              | 416 |

|     | New Display Modes                                         | 416 |

|     | Memory Organization                                       | 417 |

|     | High Resolution Text Modes                                | 417 |

|     | 16-Color Graphics Modes                                   | 417 |

|     | 256-Color Graphics Modes                                  | 418 |

|     | New Registers                                             | 418 |

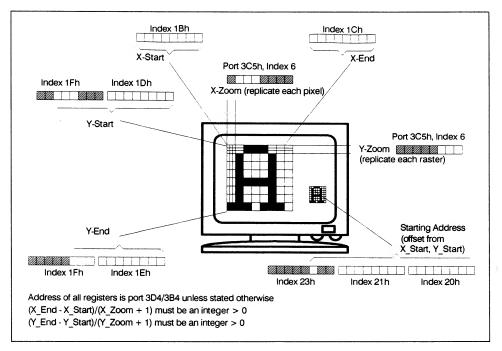

|     | Hardware Zoom Registers                                   | 418 |

|     | Start Address Overflow Register                           | 420 |

|     | Compatibility Control Register                            | 421 |

|     | Auxiliary Overflow Register                               | 421 |

|     | Segment Select Register                                   | 421 |

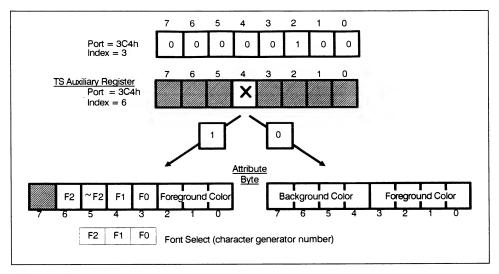

|     | TS Auxiliary Mode                                         | 422 |

|     | CRTC Vertical Sync End                                    | 423 |

|     | Programming Examples                                      | 423 |

|     | Display Memory Paging                                     | 423 |

|     | Hardware Zooming                                          | 429 |

|     | Displaying Eight Simultaneous Fonts                       | 435 |

|     | Detection and Identification                              | 443 |

| 18. | Western Digital WD90C00 Western Digital Paradise VGA 1024 | 445 |

|     | Introduction                                              | 446 |

|     | AT and Micro Channel Versions                             | 446 |

|     | New Display Modes                                         | 447 |

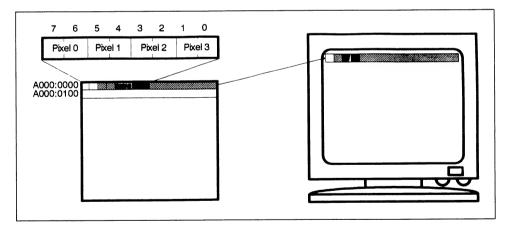

|     | Memory Organization                                       | 447 |

|     | High Resolution Text Modes                                | 447 |

|     | 2-Color Graphics Modes 59H and 5Ah                        | 448 |

|     | 4-Color Graphics Modes 5Bh                                | 448 |

|     | 16-Color Graphics Modes                                   | 449 |

|     | 256-Color Graphics Modes                                  | 449 |

|     | New Registers                                             | 449 |

|     | Module Disable                                            | 450 |

|     | POS Sleep Bit Register                                    | 451 |

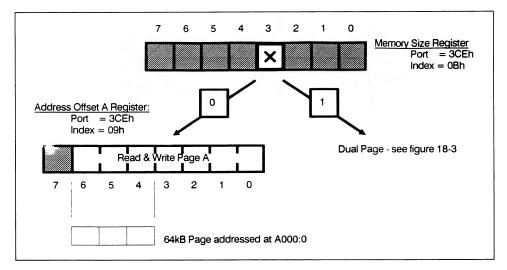

|     | Extended Register Bank           | 451 |

|-----|----------------------------------|-----|

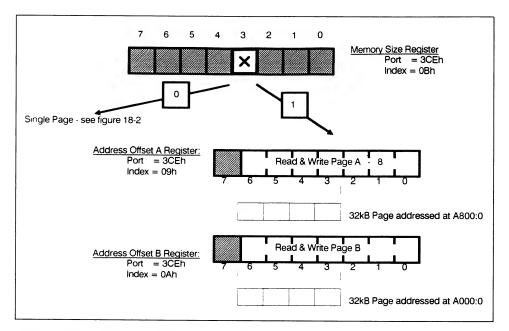

|     | Address Offset A                 | 451 |

|     | Address Offset B                 | 452 |

|     | Memory Size                      | 453 |

|     | Video Select                     | 453 |

|     | CRT Lock Control                 | 454 |

|     | Video Control                    | 455 |

|     | General Purpose Status Bits      | 456 |

|     | Unlock Second Bank               | 456 |

|     | EGA Switches                     | 456 |

|     | Scratch Pad                      | 457 |

|     | Interlace H/2 Start              | 457 |

|     | Interlace H/2 End                | 457 |

|     | Miscellaneous Control 1          | 458 |

|     | Miscellaneous Control 3          | 459 |

|     | The BIOS                         | 459 |

|     | Parametric Mode Set              | 459 |

|     | Enable/Disable Emulation Mode    | 460 |

|     | Inquire Emulation Status         | 460 |

|     | Lock Emulation Mode for Reset    | 460 |

|     | Enable MDA/Hercules Emulation    | 461 |

|     | Enable CGA Emulation             | 461 |

|     | Set Monochrome VGA Mode          | 461 |

|     | Set Color VGA Mode               | 462 |

|     | Read Paradise Extended Register  | 462 |

|     | Write Paradise Extended Register | 462 |

|     | Set Hardware EGA Emulation       | 462 |

|     | Programming Examples             | 463 |

|     | Accessing Extended Registers     | 463 |

|     | Display Memory Paging            | 464 |

|     | BITBLT with Two Pages            | 471 |

|     | Detection and Identification     | 472 |

| 19. | ZyMOS Poach 51 TruTech HiRes VGA | 475 |

|     | Introduction                     | 476 |

|     | Chip Versions                    | 476 |

|     | New Display Modes                | 476 |

|     | Memory Organization              | 476 |

|     | High Resolution Text Modes       | 476 |

|     | 16-Color Graphics Modes          | 477 |

|     | 256-Color Graphics Modes         | 477 |

|     | New Registers                    | 477 |

#### xviii Advanced Programmer's Guide to Super VGAs

|                                 | Hardware Version Register                      | 478 |

|---------------------------------|------------------------------------------------|-----|

|                                 | Mode Control Register 1                        | 478 |

|                                 | Processor Read Back Latch Register             | 479 |

|                                 | Attribute Controller State Register            | 479 |

|                                 | Attribute Controller Index Read Back           | 479 |

| ]                               | Programming Examples                           | 479 |

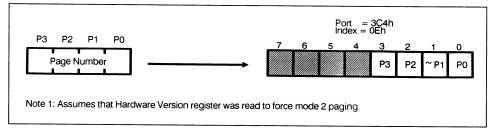

|                                 | Display Memory Paging                          | 479 |

|                                 | Detection and Identification                   | 485 |

| 20. ′                           | The VESA Standard                              | 487 |

|                                 | Introduction                                   | 488 |

| 1                               | VESA Display Modes                             | 488 |

| ,                               | The VESA BIOS                                  | 489 |

|                                 | Function 00H-Return SuperVGA Information       | 489 |

|                                 | Function 01h-Return SuperVGA Mode Information  | 490 |

|                                 | Function 02h-Set SuperVGA Display Mode         | 492 |

|                                 | Function 03h-Return Current Display Mode       | 492 |

|                                 | Function 04h-Save/Restore SuperVGA Video State | 493 |

|                                 | Function 05h-Display Memory Widow Control      | 494 |

|                                 | Programming Examples                           | 495 |

|                                 | Display Memory Paging                          | 495 |

|                                 | Detection and Identification                   | 501 |

| 21.                             | Displays for SuperVGAs                         | 505 |

|                                 | Introduction                                   | 506 |

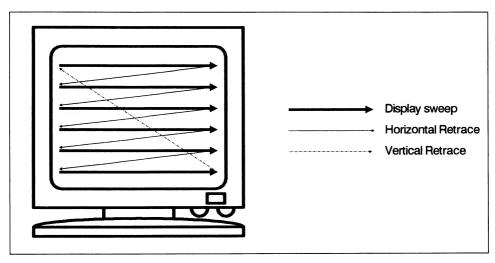

|                                 | Operation of CRT Displays                      | 506 |

|                                 | Factors Affecting Display Resolution           | 508 |

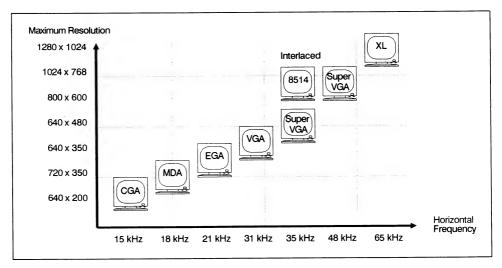

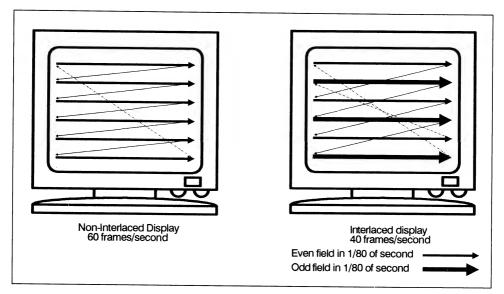

|                                 | Scan Frequency vs. Resolution                  | 508 |

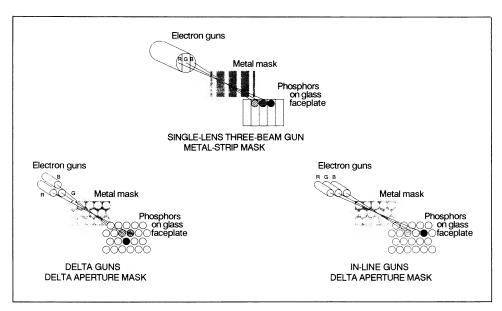

|                                 | Shadow Mask and Gun Arrangement                | 509 |

|                                 | Dot Pitch and Spot Size                        | 510 |

|                                 | Human Eye and Resolution                       | 511 |

|                                 | Specifications for Common SuperVGA Displays    | 512 |

|                                 | Interface Type                                 | 512 |

|                                 | Video Connector Type                           | 512 |

|                                 | Selecting a Display for SuperVGA               | 513 |

|                                 | Popular VGA-Compatible Displays                | 516 |

| Appendix A VGA BIOS Summary     |                                                |     |

| Appendix B VGA Register Summary |                                                |     |

| Appendix C Character Set      | 553 |

|-------------------------------|-----|

| Appendix D Standard VGA Modes | 555 |

| Appendix E Examples Summary   | 557 |

| Appendix F VGA Boards         | 561 |

| Appendix G VGA Displays       | 569 |

| Appendix H Debugging Video    | 573 |

| Glossary                      | 575 |

| Index                         | 583 |

# Part I

## **A VGA Review**

## Introduction

Since the introduction of the Apple Macintosh computer system in 1984, which gained wide acceptance as an easy-to-learn and easy-to-use tool to increase productivity, nearly all new user interfaces for computers have been graphics based. Such popular interfaces as Microsoft Windows, IBM Presentation Manager, GEM by Digital Research, NewWave by Hewlett-Packard, X-Windows, NextStep, NeWS and Open Look are all graphics based. Graphical interfaces offer many advantages over text-based interfaces, and are especially useful in personal computers where a user-friendly, interactive interface can have big payoffs in productivity and ease of use.

Increasingly, today's most popular software applications (Aldus Pagemaker, Microsoft Excel, Ventura Publisher, and others) rely on Graphical User Interfaces (GUIs) to interact efficiently with the user. It appears that GUIs are destined to become the standard for personal computers. This also means that graphics programming is becoming less of a programming specialty and more the standard method of implementing applications.

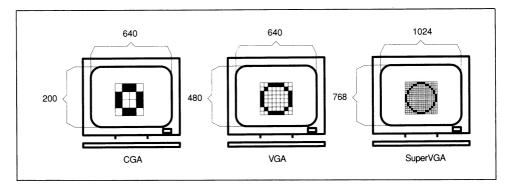

The increasing popularity of GUIs has been made possible by rapid advances in graphics technology. In just a few years, personal computer graphics has progressed from nonexistent to the breathtaking quality of the VGA and SuperVGA, which are quickly becoming the most prevalent graphics adapters for IBM-compatible computers. The superior features and affordable price of the VGA guarantee it an increasing share of the IBM-compatible video market. International Data Corporation predicted that in 1989 1.7 million EGA boards will be shipped, compared with 1.4 million VGA boards. By 1993, however, IDC predicts that VGA (including SuperVGA) will be the most prevalent display adapter in use, with more than 11 million units installed.

## Why We Wrote this Book

The IBM VGA has been well documented in several texts. We are partial to our previous text, the *Advanced Programmer's Guide to EGA/VGA*, as a convenient reference on the subject. Most of the VGA boards on the market, however, offer significant features (such as high resolution display modes) that are not available on the IBM product and are not covered in any of the texts on VGA. The added benefits of SuperVGA boards are not at all trivial; SuperVGAs can now be used in applications for which the original IBM VGA is ill-suited.

This book contains the information you need to know to write software that takes advantage of the benefits of SuperVGAs. Its sole purpose is to provide a complete and comprehensive tutorial on SuperVGAs. It tells you, among other things, what SuperVGA features are available, how to select a SuperVGA that suits your needs, how to utilize advanced SuperVGA features in your software, and how to write graphics drawing routines that will work in the high resolution modes of your SuperVGA. It explains the differences between SuperVGAs, as well as their similarities. It describes what displays are available and offers suggestions on how to select one.

In short, this book is designed to enable you to utilize fully the many advanced features of the SuperVGAs.

## The History of VGA

While IBM has repeatedly demonstrated its ability to use a combination of engineering and marketing to set important standards for personal computing, many competitors have shown their ability to improve on IBM's standards by introducing products that are IBM compatible but with additional features and enhancements which are not included in the IBM product.

Introduced in 1982 with the IBM PC, the Monochrome Display Adapter (MDA) was IBM's first video product for personal computers. The MDA is a text mode display adapter, and offers no graphics or color capabilities. Shortly thereafter, Hercules Computer Technology Inc. introduced the Hercules Monochrome Graphics Adapter, which is MDA compatible but offers a graphics mode as well. Hercules established the first independent video standard for IBM computers.

MDA was followed by the Color Graphics Adapter (CGA), which offers relatively crude color graphics modes. CGA text is actually less readable than that of the MDA, and CGA gained acceptance only among those who had a strong desire for its color graphics capabilities. Several manufacturers introduced enhanced CGA products, but due to a lack of standardization their product enhancements were largely ignored.

In 1985 IBM introduced the Enhanced Graphics Adapter (EGA). The EGA offers color graphics modes which are superior to those of the CGA, and includes some compatibility with MDA and CGA as well. With EGA, IBM began a new product trend; it was the first PC video adapter to be based on proprietary (VLSI) technology. This made the task of building a compatible product much more difficult for IBM's competitors. Around the same time the Professional Graphics Controller (PGC) became available. Although this board provided 256 colors in 640x480, the high cost of the adapter and even higher cost of display needed caused this board to capture only a very small segment of the PC market.

Despite its advantages, the cost of the IBM EGA kept it from becoming widely accepted until several chip manufacturers (Chips and Technologies, Paradise, Tseng Labs, ATI, and others) engineered the VLSI devices required to clone the IBM product, adding enhancements as they did so. IBM quickly became an insignificant force in the EGA market.

The IBM Video Graphics Array (VGA) was introduced by IBM in April 1987 as the standard display interface for the PS/2 line of personal computers, except models 25 and 30 which are equipped with the Multi-Color Graphics Array (MCGA). VGA is similar to EGA, but is the first IBM display adapter to use an analog display interface (previ-

ous adapters used digital display interfaces). This gives the VGA much greater color capabilities than the EGA. Before VGA, 256-color capability in the IBM PC-compatible arena was available only with high-end graphics products. The MCGA has not become popular and is found only in low-end PS/2 products from IBM.

While the PS/2 and its Micro Channel have managed to capture only a small percentage of the personal computer market, the VGA quickly gained widespread market acceptance as the display standard of the future. EGA chip manufacturers soon repeated their success by cloning the IBM VGA. Their enhanced VGA products, which offer higher resolutions and more colors than the IBM product, have been nicknamed the SuperVGAs.

By October 1987, STB Systems and Sigma Designs were shipping register-compatible VGA boards, and many other vendors were announcing similar products. By late 1987, enhanced VGA products were appearing with 800 by 600 resolution, the greater detail quickly becoming popular for desktop publishing and Computer-Aided Design (CAD). By late 1988 many vendors were offering 256-color modes at resolutions of 640 by 400, 640 by 480, and even 800 by 600.

Unfortunately, the displays available at the time were less than ideal at this resolution, exhibiting noticeable flicker and data degradation. As displays with higher bandwidth and scanning rates became available, VGA board vendors added support for 1024 by 768 resolution.

VGA chip vendors now appear to be the driving force behind the personal computer graphics industry. By designing newer and better VGA chips, they have defined the features and enhancements that are found in the newest SuperVGA products.

The fly in all this graphics ointment is that there is a lack of standardization among SuperVGA vendors as to how enhancements have been added. This has made it difficult for software developers to utilize the enhanced features. SuperVGA board vendors have partially alleviated this problem by supplying drivers with their products to utilize the enhanced features with popular software packages such as Microsoft Windows, GEM, Autocad, Lotus 1-2-3, and others.

Recognizing the virtues of standardization, a number of SuperVGA vendors have now banded together to form the Video Electronics Standards Association (VESA), a standards committee committed to, among other things, the development of an expanded VGA standard. VESA has also assumed the task of standardizing the interface for the high resolution displays that are needed to take advantage of SuperVGA technology. It will be a rare accomplishment if this industry organization succeeds in setting a personal computing standard without the assistance of IBM.

### How the Book is Organized

The Advanced Programmer's Guide to SuperVGAs is intended to satisfy the growing need for detailed information regarding enhanced VGA products. It explains how to

#### 6 Advanced Programmer's Guide to Super VGAs

write software that can utilize the advanced modes and features of the SuperVGAs. It includes useful graphics algorithms tailored for the SuperVGA. The book is intended to be used both as a tutorial text and as a reference source where answers to VGA related questions can be found. It is a companion text to the *Advanced Programmer's Guide to EGA/VGA*, which offers the reader a complete tutorial regarding the IBM EGA and VGA display adapters and compatible products. An understanding of the information in that text is prerequisite for much of the information that is presented here. This text will concentrate on SuperVGA features that are not found on the standard VGA. It is assumed that the reader has some familiarity with the BIOS, register set, and display memory of the standard IBM VGA, as well as the Intel 8086/80286 assembly language instruction set.

The book consists of two major sections:

Part I contains an overview of the VGA architecture. Basic principles of the VGA, its register set, display memory, and ROM BIOS are discussed. This chapter is not intended to be a substitute for the in-depth description of the VGA given in our previous text, the *Advanced Programmer's Guide to EGA/VGA*. It is included here as a summary and reference source.

Part II covers basic principles that are common among SuperVGAs. While SuperVGA implementations differ from vendor to vendor, basic design requirements are the same for all. These include issues such as how to address the much larger display memory that is required, what new display resolutions to support, what new BIOS support to add, and what software drivers to supply. It includes a discussion of the incompatibilities between some of the popular SuperVGA products. Programming examples illustrate how to manipulate registers and read back VGA status information. Only products that are capable or 256 colors at resolutions of 640x400 or better are considered here to be SuperVGAs.

Part II of the book provides detailed descriptions of some of the most popular SuperVGA products (one per chapter). The characteristics of a particular VGA product are for the most part determined by the manufacturer of the VLSI integrated circuit that is the heart of any VGA design. VGA products from several different board vendors may be very compatible if they are based on the same VLSI device. This section describes VGA products based on commonly found VLSI devices. The result is that most VGA products currently on the market will conform closely to one of these descriptions.

The final chapter of the book is dedicated to VGA-compatible displays. A large number of high quality, high resolution color displays are now available, each with its own advantages and disadvantages. Included is a summary of display terminology and information needed to evaluate different displays. Resolution, bandwidth, pixel size, tube size, aspect ratio and sync timing are just some of the factors that affect the quality and flexibility of a display.

The appendices of the book contain tables that summarize VGA information for quick reference, along with a glossary of terms.

# 1

## Standard VGA Display Modes

## Introduction

IBM introduced the Video Graphics Array (VGA) display adapter in 1985 as the standard display adapter for their PS/2 computer systems. While acceptance of the PS/2 and its Micro Channel has been mixed, the VGA has been widely embraced as the graphics adapter technology of today and tomorrow.

Unlike most earlier display adapters, which drive displays with a TTL digital interface, VGA adapters drive analog displays. This makes it possible for the VGA to display many more colors than other display adapters (including EGA). It also means, however, that the VGA is incompatible with many existing displays.

As the VGA and its analog monitors become more widespread, compatibility will become much less of an issue. Many programs written for other color display adapters cannot operate with monochrome displays, and vice versa. This is not a problem with the VGA; if a monochrome display is attached, color information is automatically converted to shades of gray. Monochrome information can also be shown on a color screen.

Both color and monochrome VGA-compatible displays are available from a wide variety of sources. Part 3 of this text discusses popular VGA displays.

Like its predecessors, the VGA is a nonintelligent display device; it has no on-board drawing or processing capability. The system processor must perform all drawing functions by writing directly to display memory. Essentially, writing one bit into display memory is equivalent to lighting one pixel on the display screen. Most of the circuitry of the VGA is dedicated to the task of transferring the data in display memory onto the display screen. This process, called display refresh, must be performed between 50 and 70 times each second.

In color display systems, the number of colors that can be displayed on the screen at one time is governed by the number of bits of display memory that are dedicated to color information for each pixel. If n bits per pixel are used, 2<sup>n</sup> colors can be generated. VGA uses from one to eight bits per pixel, permitting up to 256 (2<sup>8</sup>) colors to be displayed on the screen at the same time. In other words, the VGA is capable of 256 simultaneous colors.

In order to standardize the video interface for applications software, IBM defined a set of standard display modes for the VGA. SuperVGA vendors have added to the list of standard modes by creating new high resolution display modes. These modes do not represent all configurations in which the display adapter can operate, but there are few good reasons to stray from the defined standard modes. Many of the standard VGA display modes have been carried forward from the MDA, CGA, and EGA display adapters.

Table 1.1 lists the display modes that are available for the standard VGA.

| Mode   | Туре     | Resolution                                     | Colors |

|--------|----------|------------------------------------------------|--------|

| 0,1    | Text     | 40 columns x 25 rows (320x200, 8x8 char cell)  | 16     |

| 0*     | Text     | 40 columns x 25 rows (320x350, 8x14 char cell) | 16     |

| 0 +    | Text     | 40 columns x 25 rows (320x400, 9x16 char cell) | 16     |

| 2,3    | Text     | 80 columns x 25 rows (640x200, 8x8 char cell)  | 16     |

| 2*     | Text     | 80 columns x 25 rows (640x350, 8x14 char cell) | 16     |

| 2+, 3+ | Text     | 80 columns x 25 rows (640x400, 9x16 char cell) | 16     |

| 4,5    | Graphics | 320 horizontal x 200 vertical                  | 4      |

| 6      | Graphics | 640 horizontal x 200 vertical                  | 2      |

| 7      | Text     | 80 columns x 25 rows (720x350, 8x14 char cell) | Mono   |

| 7+     | Text     | 80 columns x 25 rows (720x400, 9x16 char cell) | Mono   |

| D      | Graphics | 320 horizontal x 200 vertical                  | 16     |

| E      | Graphics | 640 horizontal x 200 vertical                  | 16     |

| F      | Graphics | 640 horizontal x 350 vertical                  | Mono   |

| 10h    | Graphics | 640 horizontal x 250 vertical                  | 16     |

| 11h    | Graphics | 640 horizontal x 480 vertical                  | 2      |

| 12h    | Graphics | 640 horizontal x 480 vertical                  | 16     |

| 13h    | Graphics | 320 horizontal x 200 vertical                  | 256    |

Table 1-1. Standard IBM VGA video modes

Since the introduction of the IBM Color Graphics Adapter (CGA), all IBM display adapters have included 40 column text modes. These modes were created to allow text to be displayed on home television sets, which have much poorer resolution than computer displays and cannot display 80 columns of text. Other than a small number of computer games which have been written using 40-column text, these modes are not commonly used.

Special adapter circuitry is required to connect an IBM compatible computer to a television set (unless the TV set can accept composite video input).

## **Standard VGA Display Modes**

#### Modes 0 and 1 (40-column Color Text)

On the VGA there is no functional difference between mode 0 and mode 1. These two modes were brought forward from the CGA video adapter and the distinction between them disappeared with the CGA Composite Video output jack. Modes 0 and 1 display color text at a resolution of 40-character columns by 25-character rows.

CGA compatibility is not complete, and not all CGA software will run properly in these modes. In general, software which makes use of BIOS video services and avoids any direct access to I/O registers on the video adapter will usually run without prob-

lems. Direct processor access to display memory does not cause compatibility problems.

#### Modes 2 and 3 (80-column Color Text)

Modes 2 and 3 are the 80-column counterparts to the 40-column modes 0 and 1. On the VGA, there is no functional difference between mode 2 and mode 3. As with modes 0 and 1, these two modes were brought forward from the CGA video adapter and the distinction between them disappeared with the CGA Composite Video output jack. Modes 2 and 3 display color text at a resolution of 80-character columns by 25-character rows.

#### **Double Scanning**

When operating in CGA-compatible graphics modes, the VGA display adapter uses a technique known as DOUBLE SCANNING to display the low resolution (200 scan line) CGA display on the high resolution (400 scan line) VGA display. Each of the 200 horizontal scan lines is displayed twice, increasing the vertical screen resolution from 200 scan lines to 400 scan lines. This improves the quality of the display, and helps compensate for the different aspect ratio of the VGA display. Double Scanning is used for modes 4,5,6,D, and E.

#### Modes 4 and 5 (Four-color 320x200 Graphics)

Modes 4 and 5 are very popular CGA graphics modes which were also carried forward to EGA and VGA. The distinction between these modes disappeared with the CGA Composite Video output jack. Display resolution is 320 pixels horizontally by 200 pixels vertically. The VGA uses double scanning to increase this to 400 lines vertically.

Four-color pixel data is stored in a packed pixel format with two bits per pixel. Details are given in the section "Display Memory in Graphics Modes."

As with all standard CGA modes, compatibility is not complete. Software which writes directly to I/O registers of the CGA may not function properly on VGA. Software which makes use of BIOS calls to configure the registers will usually operate properly.

#### **CGA Graphics Modes**

These modes present an unusual set of challenges for the graphics programmer because the display memory is not linearly mapped. A computation is required to translate from a pixel location on screen to a location in display memory. For an explanation of the CGA graphics memory map, see the section "Display Memory in Graphics Modes".

### Mode 6 (Two-color 640x200 Graphics)

Mode 6 is the highest resolution graphics mode of the CGA, carried forward to VGA. A screen resolution of 640 pixels horizontally by 200 lines vertically is supported, but only in two colors. The VGA uses double scanning to increase this to 400 lines vertically.

As with all standard CGA modes, compatibility is not complete. Software which writes directly to I/O registers of the CGA may not function properly on EGA. Software which makes use of BIOS calls to configure the registers will usually operate properly.

As explained for modes 4 and 5, the display memory is not linearly mapped. A computation is required to translate from a pixel position on the screen to an address in display memory. Details are given in the section "Display Memory in Graphics Modes."

#### Mode 7 (Monochrome Text)

In mode 7 the VGA is partially software compatible with the Monochrome Display Adapter (MDA). The display is formatted as 80 character columns by 25 character rows. In monochrome text mode, character attributes do not control character color but represent other display characteristics. Monochrome text attributes include character blink, intensify, underline, and reverse video. Monochrome text attributes are described in detail later in this chapter.

#### Mode D (Sixteen-color 320x200 Graphics)

Unlike previously described modes, this mode is not a backward compatibility mode for CGA or MDA; it exists for EGA and VGA only. It is loosely patterned after mode 4 (CGA 4-color graphics), but offers more colors. The limited resolution of mode D (320 horizontal pixels by 200 vertical lines) makes it undesirable for new software applications, yet it is not software compatible with any older applications. The result is that mode D is rarely used. The VGA uses double scanning to increase the screen size to 400 lines vertically.

Mode D does not suffer from the nonlinear memory mapping that CGA compatible graphics modes do, and translating from a pixel position on the screen to a location in display memory is relatively straightforward. The memory map for mode D is described in the section "Display Memory in Graphics Modes".

#### Mode E (Sixteen-color 640x200 Graphics)

Like mode D, mode E exists for the EGA and VGA only. It is loosely patterned after CGA mode 6 (two-color graphics), but offers more colors. Its limited resolution (640 pixels horizontally by 200 lines vertically) makes it unpopular for new software devel-

#### 12 Advanced Programmer's Guide to Super VGAs

opment, and it is not compatible with any older existing software. The result is that mode E is rarely used. The VGA uses double scanning to increase the screen size to 400 lines vertically.

Mode E does not suffer from the nonlinear memory mapping that CGA compatible graphics modes do, and translating from a pixel position on the screen to a location in display memory is relatively simple. Details are given in the section "Display Memory in Graphics Modes."

#### Mode F (Monochrome 640x350 Graphics)

Graphics mode F is unique to the EGA and VGA. Resolution in mode F is 640 pixels horizontally by 350 lines vertically, which is less than the 720 horizontal by 348 vertical resolution of the Hercules monochrome graphics adapter.

Mode F does not suffer from the nonlinear display memory address mapping of the Hercules adapter. The display memory is linearly mapped.

Two "color" planes of display memory are used, giving each monochrome pixel four attributes. These attributes are:

00 - black

01 - white

10 - blinking

11 - intensified

The memory planes can be enabled and disabled independently by writing to the plane enable register, index 2 in the Sequencer.

#### Mode 10 (Sixteen-color 640x350 Graphics)

Mode 10, which is unique to the EGA and VGA, is the most popular mode for new color graphics applications. It supports a resolution of 640 horizontal pixels by 350 vertical pixels. Four color planes are used, yielding up to 16 simultaneous colors. Color planes are enabled and disabled by writing to the plane enable register in the Sequencer.

#### Mode 11 (Two-color 640x480 Graphics)

Mode 11 supports the IBM VGA at its highest standard resolution (640 pixels horizontally by 480 lines vertically), but supports only two simultaneous colors. This mode can be used to display 30 rows of 80 column text.

### Mode 12 (Sixteen-color 640x480 Graphics)

Mode 12 supports the VGA at its highest resolution (640 pixels horizontally by 480 lines vertically), with 16 simultaneous colors. This is a popular mode for new color graphics applications. Four color planes are used, yielding up to 16 simultaneous colors. Color planes are enabled and disabled by writing to the plane enable register, index 2, in the Sequencer.

#### Mode 13 (256-color 320x200 Graphics)

This mode, which is unique to the VGA, is the only 256-color mode of the standard VGA. Resolution is limited to only 320 pixels horizontally by 200 lines vertically, which is double scanned to increase the vertical height to 400 lines.

#

## Architecture of the VGA

## Introduction

With the exception of the video output DAC (Digital to Analog Converters), the architecture of the VGA closely resembles that of the EGA. The VGA includes a few additional registers, and lacks the light pen support of EGA. Unlike many of the EGA registers, most VGA registers include read-back capability; the lack of read-back ability was such a drawback in the original EGA that it was added later by most EGA chip manufacturers.

#### **Packed Pixels vs. Color Planes**

Two common techniques for storing color information are the packed pixel method and the color plane method. The original EGA is color plane oriented, except for the CGA-compatible modes, modes 4 through 5, which use packed pixels. VGA has one added mode, the 256-color packed pixel mode.

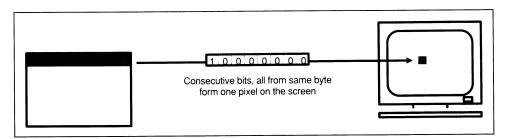

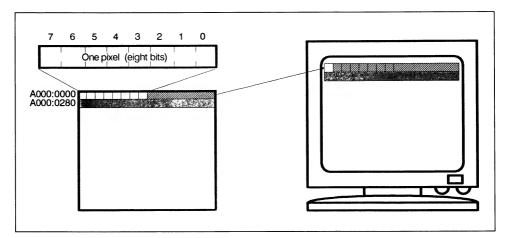

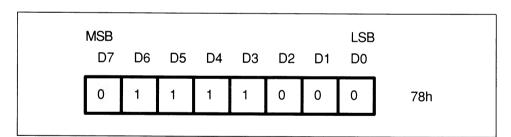

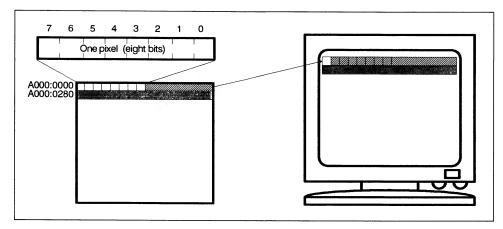

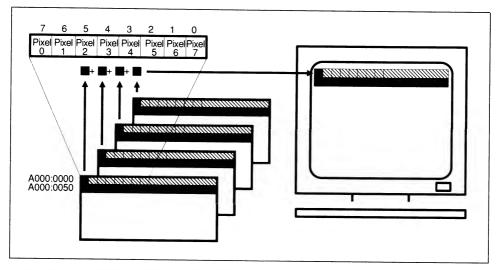

With packed pixels, all color information for a pixel is packed into one word of memory data. For a system with few colors, this packed pixel may require only part of one byte of memory; for very elaborate systems, a packed pixel might be several bytes long. Using 8 bits per pixel, a packed pixel looks as shown in Figure 2-1.

#### Figure 2-1. Packed pixels

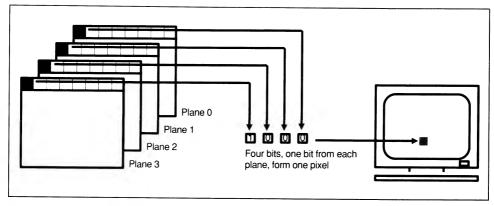

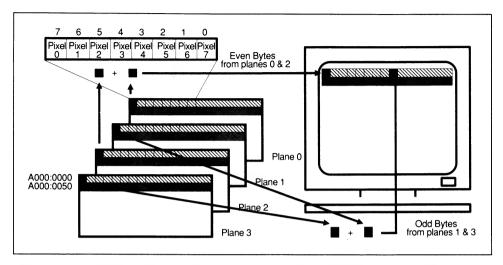

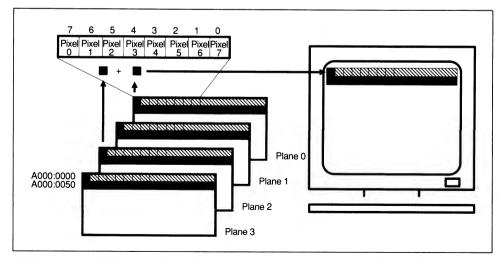

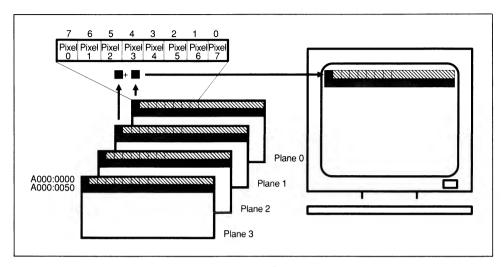

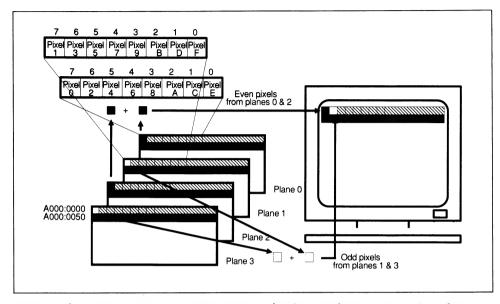

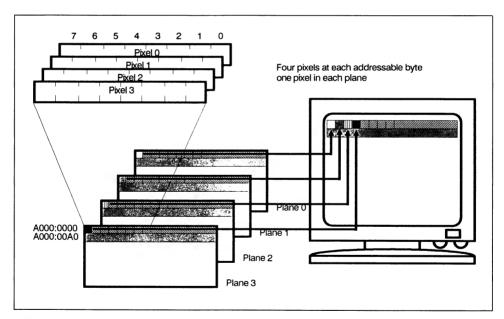

With the color plane approach, the display memory is separated into several independent planes of memory, with each plane dedicated to controlling one color component (such as red, green, or blue). Each pixel of the display occupies one bit position in each plane. This approach is shown in Figure 2-2.

Figure 2-2. Planar pixels

### **Text Modes vs. Graphics Modes**

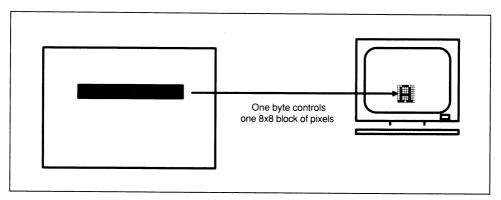

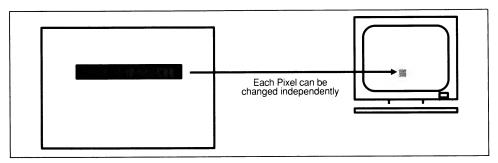

Two basic types of operating modes exist for the VGA: text mode and graphics mode. In graphics modes (which IBM frequently refers to as **All Points Addressable** modes), a set of bits in display memory represents a single pixel on the display screen. In text modes, however, a single byte ASCII character code placed in display memory causes an entire text character to be displayed on the screen. Text modes require much less display memory and place less burden on the system processor, but they are very limited in that only text and crude block graphics objects can displayed. Figure 2-3 illustrates the basic operation of a text mode, and Figure 2-4 shows the operation of a graphics mode.

Figure 2-3. Text mode operation

Figure 2-4. Graphics mode operation

## **Functional Blocks**

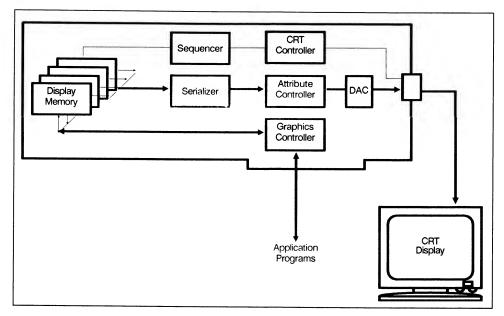

Figure 2-5 illustrates the basic architecture of the VGA, which consists of six major functional blocks:

- The **Display Memory** is a bank of 256 K (or more) of dynamic random access memory (DRAM or VRAM), divided into four planes, which holds the screen display data.

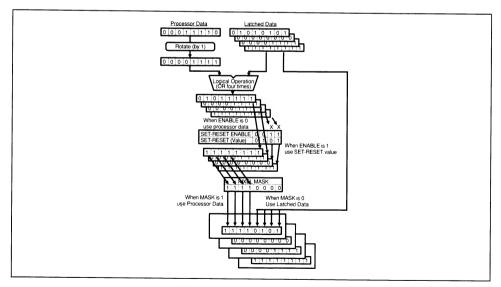

- The **Graphics Controller** resides in the data path between the processor and display memory. It can be programmed to perform logical functions (such as AND, OR, XOR, or ROTATE) on data being written to display memory. These logical functions can provide a hardware assist to simplify drawing operations.

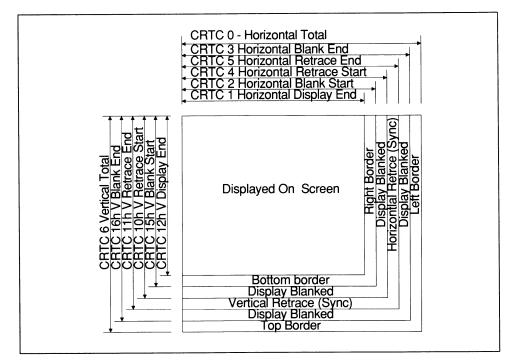

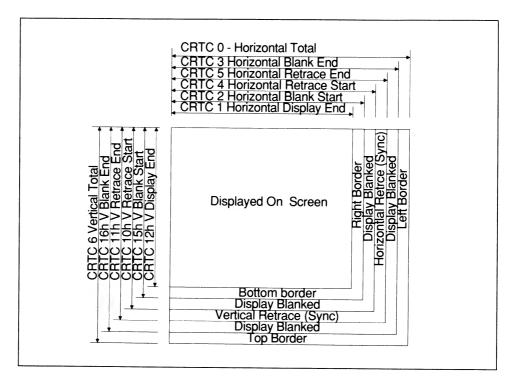

- The **CRT Controller** generates timing signals (such as syncing and blanking) to control the operation of the CRT display and display refresh timing.

- The **Data Serializer** captures display information which is taken from display memory one or more bytes at a time, and converts it to a serial bit stream to be sent to the CRT display. Some boards use VRAM to serialize data.

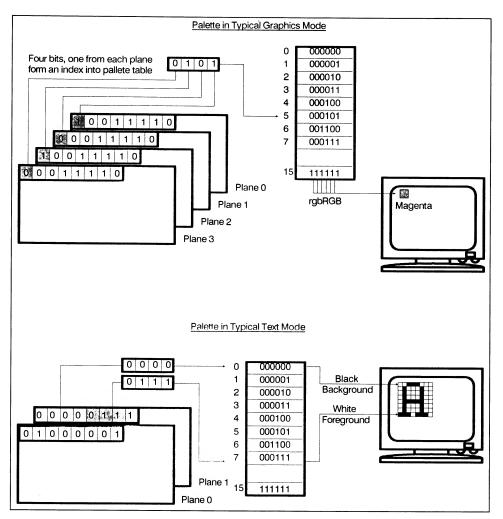

- The **Attribute Controller** contains one of two color lookup tables (LUTs) that translate color information from the display memory into color information for the CRT display. The first lookup table is controlled via Palette registers of the attribute controller, and the second table is contained in video DACs. Because of the relatively high cost of display memory, a practical display system will typically use a display that supports many more colors than the matching display adapter can simultaneously display. By programming a color lookup table on the display adapter, a programmer can select which subset of the display's colors will be supported for his software.

- The **Video DACs** (Digital to Analog Converters) convert digital color data into an analog signal. They also contain the second color lookup table.

- The **Sequencer** controls the overall timing of all functions on the board. It also contains logic for enabling and disabling color planes.

Figure 2-5. VGA block diagram

# **Display Memory**

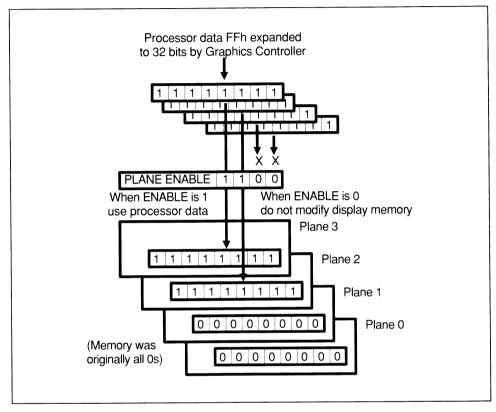

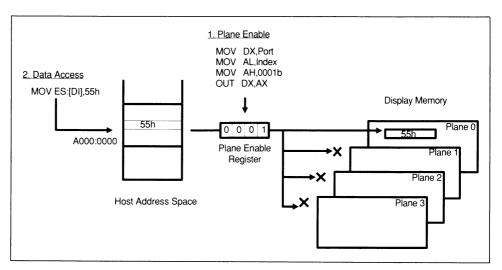

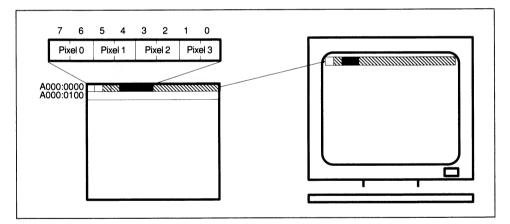

The VGA contains 256 K (or more) of display memory, divided into four independent 64 K (or 128 K) sections of memory called **color planes**. These memory planes all reside in the same processor memory space. Which color planes are being written to or read from at any time is determined by the settings of several I/O registers.

With all four memory planes residing in the same address space, the processor can write to all four planes (or any combination thereof) with a single memory write cycle. This capability can be very useful for some drawing operations, such as fast screen fills. In other drawing operations, it may be desirable to disable writing to all but a single memory plane. Color planes are enabled and disabled for writing via the Color Plane Write Enable register of the Sequencer.

Since it would not be meaningful for the processor to attempt to read data from more than one source at a time, only one memory plane may be enabled for reading. A color plane is enabled for reading via the Read Plane Read Select register of the Graphics Controller. A special mode is provided, however, to read data from multiple color planes, compare it to some preset reference data, and return status to the processor declaring if the colors matched. The color compare function is useful for finding certain patterns in display memory during operations such as area fills. This mode is controlled by the Color Compare register of the Graphics Controller.

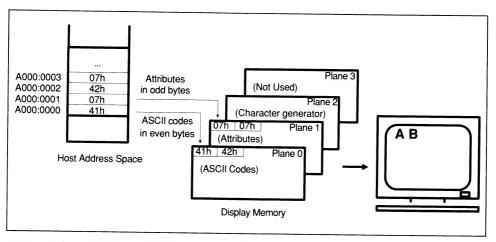

In some operating modes, the organization of display memory will be altered. The best example of this is text mode, where even memory addresses (containing ASCII data) are in memory plane 0, odd memory addresses (containing text attributes) are in memory plane 1, memory plane 2 is reserved for the character generator, and memory plane 3 is unused.

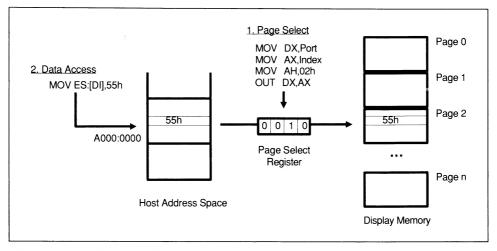

For many operating modes, the 64K address space of the EGA is divided into several display pages. Application software may then control which page is active (being viewed) at any time, and drawing operations can take place in off-screen display memory.

The processor address space used by the EGA and VGA depends on the operating mode. This address space may begin at address A0000, B0000, or B8000, depending on the mode.

## **Display Memory in Text Modes**

Text mode displays have been in common use much longer than graphics displays, and are still very useful in applications which do not require graphics (or in which simple block graphics will suffice). Text modes place a much lower burden on the system processor, which only has to manipulate ASCII character codes rather than individual pixels.

In standard text modes, the display screen is divided into 25 lines of text, with either 40 or 80 columns of text per line. In 40-column modes, 1000 characters can be displayed on the screen; in 80-column modes, 2000 characters can be displayed (see Figure 2-6). Two bytes of display memory are used to define each character; the first byte, mapped at an even memory address, contains the ASCII character code, and the second byte, mapped at an odd memory address, contains color information called the **Character Attribute**. 2000 bytes of display memory are needed to define one 40 column page, or 4000 bytes to define one 80 column page. A page of display memory is 4096 bytes long, leaving 96 bytes unused at the end of each page.

#### Preserving display memory during a Mode Select

BIOS mode select functions will optionally preserve the contents of display memory if the desired mode number is ORed with the value 80h before the BIOS call is made. This capability is limited in text modes, however, since these modes utilize display memory plane 2 for storage of character generators. It is therefore not possible to enter and exit a text mode without corrupting at least part of the display memory.

Figure 2-6. Display memory format-text modes

## **Character Generators**

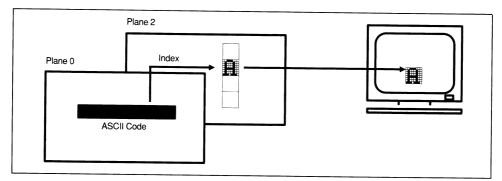

To convert an ASCII character code into an array of pixels on the screen, a translation table or **Character Generator** is used. On older display adapters such as MDA and CGA, the character generator is located in ROM (Read Only Memory.) The VGA does not use a character generator ROM; instead, character generator data is loaded into plane 2 of the display RAM. This feature makes it easy for custom character sets to be loaded. Multiple character sets (up to 8) may reside in RAM simultaneously. A set of BIOS services are available for easy loading of character sets. Figure 2-7 illustrates how character codes are used as an index into a character generator.

Figure 2-7. Character code as index into character generator

Either one or two character generators may be active, giving the VGA the capability to display up to 512 different characters on the screen simultaneously. When two character generators are active, a bit in each character attribute byte selects which character set will be used for that character. A register in the Sequencer is used to select the two active character generators.

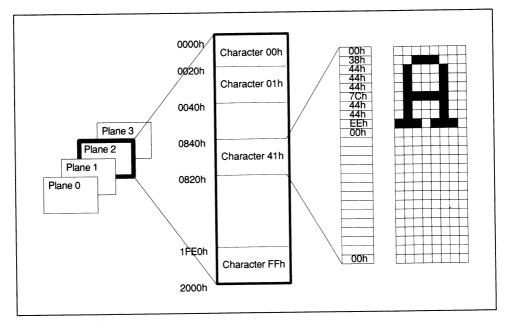

Character width is fixed at eight pixels. Character height is selectable from 1 to 32 pixels through an output register. Figure 2-8 illustrates how a character generator is designed.

Figure 2-8. Character generator format

The location of character generators in memory is shown in Table 2-1. Regardless of the character height which is being used, characters always begin on 32-byte boundaries. For instance, the 8 pixel by 14 pixel character set requires 14 bytes per character, so 18 bytes per character go unused in the character generator.

| Character Map A            | Character Map E            |

|----------------------------|----------------------------|

| 0000h to 001Fh - Char. 0   | 2000h to 201Fh - Char. 0   |

| 0020h to 003Fh - Char. 1   | 2020h to 203Fh - Char. 1   |

| 0040h to 005Fh - Char. 2   | 2040h to 205Fh - Char. 2   |

| 1FE0h to 1FFFh - Char. 255 | 3FE0h to 3FFFh - Char. 255 |

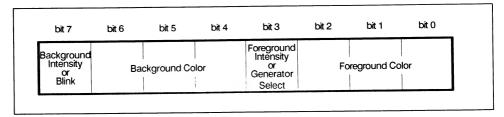

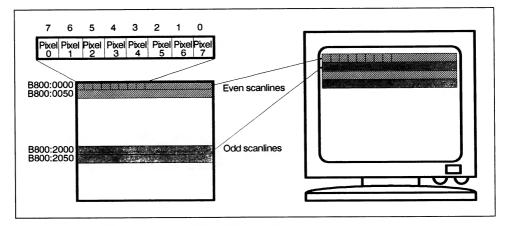

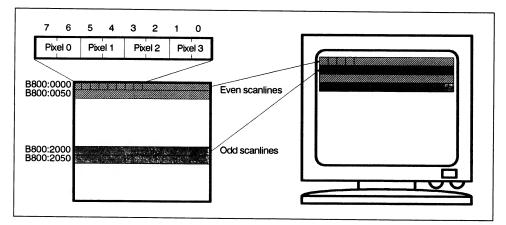

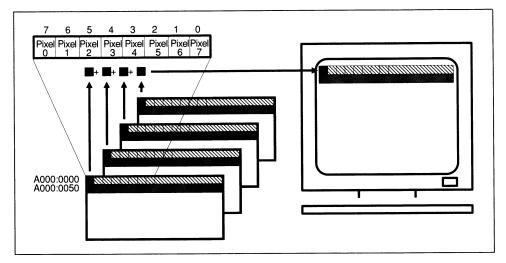

| Character Map B            | <b>Character Map F</b>     |