Reference Nultiprotocol Adapter A

The warranty terms and conditions applicable in the country of purchase in respect of an IBM product are available from the supplier. Please retain them with your proof of purchase.

No statements contained in this documentation shall affect the statutory rights of consumers.

#### First Edition (April, 1987)

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time.

It is possible that this publication may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

The publication of the information contained herein is not intended to and does not convey any rights or licenses under any IBM patents or copyrights.

Requests for copies of this publication and for technical information about IBM products should be made to your IBM Authorized Dealer or your IBM Marketing Representative.

©Copyright International Business Machines Corporation 1987. All rights reserved. No part of this work may be reproduced or distributed in any form or by any means without prior permission in writing from the IBM Corporation.

# **Contents**

| Description 1                        |

|--------------------------------------|

| Control Signal Interface             |

| Protocol Controllers                 |

| Programmable Option Select (POS)     |

| POS Registers 0 and 1                |

| POS Register 2                       |

| POS Register 3                       |

| Asynchronous Communications          |

| 16550 Description                    |

| Programming the 16550 7              |

| Transmitter Holding Register 7       |

| Receiver Buffer Register 7           |

| Programmable Baud-Rate Generator     |

| Interrupt Enable Register            |

| Interrupt Identification Register    |

| Line Control Register                |

| Modem Control Register               |

| Line Status Register                 |

| Modem Status Register                |

| Scratch Pad Register 17              |

| Address and Interrupt Assignments    |

| Serial Data Format                   |

| Binary Synchronous Communications 21 |

| 8251A Description                    |

| Programming the 8251A 22             |

| Mode and Command Instructions 22     |

| Asynchronous Mode 23                 |

| Synchronous Mode 25                  |

| Command Instructions 28              |

| 8254 Description                     |

| Counter Descriptions                 |

| Programming the 8254 31              |

| Write Operations 32                  |

| Read Operations 34                   |

| Simple Read Operation                |

| Counter Latch Command                |

| Read-Back Command 36                 |

| Counter Status Command               |

| Mode Definitions                                   | 39 |

|----------------------------------------------------|----|

| Mode 0 - Interrupt on Terminal Count               | 40 |

| Mode 1 - Hardware Retriggerable One-Shot           | 40 |

| Mode 2 - Rate Generator                            | 41 |

| Mode 3 - Square Wave Mode                          | 42 |

| Mode 4 - Programmable Triggered Strobe             | 43 |

| Mode 5 - Hardware Triggered Strobe (Retriggerable) | 43 |

| Operations Common to All BSC Modes                 | 45 |

| Gate                                               | 45 |

| Counter                                            | 45 |

| Typical Programming Sequence                       | 46 |

| Address and Interrupt Assignments                  | 48 |

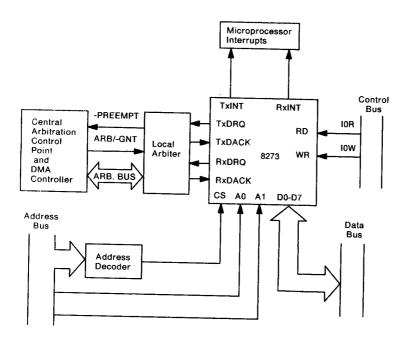

| SDLC/HDLC Communications                           | 49 |

| 8273 Description                                   | 49 |

| System Interface                                   | 50 |

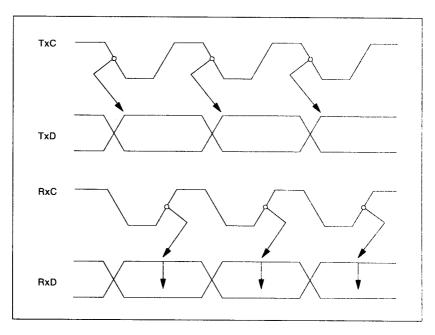

| Modem Interface                                    | 55 |

| Programming the 8273                               | 58 |

| 8273 Status Register                               | 58 |

| Operating Mode Register                            | 59 |

| Serial I/O Mode Register                           | 61 |

| Data Transfer Mode Register                        | 61 |

| 8273 Command Descriptions                          | 66 |

| Initialization/Configuration Commands              | 66 |

| Receive Commands                                   | 67 |

| Transmit Commands                                  | 72 |

| Reset Command                                      | 74 |

| Modem Control Commands                             | 75 |

| 8255 I/O Port Assignment                           | 75 |

| Address, DMA, and Interrupt Assignments            | 77 |

| DMA Assignment                                     | 77 |

| Interrupt Information                              | 77 |

| RS-232-C Interface                                 | 78 |

| Modem Control Input Signals                        | 78 |

| Modem Control Output Signals                       | 79 |

| Voltage Interchange Information                    | 80 |

| Connector                                          | 81 |

|                                                    |    |

| Index                                              | 83 |

# **Figures**

| 1.                                                                                       | Multiprotocol Adapter/A Block Diagram                                                                                                                                                                                                                                                                                              | 1                                                                                |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.                                                                                       | Register Selection                                                                                                                                                                                                                                                                                                                 | 3                                                                                |

| 3.                                                                                       | POS Register 2                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 4.                                                                                       | Mode Selection                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 5.                                                                                       | POS Register 3                                                                                                                                                                                                                                                                                                                     | 5                                                                                |

| 6.                                                                                       | Transmitter Holding Register                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 7.                                                                                       | Receiver Buffer Register                                                                                                                                                                                                                                                                                                           | 7                                                                                |

| 8.                                                                                       | Divisor Latch (LSB)                                                                                                                                                                                                                                                                                                                | 8                                                                                |

| 9.                                                                                       | Divisor Latch (MSB)                                                                                                                                                                                                                                                                                                                | 8                                                                                |

| 10.                                                                                      | Baud Rates at 1.8432 MHz                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 11.                                                                                      | Interrupt Enable Register                                                                                                                                                                                                                                                                                                          |                                                                                  |

| 12.                                                                                      | Interrupt Identification Register                                                                                                                                                                                                                                                                                                  | 10                                                                               |

| 13.                                                                                      | Interrupt Control Functions                                                                                                                                                                                                                                                                                                        | 11                                                                               |

| 14.                                                                                      | Line Control Register                                                                                                                                                                                                                                                                                                              | 11                                                                               |

| 15.                                                                                      | Word Length (Stop Bits)                                                                                                                                                                                                                                                                                                            | 12                                                                               |

| 16.                                                                                      | Word Length                                                                                                                                                                                                                                                                                                                        | 13                                                                               |

| 17.                                                                                      | Modem Control Register                                                                                                                                                                                                                                                                                                             | 13                                                                               |

| 18.                                                                                      | Line Status Register                                                                                                                                                                                                                                                                                                               | 15                                                                               |

| 19.                                                                                      | Modem Status Register                                                                                                                                                                                                                                                                                                              | 16                                                                               |

| 20.                                                                                      | I/O Address and Interrupt Level Assignments (Async)                                                                                                                                                                                                                                                                                |                                                                                  |

| ZU.                                                                                      | "O Address and interrupt Level Assignments (Async)                                                                                                                                                                                                                                                                                 | 18                                                                               |

| 20.<br>21.                                                                               | Serial Data Format                                                                                                                                                                                                                                                                                                                 | 18<br>20                                                                         |

|                                                                                          | Serial Data Format                                                                                                                                                                                                                                                                                                                 | 20                                                                               |

| 21.                                                                                      | Serial Data Format                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| 21.<br>22.                                                                               | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format                                                                                                                                                                                                                                                         | 20<br>22<br>24                                                                   |

| 21.<br>22.<br>23.                                                                        | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits                                                                                                                                                                                                                                     | 20<br>22                                                                         |

| 21.<br>22.<br>23.<br>24.                                                                 | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format                                                                                                                                                                                                                                                         | 20<br>22<br>24<br>25                                                             |

| 21.<br>22.<br>23.<br>24.<br>25.                                                          | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor                                                                                                                                                                                              | 20<br>22<br>24<br>25<br>25                                                       |

| 21.<br>22.<br>23.<br>24.<br>25.                                                          | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format                                                                                                                                                                  | 20<br>22<br>24<br>25<br>25<br>25                                                 |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.                                                   | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length                                                                                                                                                 | 20<br>22<br>24<br>25<br>25<br>25<br>27                                           |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.<br>27.                                            | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format                                                                                                                      | 20<br>22<br>24<br>25<br>25<br>25<br>27<br>27                                     |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.<br>27.<br>28.                                     | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format Status Read Format                                                                                                   | 20<br>22<br>24<br>25<br>25<br>25<br>27<br>27<br>28                               |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.<br>27.<br>28.<br>29.                              | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format                                                                                                                      | 20<br>22<br>24<br>25<br>25<br>27<br>27<br>28<br>29                               |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.<br>27.<br>28.<br>29.                              | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format Status Read Format Control Word Register Select Counter                                                              | 20<br>22<br>24<br>25<br>25<br>27<br>27<br>27<br>28<br>29<br>31                   |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.<br>27.<br>28.<br>29.<br>30.<br>31.                | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format Status Read Format Control Word Register Select Counter Read/Write Options                                           | 20<br>22<br>24<br>25<br>25<br>27<br>27<br>28<br>29<br>31<br>32<br>32             |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.<br>27.<br>28.<br>29.<br>30.<br>31.<br>32.         | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format Status Read Format Control Word Register Select Counter Read/Write Options Counter Mode Selection                    | 20<br>22<br>24<br>25<br>25<br>27<br>27<br>28<br>29<br>31<br>32<br>32<br>32       |

| 21.<br>22.<br>23.<br>24.<br>25.<br>26.<br>27.<br>28.<br>29.<br>30.<br>31.<br>32.         | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format Status Read Format Control Word Register Select Counter Read/Write Options Counter Mode Selection Sequence Example 1 | 20<br>22<br>24<br>25<br>25<br>27<br>27<br>28<br>29<br>31<br>32<br>32             |

| 21.<br>222.<br>23.<br>24.<br>25.<br>26.<br>27.<br>28.<br>29.<br>30.<br>31.<br>32.<br>33. | Serial Data Format Typical Data Block Asynchronous Mode Instruction Format Number of Stop Bits Character Rate Factor Baud Rate Factor BSC Mode Instruction Format Character Length Command Instruction Format Status Read Format Control Word Register Select Counter Read/Write Options Counter Mode Selection                    | 20<br>22<br>24<br>25<br>25<br>27<br>27<br>28<br>29<br>31<br>32<br>32<br>32<br>33 |

| 39. | Counter Latch Command Format                  | 35 |

|-----|-----------------------------------------------|----|

| 40. | Counter Selection                             | 35 |

| 41. | Read-Back Command Format                      | 37 |

| 42. | Counter Status Format                         | 37 |

| 43. | Null Count Operation                          | 38 |

| 44. | Read-Back Command Example                     | 39 |

| 45. | GATE Operations Summary                       | 44 |

| 46. | Minimum and Maximum Initial Counts            | 44 |

| 47. | Port A Assignments                            | 46 |

| 48. | Port B Assignments                            | 47 |

| 49. | Port C Assignments (Input)                    | 47 |

| 50. | Port C Assignments (Output)                   | 47 |

| 51. | I/O Address Assignemnts (BSC)                 | 48 |

| 52. | SDLC Frame Format                             | 49 |

| 53. | 8273 Register Selection                       | 50 |

| 54. | DMA, Interrupt-Driven System                  | 52 |

| 55. | 8273 Port A (Input)                           | 55 |

| 56. | 8273 Port B (Output)                          | 56 |

| 57. | Transmit/Receive Timing                       | 57 |

| 58. | Status Register Format                        | 58 |

| 59. | Operating Mode Register                       | 59 |

| 60. | Serial I/O Mode Register                      | 61 |

| 61. | Data Transfer Mode Register                   | 61 |

| 62. | 1-Bit Delay Mode Register                     | 62 |

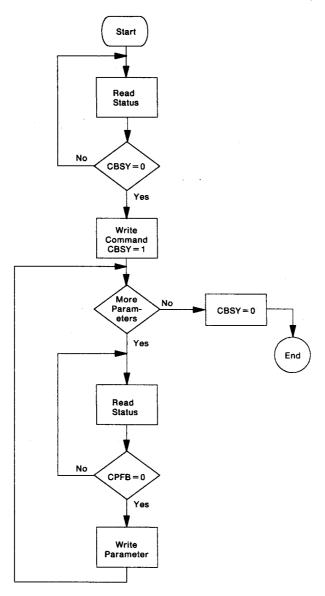

| 63. | Command Phase Flowchart                       | 63 |

| 64. | Command Summary Key                           | 66 |

| 65. | Initialization/Configuration Command Summary  | 67 |

| 66. | Receive Command Summary                       | 68 |

| 67. | Interrupt Result Code                         | 68 |

| 68. | Receiver Interrupt Result Codes (RIC)         | 69 |

| 69. | Transmit Command Summary                      | 73 |

| 70. | Transmit Interrupt Result (TIC) Codes         | 73 |

| 71. | Port A (Input) Modem Control Command Summary  | 75 |

| 72. | Port B (Output) Modem Control Command Summary | 75 |

| 73. | Port A Assignments                            | 76 |

| 74. | Port B Assignments                            | 76 |

| 75. | Port C Assignments (Input)                    | 76 |

| 76. | Port C Assignments (Output)                   | 76 |

| 77. | I/O Address Assignments (SDLC/HDLC)           | 77 |

| 78. | Voltage Levels                                | 80 |

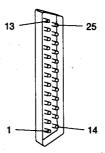

| 79. | Pin Locations                                 | 81 |

| 80. | EIA/CCITT Pin Assignments                     |    |

# **Description**

The Multiprotocol Adapter/A provides multiple communications features and is designed to work in systems that use the Micro Channel<sup>TM</sup> architecture. For more information about the channel, refer to the system *Technical Reference* manual.

The adapter provides the following features:

- ISO/CCITT level 2 and level 1 protocol:

- Level 2: Asynchronous, Bisynchronous (BSC), and

Synchronous Data Link Control (SDLC)/High-level Data Link

Control (HDLC) protocol

- Level 1: EIA RS-232C interface.

- One 25-pin, D-type connector

- Internal wrap-back test loop for diagnostics

- Programmable arbitration level for direct DMA transfers on SDLC/HDLC communications.

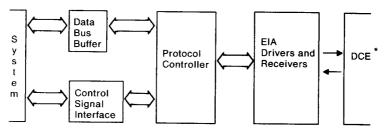

The following is a block diagram of the adapter:

<sup>\*</sup> Data Communications Equipment

Figure 1. Multiprotocol Adapter/A Block Diagram

Micro Channel is a trademark of the International Business Machines corporation.

# **Control Signal Interface**

The control signal interface performs the following functions:

- I/O read and write signal generation and wait-state insertion

- Programmable Option Select (POS)

- Local Arbiter for DMA operation

- Address decode and protocol mode selection.

#### **Protocol Controllers**

Communications protocols are performed by the following controllers and circuits on the adapter:

- NS16550 Asynchronous Communications Element for ASYNC

- 8251A Universal Synchronous/Asynchronous Receiver/Transmitter (USART) for BSC

- 8254 Programmable Interval Timer (provides time-outs and interrupt functions in synchronous communications)

- 8273 SDLC/HDLC Protocol Controller

- 8255-5 Programmable Peripheral Interface (for expanded modem interface and diagnostic aid in synchronous communications)

- Multiplexer.

# **Programmable Option Select (POS)**

Before the adapter can be used it must be initialized by the system. The Programmable Option Select (POS) registers eliminate the need to manually initialize the adapter for a particular configuration.

The adapter contains several configurable options. These options are controlled by the POS registers.

**Warning:** IBM recommends that programmable options be set only through the System Configuration Utilities. Direct setting of the POS registers and/or CMOS RAM POS parameters can result in multiple assignment of the same system resource, improper operation of the feature, loss of data, or possible damage to the system or options. If application programs use adapter identification (ID) information, compatibility problems between systems or options may result.

The POS registers are only accessible by the system when -CD SETUP on the channel is active. Address lines A0 through A2 select the registers as shown in the following figure:

| -CD SETUP | Address Line<br>A2 A1 A0 | Register                          |

|-----------|--------------------------|-----------------------------------|

| L         | LLL                      | POS Register 0 - Adapter ID       |

| L         | LLH                      | POS Register 1 - Adapter ID       |

| L         | LHL                      | POS Register 2 - Option<br>Select |

| L         | L Н Н                    | POS Register 3 - Option<br>Select |

| Н         | X X X                    | Normal Operation                  |

Figure 2. Register Selection

# POS Registers 0 and 1

These read-only registers contain the hard-wired adapter ID.

When -CD SETUP is active, the hard-wired adapter ID (hex DEFF) is read by the system. POS Register 1 is the most-significant byte and POS Register 0 is the least-significant byte of the adapter ID.

# **POS Register 2**

Programmable adapter options are written to this read/write register. Bit definitions for POS register 2 are shown in the following figure:

| Function       |                                          |

|----------------|------------------------------------------|

| Reserved = 0   |                                          |

| Reserved = 1   |                                          |

| Mode Selection |                                          |

| Adapter Enable |                                          |

|                | Reserved = 0 Reserved = 1 Mode Selection |

Figure 3. POS Register 2

#### Notes:

- Bits 0 and 4 are cleared to 0 during power-on.

- The alternate BSC port has the same I/O address as the SDLC port (0380-038F). The alternate SDLC port has the same I/O address as the BSC port (03A0-03AF).

- Bits 7 6 Reserved. These bits are always cleared to 0.

- Bit 5 Reserved. This bit is always set to 1.

- Bits 4 1 These bits select modes as shown in the following figure:

| 4321 | Mode Selected  |  |

|------|----------------|--|

| 0000 | Serial 1       |  |

| 0001 | Serial 2       |  |

| 0010 | Serial 3       |  |

| 0011 | Serial 4       |  |

| 0100 | Serial 5       |  |

| 0101 | Serial 6       |  |

| 0110 | Serial 7       |  |

| 0111 | Serial 8       |  |

| 1000 | SDLC           |  |

| 1001 | Alternate SDLC |  |

| 1010 | Reserved       |  |

| 1011 | Reserved       |  |

| 1100 | BSC            |  |

| 1101 | Alternate BSC, |  |

| 1110 | Reserved       |  |

| 1111 | Reserved       |  |

Figure 4. Mode Selection

When this bit is set to 1, the adapter is enabled. When this bit is cleared to 0 the adapter is disabled. When the adapter is disabled, it does not respond to any I/O or Memory commands except the Memory Refresh command and POS reads and writes. No interrupt requests are driven. A 'channel reset' clears this bit to 0.

### **POS Register 3**

Programmable adapter options are written to this read/write register. Bit definitions for POS register 3 are shown in the following figure:

| Bit   | Function          |  |

|-------|-------------------|--|

| 7 - 4 | Reserved          |  |

| 3 - 0 | Arbitration Level |  |

Figure 5. POS Register 3

Note: All bits in POS Register 3 are cleared to 0 during power-on.

- Bits 7 4 Reserved. These bits are always cleared to 0.

- Bits 3 0 These bits specify the arbitration priority level for the adapter. The highest priority is selected with the binary decode of 0000. When competing for the channel, the adapter places this value on the '-arb' lines. If no other device places a higher priority request (lower binary value) on these lines, the adapter wins the arbitration.

Note: Arbitration level 1 is recommended for primary SDLC communications.

# **Asynchronous Communications**

The asynchronous communications portion of the adapter is fully programmable.

The major component of this portion of the adapter is a NS16550 LSI Asynchronous Communications Controller. The NS16550 controller is functionally compatible to the NS16450 controller. To programs, the NS16550 appears to be identical to the IBM Personal Computer AT® Serial/Parallel adapter. Support for the controller on the adapter is restricted to the functions which are identical to the NS16450. Using the controller in the FIFO mode may result in non-detectable data errors.

# 16550 Description

The NS 16550 adds and removes a start bit, parity bit, and stop bits. A programmable baud-rate generator allows operation from 50 baud to 19,200 baud. The adapter supports 5-, 6-, 7-, and 8-bit characters with 1, 1-1/2, or 2 stop bits. A fully prioritized interrupt system controls transmit, receive, error, line status, and data set interrupts. Diagnostic capabilities provide loopback functions of transmit/receive and input/output signals. Total system load (for example, competing I/O devices) will limit the practical total number of concurrent ports and the speed of each port. Other features include:

- Full double buffering in the character mode, eliminating the need for precise synchronization

- False-start bit detection

- Line-break generation and detection

- Modem control functions.

AT is a registered trademark of the International Business Machines Corporation.

# **Programming the 16550**

The NS16550 controller has a number of accessible registers. The system uses these registers to control adapter operations and to transmit and receive data.

#### **Transmitter Holding Register**

The Transmitter Holding register contains the character to be sent. Bit 0 is the least-significant bit and the first bit sent serially as shown in the following figure:

| Bit | Function   |  |

|-----|------------|--|

| 7   | Data Bit 7 |  |

| 6   | Data Bit 6 |  |

| 5   | Data Bit 5 |  |

| 4   | Data Bit 4 |  |

| 3   | Data Bit 3 |  |

| 2   | Data Bit 2 |  |

| 1   | Data Bit 1 |  |

| 0   | Data Bit 0 |  |

Figure 6. Transmitter Holding Register

# **Receiver Buffer Register**

The Receiver Buffer register contains the received character. Bit 0 is the least-significant bit and the first bit received serially as shown in the following figure:

| Bit | Function   |  |

|-----|------------|--|

| 7   | Data Bit 7 |  |

| 6   | Data Bit 6 |  |

| 5   | Data Bit 5 |  |

| 4   | Data Bit 4 |  |

| 3   | Data Bit 3 |  |

| 2   | Data Bit 2 |  |

| 1   | Data Bit 1 |  |

| 0   | Data Bit 0 |  |

Figure 7. Receiver Buffer Register

#### **Programmable Baud-Rate Generator**

The controller has a programmable baud-rate generator that can divide the clock input (1.8432 MHz) by any divisor from 1 to 65,535. The output frequency of the baud-rate generator is the baud rate multiplied by 16. Two 8-bit divisor latches store the divisor in a 16-bit binary format. These divisor latches must be loaded during adapter initialization to ensure desired operation of the baud-rate generator. When either of the divisor latches is loaded, a 16-bit baud counter is immediately loaded. This prevents long counts on the first load.

The divisor latches are shown in the following figures:

### **Divisor Latch (Least Significant Byte)**

| Bit | Function |   |

|-----|----------|---|

| 7   | Bit 7    |   |

| 6   | Bit 6    |   |

| 5   | Bit 5    |   |

| 4   | Bit 4    | į |

| 3   | Bit 3    |   |

| 2   | Bit 2    | j |

| 1   | Bit 1    | ļ |

| 0   | Bit 0    |   |

Figure 8. Divisor Latch (LSB)

# **Divisor Latch (Most Significant Byte)**

| Bit | Function |  |

|-----|----------|--|

| 7   | Bit 7    |  |

| 6   | Bit 6    |  |

| 5   | Bit 5    |  |

| 4   | Bit 4    |  |

| 3   | Bit 3    |  |

| 2   | Bit 2    |  |

| 1   | Bit 1    |  |

| 0   | Bit 0    |  |

Figure 9. Divisor Latch (MSB)

Figure 10 on page 9 illustrates the use of the baud-rate generator with a frequency of 1.8432 MHz. For baud rates of 19,200 and below, the error obtained is minimal.

Note: In no case should the data speed be greater than 19,200 baud.

| Desired<br>Baud<br>Rate | Divisor Use<br>Generate 1<br>(Decimal) |      | Percent Error<br>Difference Between<br>Desired and Actual |  |

|-------------------------|----------------------------------------|------|-----------------------------------------------------------|--|

| 50                      | 2304                                   | 0900 |                                                           |  |

| 75                      | 1536                                   | 0600 |                                                           |  |

| 110                     | 1047                                   | 0417 | 0.026                                                     |  |

| 134.5                   | 857                                    | 0359 | 0.058                                                     |  |

| 150                     | 768                                    | 0300 |                                                           |  |

| 300                     | 384                                    | 0180 |                                                           |  |

| 600                     | 192                                    | 00C0 |                                                           |  |

| 1200                    | 96                                     | 0060 |                                                           |  |

| 1800                    | 64                                     | 0040 |                                                           |  |

| 2000                    | 58                                     | 003A | 0.69                                                      |  |

| 2400                    | 48                                     | 0030 |                                                           |  |

| 3600                    | 32                                     | 0020 |                                                           |  |

| 4800                    | 24                                     | 0018 |                                                           |  |

| 7200                    | 16                                     | 0010 |                                                           |  |

| 9600                    | 12                                     | 000C |                                                           |  |

| 19200                   | 6                                      | 0006 |                                                           |  |

Figure 10. Baud Rates at 1.8432 MHz

## Interrupt Enable Register

This 8-bit register allows the four types of controller interrupts to separately activate the 'chip-interrupt' output signal. The interrupt system can be totally disabled by clearing bits 0 through 3 of the Interrupt Enable register. Similarly, by setting the appropriate bits of this register to 1, selected interrupts can be enabled. Disabling the interrupts will inhibit the 'chip-interrupt' output signal from the controller. All other system functions operate normally, including the setting of the Line Status and Modem Status registers.

| Bit   | Function                                     |

|-------|----------------------------------------------|

| 7 - 4 | Reserved = 0                                 |

| 3     | Modem-Status Interrupt                       |

| 2     | Receiver-Line-Status Interrupt               |

| 1     | Transmitter-Holding-Register-Empty Interrupt |

| 0     | Received Data Available Interrupt            |

Figure 11. Interrupt Enable Register

| Bits 7 - 4 | Reserved. These bits are always cleared to 0.                      |

|------------|--------------------------------------------------------------------|

| Bit 3      | When set to 1, this bit enables the modem-status interrupt.        |

| Bit 2      | When set to 1, this bit enables the receiver-line-status interrupt |

Bit 1 When set to 1, this bit enables the

transmitter-holding-register-empty interrupt.

When set to 1, this bit enables the received-data-available interrupt.

## Interrupt Identification Register

In order to minimize programming overhead during data character transfers, the controller prioritizes interrupts into four levels:

- Priority 1 Receiver-line-status

- Priority 2 Received-data-available

- Priority 3 Transmitter-holding-register-empty

- Priority 4 Modem status.

Information about a pending interrupt is stored in the Interrupt Identification register. When the Interrupt Identification register is addressed, the pending interrupt with the highest priority is held and no other interrupts are acknowledged until the system microprocessor services that interrupt.

| Bit   | Function              |  |

|-------|-----------------------|--|

| 7 - 3 | Reserved = 0          |  |

| 2     | Interrupt ID, Bit 1   |  |

| 1     | Interrupt ID, Bit 0   |  |

| 0     | Interrupt Pending = 0 |  |

Figure 12. Interrupt Identification Register

- Bits 7 3 Reserved. These bits are always cleared to 0.

- Bits 2 1 These two bits identify the pending interrupt with the highest priority as shown in Figure 13 on page 11.

- Bit 0 When this bit is set to 1, no interrupt is pending and polling (if used) continues. When this bit is cleared to 0, an interrupt is pending and the contents of this register can be used as a pointer to the appropriate interrupt service routine.

This bit can be used in either hard-wired, prioritized, or polled conditions to indicate if an interrupt is pending.

Bits 2 - 0 select Interrupt Control Functions as shown in the following figure:

| Bits<br>2 1 0 | Priority | Туре                                        | Cause                                                      | Interrupt Reset<br>Control                                                                        |

|---------------|----------|---------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 001           | -        | None                                        | None                                                       | -                                                                                                 |

| 110           | Highest  | Receiver Line<br>Status                     | Overrun, Parity, or<br>Framing Error or<br>Break Interrupt | Read the Line<br>Status<br>Register                                                               |

| 100           | Second   | Received Data<br>Available                  | Data in Receiver<br>Buffer                                 | Read the<br>Receiver<br>Buffer<br>Register                                                        |

| 010           | Third    | Transmitter<br>Holding<br>Register<br>Empty | Transmitter<br>Holding Register is<br>Empty                | Read Interrupt<br>Identification<br>Register or<br>Write to<br>Transmitter<br>Holding<br>Register |

| 000           | Fourth   | Modem Status                                | Change in Signal<br>Status from Modem                      | Read the<br>Modem Status<br>Register                                                              |

Figure 13. Interrupt Control Functions

# **Line Control Register**

The format of asynchronous communications is programmed through the Line Control register.

| Bit | Function                  |

|-----|---------------------------|

| 7   | Divisor Latch Access Bit  |

| 6   | Set Break                 |

| 5   | Stick Parity              |

| 4   | Even Parity Select        |

| 3   | Parity Enable             |

| 2   | Number of Stop Bits       |

| 1   | Word Length Select, Bit 1 |

| 0   | Word Length Select, Bit 0 |

Figure 14. Line Control Register

This bit must be set to 1 during a read or write operation to gain access to the divisor latches of the baud-rate generator. It must be cleared to 0 to gain access to the Receiver Buffer, Transmitter Holding, or Interrupt Enable registers.

When this bit is set to 1, set-break is enabled and serial output is forced to the spacing state and remains there regardless of other transmitter activity. When this bit is cleared to 0, set-break is disabled.

Bit 5 When bits 5, 4, and 3 are set to 1, the parity bit is sent and checked as a logical 0. When bits 5 and 3 are set to 1, and bit 4 is cleared to 0, the parity bit is sent and checked as a logical 1.

When this bit and bit 3 are set to 1, an even number of logical 1's are transmitted and checked in the data word bits and parity bit. When this bit is cleared to 0, and bit 3 is set to 1, an odd number of logical 1's are transmitted and checked in the data word bits and parity bit.

When set to 1, a parity bit is generated (transmit data) or checked (receive data) between the last data word bit and stop bit. (The parity bit is used to produce an even or odd number of 1's when the data-word bits and the parity bit are summed.)

Bit 2 This bit, along with bits 0 and 1, specifies the number of stop bits in each serial character that is sent or received as shown in the following figure:

| Bit 2 | Word<br>Length * | Number of<br>Stop Bits |

|-------|------------------|------------------------|

| 0     | N/A              | 1                      |

| 1     | 5-Bits           | 1-1/2                  |

| 1     | 6-Bits           | 2                      |

| 1     | 7-Bits           | 2                      |

| 1     | 8-Bits           | 2                      |

Figure 15. Word Length (Stop Bits)

Bits 0 - 1 These two bits specify the number of bits in each serial character that is sent or received. Word length is selected as shown in the following figure:

| Bits<br>1 0 | Word Length |  |

|-------------|-------------|--|

| 0 0         | 5-Bits      |  |

| 0 1         | 6-Bits      |  |

| 10          | 7-Bits      |  |

| 11          | 8-Bits      |  |

Figure 16. Word Length

#### **Modem Control Register**

This 8-bit register controls the data exchange with the modem, data set, or peripheral device emulating a modem.

| Bit   | Function            |  |

|-------|---------------------|--|

| 7 - 5 | Reserved = 0        |  |

| 4     | Loop                |  |

| 3     | Out 2               |  |

| 2     | Out 1               |  |

| 1     | Request-to-Send     |  |

| 0     | Data-Terminal-Ready |  |

Figure 17. Modem Control Register

# Bits 7 - 5 Reserved. These bits are always cleared to 0.

- Bit 4 This bit provides a loopback feature for diagnostic testing of the adapter. When bit 4 is set to 1:

- Transmitter-serial-output is set to the marking state

- Receiver-serial-input is disconnected

- Output of the Transmitter Shift register is "looped back" to the Receiver Shift register input

**Note:** The Transmitter and Receiver Shift registers are not accessible NS16550 registers.

The modem control inputs (CTS, DSR, DCD, and RI) are disconnected

- The modem control outputs (DTR, RTS, OUT 1, and OUT 2) are internally connected to the four modem control inputs

- The modem control output pins are forced inactive.

When the adapter is in the diagnostic mode, transmitted data is immediately received. This feature allows the system microprocessor to verify the transmit-data and receive-data paths of the adapter.

When the adapter is in the diagnostic mode, the receiver and transmitter interrupts are fully operational. The modem control interrupts are also operational, but their sources are the lower four bits of the Modem Control register instead of the four modem control input signals. The interrupts are still controlled by the Interrupt Enable register.

- This bit controls the 'output 2' (OUT 2) signal which is an auxiliary user-designated interrupt enable signal. OUT 2 is used to control the interrupt signal to the channel. Setting this bit to 1 enables the interrupt. Clearing this bit to 0 disables the interrupt.

- This bit controls the 'output 1' (OUT 1) signal which is an auxiliary user-designated output signal. When set to 1, OUT 1 is forced active. When cleared to 0, OUT 1 is forced inactive.

- This bit controls the 'request-to-send' (RTS) controller output signal. When set to 1, RTS is forced active. When cleared to 0, RTS is forced inactive.

- This bit controls the 'data-terminal-ready' (DTR) controller output signal. When set to 1, DTR is forced active. When cleared to 0, DTR is forced inactive.

#### **Line Status Register**

This 8-bit register provides the system microprocessor with status information about the data transfer.

| Bit | Function                           |

|-----|------------------------------------|

| 7   | Reserved = 0                       |

| 6   | Transmitter Shift Register Empty   |

| 5   | Transmitter Holding Register Empty |

| 4   | Break Interrupt                    |

| 3   | Framing Error                      |

| 2   | Parity Error                       |

| 1   | Overrun Error                      |

| 0   | Data Ready                         |

Figure 18. Line Status Register

Bit 7 Reserved. This bit is always cleared to 0.

Bit 6 This bit is set to 1 when the Transmitter Holding register and the Transmitter Shift register are both empty. This bit is cleared to 0 when either the Transmitter Holding register or the Transmitter Shift register contains a data character.

Bit 5 This bit indicates that the adapter is ready to accept a new character for transmission. This bit is set to 1 when a character is transferred from the Transmitter Holding register into the Transmitter Shift register. This bit is cleared to 0 when the system microprocessor loads the Transmitter Holding register.

This bit also causes the adapter to issue an interrupt to the system microprocessor when bit 1 in the Interrupt Enable register is set to 1.

This bit is set to 1 when the received data input is held in the spacing state for longer than a fullword transmission (the total time of the start bit + data bits + parity + stop bits).

Note: Bits 1 through 4 are the error conditions that produce a receiver line-status interrupt whenever any of the corresponding conditions are detected.

- Bit 3 This bit is set to 1 when the stop bit following the last data bit or parity bit is at a spacing level. This indicates that the received character did not have a valid stop bit.

- This bit is set to 1 when a parity error is detected (the received character does not have the correct even or odd parity, as selected by the even-parity-select bit).

This bit is cleared to 0 when the system microprocessor reads the contents of the Line Status register.

- When it is set to 1, this bit indicates that data in the Receiver Buffer register was not read by the system microprocessor before the next character was transferred into the Receiver Buffer register, destroying the previous character. This bit is cleared to 0 when the system microprocessor reads the contents of the Line Status register.

- Bit 0 This bit is set to 1 when a complete incoming character has been received and transferred into the Receiver Buffer register. This bit is cleared to 0 by reading the Receiver Buffer register.

## Modem Status Register

This 8-bit register provides the current state of the control lines from the modem (or external device) to the system microprocessor. In addition, bits 3 - 0 of the this register provide change information. These four bits are set to logical 1 whenever a control input from the modem changes state. They are reset to logical 0 whenever the system microprocessor reads this register.

| Bit | Function                     | 1   |

|-----|------------------------------|-----|

| 7   | Data-Carrier-Detect          |     |

| 6   | Ring Indicator               | - 1 |

| 5   | Data-Set-Ready               | 1   |

| 4   | Clear-to-Send                | i   |

| 3   | Delta-Data-Carrier-Detect    |     |

| 2   | Trailing Edge Ring Indicator |     |

| 1   | Delta-Data-Set-Ready         |     |

| 0   | Delta-Clear-to-Send          |     |

Figure 19. Modem Status Register

- Bit 7 This bit is the inverted 'data-carrier-detect' (DCD) modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 3 in the Modem Control register.

- Bit 6 This bit is the inverted 'ring-indicator' (RI) modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 2 in the Modem Control register.

- Bit 5 This bit is the inverted 'data-set-ready' (DSR) modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 0 in the Modem Control register.

- Bit 4 This bit is the inverted 'clear-to-send' (CTS) modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 1 in the Modem Control register.

- When set to 1, this bit indicates that the 'data-carrier-detect' modem control input signal has changed state since the last time it was read by the system microprocessor.

**Note:** Whenever bit 0, 1, 2, or 3 is set to 1, a modem status interrupt is generated.

- When set to 1, this bit indicates that the 'ring-indicator' modem control input signal has changed from an active condition to an inactive condition.

- Bit 1 When set to 1, this bit indicates that the 'data-set-ready' modem control input signal has changed state since the last time it was read by the system microprocessor.

- When set to 1, this bit indicates that the 'clear-to-send' modem control input signal has changed state since the last time it was read by the system microprocessor.

### Scratch Pad Register

This register does not control the adapter in any way. It can be used by the system microprocessor to temporarily hold data.

# **Address and Interrupt Assignments**

The controller register I/O addresses and interrupt levels are:

| B '- 1 -           |      | _    |      | Serial |      |      |      |      |

|--------------------|------|------|------|--------|------|------|------|------|

| Register           | 1    | 2    | 3    | 4      | 5    | 6    | 7    | 8    |

| RBR (DLAB = 0)     | 03F8 | 02F8 | 3220 | 3228   | 4220 | 4228 | 5220 | 5228 |

| THR (DLAB = 0)     | 03F8 | 02F8 | 3220 | 3228   | 4220 | 4228 | 5220 | 5228 |

| IER (DLAB = 0)     | 03F9 | 02F9 | 3221 | 3229   | 4221 | 4229 | 5221 | 5229 |

| iiR                | 03FA | 02FA | 3222 | 322A   | 4222 | 422A | 5222 | 522  |

| LCR                | 03FB | 02FB | 3223 | 322B   | 4223 | 422B | 5223 | 5228 |

| MCR                | 03FC | 02FC | 3224 | 322C   | 4224 | 422C | 5224 | 5220 |

| LSR                | 03FD | 02FD | 3225 | 322D   | 4225 | 422D | 5225 | 5220 |

| MSR                | 03FE | 02FE | 3226 | 322E   | 4226 | 422E | 5226 | 522E |

| SCR                | 03FF | 02FF | 3227 | 322F   | 4227 | 422F | 5227 | 522F |

| DLL (DLAB = 1)     | 03F8 | 02F8 | 3220 | 3228   | 4220 | 4228 | 5220 | 5228 |

| DLM (DLAB = 1)     | 03F9 | 02F9 | 3221 | 3229   | 4221 | 4229 | 5221 | 5229 |

| Interrupt<br>Level | 4    | 3    | 3    | 3      | 3    | 3    | 3    | 3    |

Figure 20. I/O Address and Interrupt Level Assignments (Async)

Definitions of the abbreviations in Figure 20 are as follows:

DLAB: Divisor Latch Access Bit DLL: Divisor Latch (LSB) DLM: Divisor Latch (MSB) IER: Interrupt Enable Register

IIR: Interrupt Identification Register (Read Only)

LCR: Line Control Register

LSR: Line Status Register (Read Only)

MCR: Modem Control Register

MSR: Modem Status Register

RBR: Receiver Buffer Register (Read Only)

SCR: Scratch Pad Register

THR: Transmitter Holding Register (Write Only)

#### **Interrupt Assignments**

Two interrupt lines are provided to the system. Interrupt level 4 (IRQ4) is for serial mode 1 and interrupt level 3 (IRQ3) is for serial modes 2 through 8. To allow the adapter to send interrupts to the system, bit 3 of the Modem Control register must be set to 1. At this point, any interrupts allowed by the Interrupt Enable register will cause an interrupt.

#### **Hardware Interrupts**

Hardware interrupts are level-sensitive for systems using the Micro Channel architecture while systems using the Personal Computer type I/O channel design have edge-sensitive hardware interrupts. On edge-sensitive interrupt systems, the interrupt controller clears its internal interrupt-in-progress latch when the interrupt routine sends an End-of-Interrupt (EOI) command to the controller. The EOI is sent whether the incoming interrupt request to the controller is active or inactive.

In level-sensitive systems, the interrupt-in-progress latch is readable at an I/O address bit position. This latch is read during the interrupt service routine and may be reset by the read operation or may require an explicit reset.

Note: Designers may wish to limit the number of devices sharing an interrupt level for performance and latency considerations.

The interrupt controller on level-sensitive systems requires the interrupt request to be inactive at the time the EOI is sent; otherwise, a "new" interrupt request will be detected and another microprocessor interrupt caused.

To avoid this problem, a level-sensitive interrupt handler must clear the interrupt condition (usually by a Read or Write to an I/O port on the device causing the interrupt). After clearing the interrupt condition, a JMP \$+2 should be executed prior to sending the EOI to the interrupt controller. This ensures that the interrupt request is removed prior to re-enabling the interrupt controller. Another JMP \$+2 should be executed after sending the EOI, but prior to enabling the interrupt through the Set Interrupt Enable Flag (STI) command.

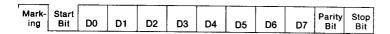

### **Serial Data Format**

The serial data format is as follows:

Figure 21. Serial Data Format

Data bit 0 is the first bit to be transmitted or received. The adapter automatically inserts the start bit, the correct parity bit, if programmed to do so, and the stop bits (1, 1-1/2, or 2 depending on the command in the Line Control register).

During the transmission of data, the marking condition will be used to denote the binary state 1, and the spacing condition is used to denote the binary state 0.

# **Binary Synchronous Communications**

The Binary Synchronous Communications (BSC) portion of the adapter uses:

- An Intel 8251A Universal Synchronous/Asynchronous Receiver/Transmitter communications controller

- An Intel 8255A-5 Programmable Peripheral Interface (PPI) for expanded modem operation

- An Intel 8254 Programmable Interval Timer for time-outs and generating interrupts.

# 8251A Description

The 8251A communications controller accepts data characters from the system in parallel format and converts them into a continuous serial data stream for transmission. While accepting data characters it can also receive external serial data streams and convert them into parallel data characters for the system microprocessor. When the controller can accept a new character for transmission or when it has received a character for the system microprocessor it signals the system. The system microprocessor can read the complete status of the controller at any time.

Once the controller is programmed, the 'transmitter ready' (TxRDY) signal is raised to an active level to signal the system microprocessor that the controller is ready to receive a data character from the system microprocessor. TxRDY is reset automatically when a character is written to the controller. The controller also receives serial data from the modem or I/O device. Upon receiving an entire character, the 'receiver ready' (RxRDY) signal is raised to an active level to an active level to signal the system microprocessor that the controller has a character ready. RxRDY is reset automatically by a data read operation. The controller cannot begin transmission until the transmitter enable bit is set in the Command instruction and it has received a 'clear-to-send' (CTS) modem control input signal. The 'transmit data' output signal is held in the marking state upon reset.

# Programming the 8251A

Prior to starting data transmission or reception, the 8251A communications controller must be loaded with a set of control words generated by the system microprocessor. These control words define the complete functional definition of the controller and must immediately follow an internal or external reset operation.

Control words are split into two formats:

- Mode Instructions

- Command Instructions.

#### Mode and Command Instructions

The Mode and Command instructions define the general operational characteristics of the controller. Once the Mode instruction has been written into the controller by the system microprocessor, sync characters (usually hex 32 in BSC) or Command instructions may be inserted.

The following represents a typical data block and shows the primary SDLC Mode instruction and Command instruction:

| Primary<br>Hex Address | Data Block<br>Information         |

|------------------------|-----------------------------------|

| nex Address            | information                       |

| 389                    | Mode Instruction                  |

| 3A9                    | Sync Character 1 (Sync Mode Only) |

| 3A9                    | Sync Character 2 (Sync Mode Only) |

| 3A9                    | Command Instruction               |

| 3A8                    | Data                              |

| 3A9                    | Command Instruction               |

| 3A8                    | Data                              |

| 3A9                    | Command Instruction               |

Figure 22. Typical Data Block

Note: The second Sync Character is skipped if the Mode instruction has programmed the controller to single-character internal sync mode. Both Sync Characters are skipped if the Mode instruction has programmed the controller to the asynchronous mode.

#### Mode Instruction

The controller can be used for either asynchronous or binary synchronous data communication. The format can be changed only after a master chip reset.

Note: When parity is enabled, it is not considered as one of the data bits for the purpose of programming the word length. The actual parity bit received on the 'receive data' line cannot be read on the data bus. In the case of a programmed character length of less than 8 bits, the least significant data bus bits hold the data; unused bits are "don't care bits" when writing data to the controller, and are 0's when reading the data from the controller.

### **Asynchronous Mode**

#### **Transmit**

When a data character is sent by the system microprocessor, the controller automatically adds a start bit (low level) followed by the data bits (least-significant bit first), and the programmed number of stop bits to each character. Also, an even or odd parity bit is inserted prior to the stop bits, as defined by the Mode instruction. The character is then transmitted as a serial data stream on the 'transmit data' line. The serial data is shifted out on the falling edge of the 'transmit character' (TxC) signal at a rate equal to 1/16 of TxC as defined by the Mode instruction. Break characters can be continuously sent to 'transmit data' if commanded to do so.

When no data characters have been loaded into the controller, the 'transmit data' output signal remains high (marking) unless a Break (continuously low) has been programmed.

#### Receive

The 'receive data' line is normally high. A falling edge on this line triggers the beginning of a start bit. The validity of this start bit is checked by strobing this bit a second time at its nominal center (16X or 64X mode only). If a low is detected again, it is a valid start bit, and the bit counter starts counting. The bit counter locates the center of the data bits, the parity bit and the stop bits. If a parity error occurs, the parity error flag is set.

Data and parity bits are sampled on the 'receive data' line with the rising edge of the 'receive character' (RxC) signal. If a low level is detected as the stop bit, the framing error flag is set. The stop bit signals the end of a character. The receiver requires only one stop bit, regardless of the number of stop bits programmed. This character is then loaded into the parallel I/O buffer of the controller. RxRDY is set high to signal the system that a character is ready. If a previous character has not been received by the system microprocessor, the present character replaces it in the I/O buffer, and the overrun error flag is raised and the previous character is then lost. All of the error flags can be reset by an Error Reset instruction. The occurrence of any of these errors does not affect the operation of the controller.

The Asynchronous Mode Instruction Format is shown in the following figure:

| Bit   | Name   | Function                     |

|-------|--------|------------------------------|

| 7 - 6 | S2, S1 | Stop Bits                    |

| 5     | EP     | Even Parity Generation/Check |

| 4     | PEN    | Parity enable                |

| 3 - 2 | L2, L1 | Character Rate Factor        |

| 1 - 0 | B2, B1 | Baud Rate Factor             |

Figure 23. Asynchronous Mode Instruction Format

Bits 7 - 6 Bits 7 (S2) and 6 (S1) select the number of stop bits used for transmit as shown in the following figure:

|    | Invalid | 1 Bit | 1.5 Bits | 2 Bits |

|----|---------|-------|----------|--------|

| S1 | 0       | 1     | 0        | 1      |

| S2 | 0       | 0     | ĺ        | i      |

Figure 24. Number of Stop Bits

Bit 5 When this bit is set to 1, even parity is generated or checked. When this bit is cleared to 0, odd parity is generated or checked.

When this bit is set to 1, parity is enabled. When this bit is cleared to 0, parity is disabled.

Bits 3 - 2 Bits 3 (L2) and 2 (L1) select the character rate factor as shown in the following figure:

|    | 5 Bits | 6 Bits | 7 Bits | 8 Bits |  |

|----|--------|--------|--------|--------|--|

| L1 | 0      | 1      | 0      | 1      |  |

| L2 | 0      | 0      | 1      | 1      |  |

Figure 25. Character Rate Factor

Bits 1 - 0 Bits 1 (B2) and 0 (B1) select the Baud Rate Factor as shown in the following figure:

|    | External Clock | (1 <b>X</b> ) | (16X) | (64X) |

|----|----------------|---------------|-------|-------|

| B1 | 0              | 1             | 0     | 1     |

| B2 | 0              | 0             | 1     | i     |

Figure 26. Baud Rate Factor

### **Synchronous Mode**

#### **Transmit**

The 'transmit data' output signal is normally high until the system sends its first character to the 8251A controller. When CTS goes low, the first character is serially transmitted. All characters are shifted out on the falling edge of the 'transmit clock' signal. Data is shifted out at the transmit clock rate.

Once transmission has started, the data stream at the 'transmit data' output signal must continue at the transmit clock rate. If the system does not provide the controller with a data character before the controller transmitter buffers become empty, the sync characters are automatically inserted in the 'transmit data' data stream. In this case, the transmitter empty bit in the Status Read Format is set to 1 to signal that the controller is empty and sync characters are being sent out. The transmitter empty bit is not cleared to 0 when the sync is being shifted out. The transmitter empty bit is internally reset by a data character being written into the controller.

#### Receive

In this mode, character synchronization is achieved internally. If the sync mode has been programmed, the Enter Hunt command should be included in the first Command instruction word written. Data on the 'receive data' line is sampled on the rising edge of the 'receive character' (RxC) signal. The content of the receiver buffer is compared at every bit boundary with the first sync character until a match occurs. If the controller has been programmed for two sync characters, the next character received is also compared; when both sync characters have been detected, the controller ends the Hunt mode and is in Character Synchronization mode. The synchronization detect (SYNDET) bit in the Status Read Format is then set to 1, and is reset automatically by a Status Read. If parity is programmed, the synchronization detect bit is not set until the middle of the parity bit instead of the middle of the last data bit. An Enter Hunt command has no effect in the asynchronous mode of operation.

Parity errors and overrun errors are both checked the same way as in the asynchronous receive mode. Parity is checked when not in the Hunt mode.

The system microprocessor can command the receiver to enter the Hunt mode if synchronization is lost. This also sets all used character bits in the buffer to 1, preventing a possible false synchronization detect caused by data that happens to be in the receiver buffer at Enter Hunt time. When in the Sync mode, but not in Hunt, sync detection is still functional, but only occurs at the known word boundaries. If one status read indicates sync detect and a second status read also indicates sync detect, then the programmed sync detect characters have been received since the previous status read. (If double character sync has been programmed, then both

sync characters have been contiguously received to gate a synchronization detect indication.)

The BSC Mode Instruction Format is shown in the following figure:

| Bit   | Name   | Function                     | - |

|-------|--------|------------------------------|---|

| 7     | scs    | Single Character Sync        |   |

| 6     | ESD    | External Sync Detect         |   |

| 5     | EP     | Even Parity Generation/Check |   |

| 4     | PEN    | Parity Enable                |   |

| 3 - 2 | L2, L1 | Character Length             |   |

| 1 - 0 |        | Reserved = 0                 |   |

Figure 27. BSC Mode Instruction Format

- When it is set to 1, this bit selects a single sync character. When it is cleared to 0, this bit selects a double sync character.

- Bit 6 When it is set to 1, this bit sets the 'syndet' signal on the 8251 as an output. When it is cleared to 0, this bit sets the 'syndet' signal as an input. This bit is normally cleared to 0.

- When this bit is set to 1, even parity is generated or checked. When this bit is cleared to 0, odd parity is generated or checked.

- When this bit is set to 1, parity is enabled. When this bit is cleared to 0, parity is disabled.

- Bits 3 2 Bits 3 (L2) and 2 (L1) select the character length as shown in the following figure:

|    | Character | Length |        |        |  |

|----|-----------|--------|--------|--------|--|

|    | 5 Bits    | 6 Bits | 7 Bits | 8 Bits |  |

| L1 | 0         | 1      | 0      | 1      |  |

| L2 | 0         | 0      | 1      | 1      |  |

Figure 28. Character Length

Bits 1 - 0 Reserved. These bits are always cleared to 0.

#### **Command Instructions**

Once the functional definition of the controller has been programmed by the Mode instruction and the sync characters are loaded (if in sync mode), the device is ready to be used for data communication. The Command instruction controls the actual operation of the selected format. Functions such as Enable Transmit/Receive, Error Reset and Modem Controls are provided by the Command instruction.

Once the Mode instruction has been written into the controller and if necessary, sync characters inserted, then all further "control writes" (3A9 primary, 389 alternate) will load a Command instruction. A reset operation (internal or external) returns the controller to the Mode Instruction Format.

The Command Instruction Format is shown in the following figure:

| EH    | Enter Hunt Mode*                      |

|-------|---------------------------------------|

| IR    | Internal Reset                        |

| RTS   | Request-To-Send                       |

| ER    | Error Reset                           |

| SBRK  | Send-Break-Character                  |

| RxE   | Receiver Enable                       |

| DTR · | Data-Terminal-Ready                   |

| TxEN  | Transmitter Enable                    |

|       | IR<br>RTS<br>ER<br>SBRK<br>RXE<br>DTR |

Figure 29. Command Instruction Format

| Bit / | When this bit is set to 1, the adapter enters the Hunt Mode.                                                                                      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 6 | When this bit is set to 1, the adapter returns to the Mode Instruction Format.                                                                    |

| Bit 5 | When this bit is set to 1, RTS output is forced low.                                                                                              |

| Bit 4 | When this bit is set to 1, the adapter resets all error flags.                                                                                    |

| Bit 3 | When it is set to 1, this bit forces the 'transmit data' signal inactive. When this bit is cleared to 0, the adapter is set for normal operation. |

When it is set to 1, this bit enables 'receiver ready'

(RxRDY). When it is cleared to 0, this bit disables RxRDY.

Bit 1

When this bit is set to 1, DTR output is forced low.

When this bit is set to 1, transmit is enabled. When this bit is cleared to 0, transmit is disabled. This bit has no effect in the asynchronous mode.