# PC SYSTEMS PRODUCTS

## TI486DX2-G66, TI486DX2-G80 MICROPROCESSORS

SRZS006A — MAY 1995 — REVISED JANUARY 1996

- 486DX Architecture and Performance

—486-Compatible Instruction Set and Register Set

- —Integrated Floating-Point Unit (FPU)

- —Integrated 16-Bit Hardware Multiplier

- -On-Chip 8K-Byte, 32-Bit Instruction/Data Cache Can be Configured to Operate in Write-Through or Write-Back Mode

- -Clock-Doubled Operation at 3.45-V With 5-V-Tolerant I/Os

- -Highly Optimized, Variable-Length Pipeline

- High-Performance, Footprint-Compatible

Upgrade for 486-Class Platforms

- —Internal CPU Clock Speeds of 66/80 MHz

- —Industry-Standard Footprints Using 168-Pin Ceramic PGA and 208-Pin Ceramic QFP

- Advanced Power-Management Features for Battery-Powered Notebook and Energy-Efficient Desktop PC Systems

- -System-Management Mode (SMM)

- -High-Priority System-Management Interrupt (SMI) With Separate Memory-Address Space

- -Suspend Mode (Initiated by Hardware or Software)

- -Fully Static Device Permits Clock-Stop State

- -3.45-V Device With 5-V-Tolerant I/Os Can Be Used in 3.45-V-Only or Mixed 3.45-V/5-V Systems

- Architecture Features 32-Bit Internal and 32-Bit External Buses.

- Texas Instruments (TI<sup>™</sup>) EPIC<sup>™</sup> Submicron CMOS Technology

#### description

The TI486DX2 microprocessors are attractive for new 486-compatible system designs because they are instruction-set and footprint compatible with 486-class platforms. Additionally, they feature an on-chip floating point unit that simplifies implementation of high-performance levels with clock-doubled CPU, on-chip 8K-byte cache, and advanced power-management techniques. Industry-standard footprint facilitates implementation of energy-efficient desktop and/or battery-powered notebook systems.

The TI486DX2 microprocessors support 8-, 16-, and 32-bit data types and operate in real, virtual-8086, and protected modes. The microprocessors achieve high performance through use of a highly optimized, variable-length pipeline combined with a RISC-like, single-cycle execution unit, an integrated floating point unit, a hardware multiplier, and an 8K-byte integrated instruction and data cache. The microprocessor can access up to 4G bytes of physical memory using a 32-bit bus and can perform burst bus cycles to improve the efficiency of multiple word transfers.

The TI486DX2 microprocessors are ideal for battery-powered applications because they typically draw 200  $\mu$ A when the input clock is stopped in the suspend mode. The devices operate from a 3.45-V power supply in 3.45-V-only systems or mixed 3.45-V/5-V systems.

| Торіс                                | Page | Торіс                            | Page |

|--------------------------------------|------|----------------------------------|------|

| Terminal Assignments                 | 5    | Mixed 3.45-V and 5-V Operation   | 21   |

| Terminal Functions                   | 11   | Electrical Specifications        | 22   |

| Execution Pipeline                   | 20   | Absolute Maximum Ratings         | 24   |

| On-Chip Write-Back Cache             | 20   | Recommended Operating Conditions | 24   |

| Floating-Point Unit (FPU) Operations | 21   | Electrical Characteristics       | 25   |

| Clock-Doubling                       | 21   | Switching Characteristics        | 26   |

| Power Management                     | 21   | Switching Waveforms              | 29   |

| System-Management Mode (SMM)         | 21   | Thermal Characteristics          | 32   |

| Suspend Mode and Static Operation    | 21   | Mechanical Specifications        | 34   |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC and TI are trademarks of Texas Instruments Incorporated.

Copyright © 1996, Texas Instruments Incorporated

#### description (continued)

The TI486DX2 microprocessors contain an on-chip 8K-byte cache memory that can be configured to operate in write-through or write-back mode. Conventional write-through mode updates external memory for each cache transaction. The write-back mode permits cache transactions to occur without updating external memory until a cache miss occurs, a modified line is replaced in the cache, or when an external bus master requires access to data. Configuring the cache to operate in write-back mode can improve overall performance by up to 15% when compared to write-through mode.

The TI486DX2 microprocessors are fabricated using Texas Instruments EPIC submicron CMOS technology. The combination of high-performance 486 operation, on-chip floating point unit, internal 8K-byte cache, 32-bit external data path, and advanced power-management features makes the TI486DX2 well suited for energy-efficient desktop and notebook applications.

| DEVICE PART NO. | SUPPLY               | SPEED | (MHz) | PACKAGE     |  |

|-----------------|----------------------|-------|-------|-------------|--|

| DEVICE PART NO. | VOLTAGE <sup>†</sup> | CORE  | BUS   | FACKAGE     |  |

| TX486DX2-G80-GA | 3.45 V               | 80    | 40    | 168-pin PGA |  |

| TX486DX2-G66-GA | 3.45 V               | 66    | 33    |             |  |

| TX486DX2-G80-WR | 3.45 V               | 80    | 40    | 208-pin     |  |

| TX486DX2-G66-WR | 3.45 V               | 66    | 33    | Ceramic QFP |  |

#### TI486DX2 PRODUCT OPTIONS

<sup>†</sup> All devices have 5-V-tolerant I/Os.

SRZS006A — MAY 1995 — REVISED JANUARY 1996

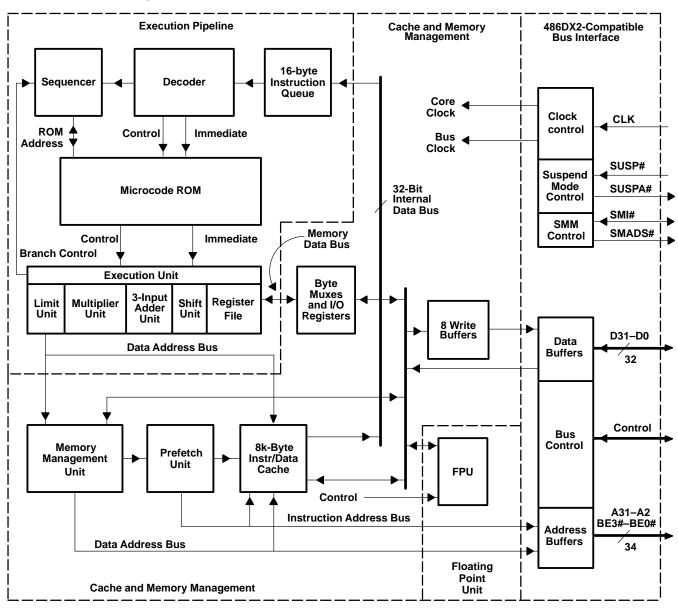

#### functional block diagram

SRZS006A — MAY 1995 — REVISED JANUARY 1996

PC SYSTEMS PRODUCTS

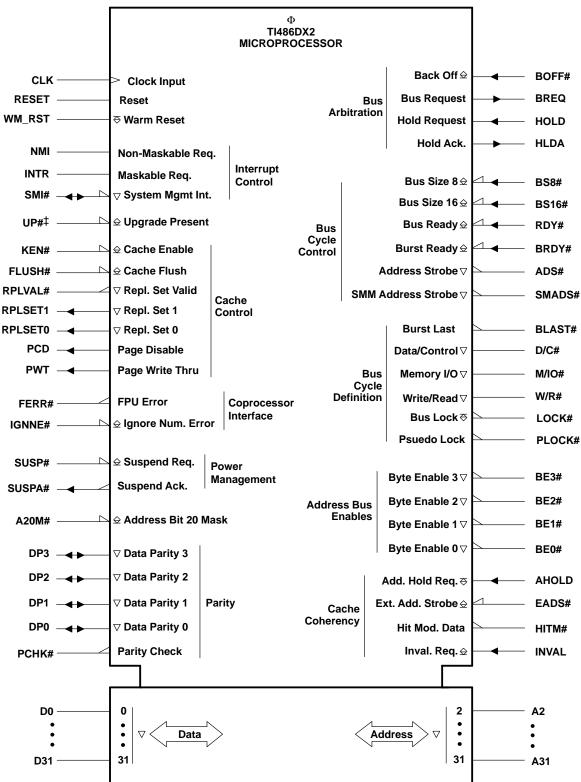

logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1991 and IEC Publication 617-12. <sup>‡</sup> 168-pin CPGA only

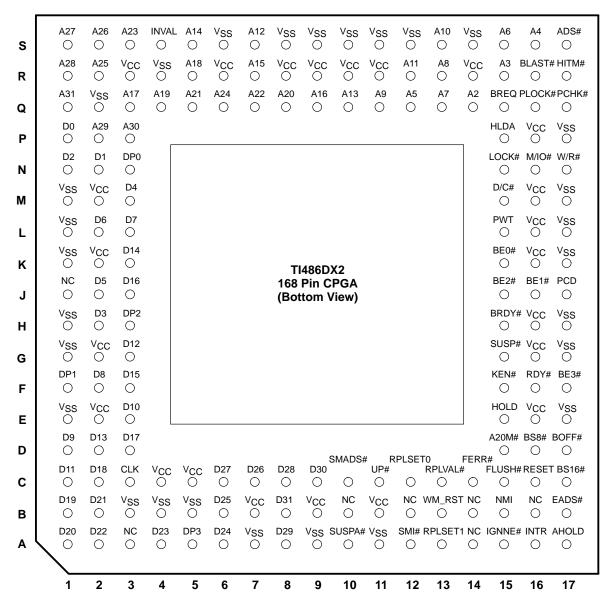

#### terminal assignments

The terminal assignments for the 168-pin, CPGA TI486DX2 microprocessors are shown as viewed from the terminal side (bottom) in Figure 1. The signal names are listed in Table 1 and Table 2 sorted by terminal number and signal name, respectively.

Figure 1. 168-Pin CPGA Terminal Assignments

NC — Make no external connection

NOTE A: Connecting or terminating (high or low) any NC terminal(s) may cause unpredictable results or nonperformance of the microprocessor.

SRZS006A — MAY 1995 — REVISED JANUARY 1996

Table 1. 168-Pin PGA Signal Names Sorted by Terminal Number

| Term.<br>No.                                                                                                                                                                                                                                                                                                                                    | Signal<br>Name | Term.<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Signal<br>Name | Term.<br>No.                                                                                                                                                                | Signal<br>Name | Term.<br>No.                                                                                                                                                                         | Signal<br>Name | Term.<br>No.                                                                                                                                                                     | Signal<br>Name | Term.<br>No.                                                                                                                                                                         | Signal<br>Name |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| No.           A1           A2           A3           A4           A5           A6           A7           A8           A9           A10           A11           A12           A13           A16           A17           B1           B2           B3           B4           B5           B6           B7           B8           B9           B10 |                | No.<br>B12<br>B13<br>B14<br>B15<br>B16<br>B17<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C7<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C1<br>C1<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C1<br>C1<br>C1<br>C1<br>C1<br>C1<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C10<br>C11<br>C12<br>C13<br>C11<br>C12<br>C13<br>C14<br>C15<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C15<br>C16<br>C17<br>C15<br>C16<br>C17<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C15<br>C16<br>C17<br>C15<br>C16<br>C17<br>D1<br>D1<br>D2<br>D3<br>D15<br>D15 |                | No.<br>D17<br>E1<br>E2<br>E3<br>E15<br>E16<br>E17<br>F1<br>F2<br>F3<br>F16<br>F17<br>G1<br>G2<br>G3<br>G15<br>G16<br>G17<br>H1<br>H2<br>H3<br>H15<br>H16<br>H17<br>J1<br>J2 |                | No.<br>J15<br>J16<br>J17<br>K1<br>K2<br>K3<br>K15<br>K16<br>K17<br>L1<br>L2<br>L3<br>L15<br>L16<br>L17<br>M1<br>M2<br>M3<br>M15<br>M16<br>M17<br>N1<br>N2<br>N3<br>N15<br>N16<br>N17 |                | No.<br>P2<br>P3<br>P15<br>P16<br>P17<br>Q1<br>Q2<br>Q3<br>Q4<br>Q5<br>Q6<br>Q7<br>Q8<br>Q9<br>Q10<br>Q11<br>Q12<br>Q13<br>Q14<br>Q15<br>Q16<br>Q17<br>R1<br>R2<br>R3<br>R4<br>R5 |                | No.<br>R7<br>R8<br>R9<br>R10<br>R11<br>R12<br>R13<br>R14<br>R15<br>R16<br>R17<br>S1<br>S2<br>S3<br>S4<br>S5<br>S6<br>S7<br>S8<br>S9<br>S10<br>S11<br>S12<br>S13<br>S14<br>S15<br>S16 |                |

| B11                                                                                                                                                                                                                                                                                                                                             | VCC            | D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BS8#           | J3                                                                                                                                                                          | D16            | P1                                                                                                                                                                                   | DO             | R6                                                                                                                                                                               | VCC            | S17                                                                                                                                                                                  | ADS#           |

SRZS006A — MAY 1995 — REVISED JANUARY 1996

| Table 2. 168-Pin PGA Terminal Numbers | Sorted by Signal Name |

|---------------------------------------|-----------------------|

|---------------------------------------|-----------------------|

| Signal<br>Name                                                                                                                                                                                                                                                                                                     | Term.<br>No.                                                                                                                                                         | Signal<br>Name                                                                                                                                                                                                                                                                                                                         | Term.<br>No.                                                                                                                                         | Signal<br>Name                                                                                                                                                                                                                                                                                                           | Term.<br>No.                                                                                                                            | Signal<br>Name                                                                                                                                                   | Term.<br>No.                                                                                                                                 | Signal<br>Name                                                                        | Term.<br>No.                                                                                                                                       | Signal<br>Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Term.<br>No.                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Name           A2           A3           A4           A5           A6           A7           A8           A9           A10           A11           A12           A13           A14           A15           A16           A17           A18           A19           A20           A20M#           A21           A22 | No.<br>Q14<br>R15<br>S16<br>Q12<br>S15<br>Q13<br>R13<br>Q11<br>S13<br>R12<br>S7<br>Q10<br>S5<br>R7<br>Q9<br>Q3<br>R5<br>Q4<br>Q3<br>R5<br>Q4<br>Q4<br>Q5<br>Q5<br>Q7 | Name           A29           A30           A31           ADS#           AHOLD           BE0#           BE1#           BE2#           BA3#           BLAST#           BOFF#           BRDY#           BREQ           BS8#           BS16#           CLK           D/C#           D0           D1           D2           D3           D4 | No.<br>P2<br>P3<br>Q1<br>S17<br>A17<br>K15<br>J16<br>J15<br>F17<br>R16<br>D17<br>H15<br>Q15<br>D16<br>C17<br>C3<br>M15<br>P1<br>N2<br>N1<br>H2<br>M3 | Name           D11           D12           D13           D14           D15           D16           D17           D18           D19           D20           D21           D22           D23           D24           D25           D26           D27           D28           D29           D30           D31           DP0 | No.<br>C1<br>G3<br>D2<br>K3<br>F3<br>J3<br>D3<br>C2<br>B1<br>A1<br>B2<br>A2<br>A4<br>A6<br>B6<br>C7<br>C6<br>C8<br>A8<br>C9<br>B8<br>N3 | Name<br>HITM#<br>HLDA<br>HOLD<br>IGNNE#<br>INTR<br>INVAL<br>KEN#<br>LOCK#<br>M/IO#<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC | No.<br>R17<br>P15<br>E15<br>A15<br>A16<br>S4<br>F15<br>N16<br>A3<br>A14<br>B10<br>B12<br>B14<br>B16<br>J1<br>B15<br>J17<br>Q16<br>L15<br>F16 | Name<br>SUSP#<br>SUSPA#<br>UP#<br>VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>VC | No.<br>G15<br>A10<br>C11<br>B7<br>B9<br>B11<br>C4<br>C5<br>E2<br>E16<br>G2<br>G16<br>H16<br>K2<br>K16<br>L16<br>K2<br>K16<br>L16<br>R3<br>R6<br>R8 | Name           VSS           VSS      VSS | No.<br>A11<br>B3<br>B4<br>B5<br>E1<br>E17<br>G1<br>G17<br>H1<br>H17<br>K1<br>K17<br>L1<br>L17<br>M1<br>M17<br>P17<br>Q2<br>R4<br>S6<br>S8<br>S9 |

| A23<br>A24<br>A25<br>A26<br>A27<br>A28                                                                                                                                                                                                                                                                             | S3<br>Q6<br>R2<br>S2<br>S1<br>R1                                                                                                                                     | D5<br>D6<br>D7<br>D8<br>D9<br>D10                                                                                                                                                                                                                                                                                                      | J2<br>L2<br>L3<br>F2<br>D1<br>E3                                                                                                                     | DP1<br>DP2<br>DP3<br>EADS#<br>FERR#<br>FLUSH#                                                                                                                                                                                                                                                                            | F1<br>H3<br>A5<br>B17<br>C14<br>C15                                                                                                     | RESET<br>RPLSET0<br>RPLSET1<br>RPLVAL#<br>SMADS#<br>SMI#                                                                                                         | C16<br>C12<br>A13<br>C13<br>C10<br>A12                                                                                                       | VCC<br>VCC<br>VCC<br>VCC<br>VCC<br>VSS<br>VSS                                         | R9<br>R10<br>R11<br>R14<br>A7<br>A9                                                                                                                | VSS<br>VSS<br>VSS<br>VSS<br>VSS<br>W/R#<br>WM_RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S10<br>S11<br>S12<br>S14<br>N17<br>B13                                                                                                          |

NC — Make no external connection

SRZS006A — MAY 1995 — REVISED JANUARY 1996

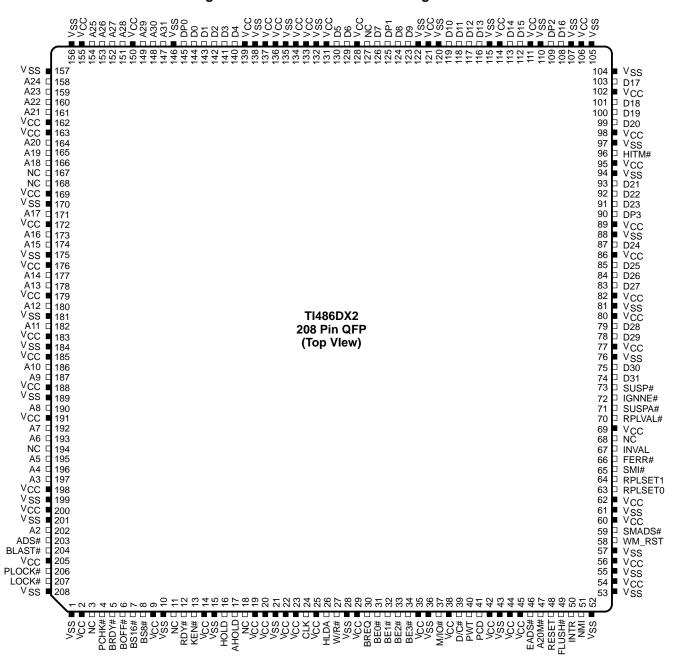

The terminal assignments for the 208-pin, QFP TI486DX2 microprocessors are shown as viewed from the top side in Figure 2. The signal names are listed in Table 3 and Table 4 sorted by terminal number and signal name, respectively.

Figure 2. 208-Pin QFP Terminal Assignments

NC — Make no external connection

NOTE A: Connecting or terminating (high or low) any NC terminal(s) may cause unpredictable results or nonperformance of the microprocessor.

SRZS006A — MAY 1995 — REVISED JANUARY 1996

| Term.    | Signal                             | Term.    | Signal                 | Term. | Signal                 | Term.      | Signal                    |

|----------|------------------------------------|----------|------------------------|-------|------------------------|------------|---------------------------|

| No.      | Name                               | No.      | Name                   | No.   | Name                   | No.        | Name                      |

| 1        | VSS                                | 53       | VSS                    | 105   | VSS                    | 157        | V <sub>SS</sub><br>A24    |

| 2        | VCC<br>NC                          | 54       | Vcc                    | 106   | VCC                    | 158        | A24                       |

| 3        | NC                                 | 55       | VSS                    | 107   | VSS                    | 159        | A23                       |

| 4        | PCHK#                              | 56       | Vcc                    | 108   | D16                    | 160        | A22                       |

| 5        | BRDY#                              | 57       | VSS<br>WM_RST          | 109   | DP2                    | 161        | A21                       |

| 6        | BOFF#                              | 58       | WM_RST                 | 110   | VSS                    | 162        | Vcc                       |

| 7        | BS16#                              | 59       | SMADS#                 | 111   | V <sub>CC</sub><br>D15 | 163        | VCC                       |

| 8        | BS8#                               | 60       | VCC                    | 112   | D15                    | 164        | A20                       |

| 9        | VCC                                | 61       | VSS                    | 113   | D14                    | 165        | A19                       |

| 10       | VSS                                | 62       | VCC                    | 114   | VCC                    | 166        | A18                       |

| 11       | NČ                                 | 63       | RPLSET0                | 115   | Vss                    | 167        | NC                        |

| 12       | RDY#                               | 64       | RPLSET1                | 116   | D13                    | 168        | NC                        |

| 13       | KEN#                               | 65       | SMI#                   | 117   | D12                    | 169        | Vcc                       |

| 14       | VCC                                | 66       | FERR#                  | 118   | D11                    | 170        | Vss                       |

| 15       | Vee                                | 67       | INVAL                  | 119   | D10                    | 171        | VSS<br>A17                |

| 16       | V <sub>SS</sub><br>HOLD            | 68       | NC                     | 120   | V <sub>SS</sub>        | 172        | Vcc                       |

| 17       | AHOLD                              | 69       | Vcc                    | 121   | VCC                    | 173        | A16                       |

| 18       | NC                                 | 70       | RPLVAL#                | 122   | VSS                    | 174        | A15                       |

| 19       | Vcc                                | 71       | SUSPA#                 | 123   | D9                     | 175        | VSS                       |

| 20       | VCC                                | 72       | IGNNE#                 | 124   | D8                     | 176        | VCC                       |

| 21       | Vss                                | 73       | SUSP#                  | 125   | DP1                    | 177        | A14                       |

| 22       | VCC                                | 70       | D31                    | 126   | D7                     | 178        | A13                       |

| 23       | Vcc                                | 75       | D30                    | 127   | NC                     | 179        | Vcc                       |

| 24       | VCC<br>CLK                         | 76       | V <sub>SS</sub>        | 128   | Vcc                    | 180        | A12                       |

| 25       | VCC                                | 77       | VCC                    | 129   | D6                     | 181        | V <sub>SS</sub>           |

| 26       | HLDA                               | 78       | D29                    | 130   | D5                     | 182        | A11                       |

| 27       | W/R#                               | 79       | D28                    | 131   | Vcc                    | 183        | Vcc                       |

| 28       | V <sub>SS</sub>                    | 80       | VCC                    | 132   | VSS                    | 184        | VSS                       |

| 29       | VCC                                | 81       | Vss                    | 133   | VCC                    | 185        | VCC                       |

| 30       | BREQ                               | 82       | VSS                    | 134   | VCC                    | 186        | A10                       |

| 31       | BE0#                               | 83       | V <sub>CC</sub><br>D27 | 135   | VSS                    | 187        | A9                        |

| 32       | BE1#                               | 84       | D26                    | 136   | VCC                    | 188        | Vcc                       |

| 33       | BE2#                               | 85       | D25                    | 137   | VCC                    | 189        | VCC<br>Voo                |

| 34       | BE3#                               | 86       | VCC                    | 138   | VSS                    | 190        | VSS<br>A8                 |

| 35       | V <sub>CC</sub>                    | 87       | D24                    | 139   | VCC                    | 191        | Vcc                       |

| 36       | Vee                                | 88       | V <sub>SS</sub>        | 140   | D4                     | 192        | A7                        |

| 37       | V <sub>SS</sub><br>M/IO#           | 89       | V55<br>V00             | 141   | D3                     | 193        | A6                        |

| 38       | V <sub>CC</sub>                    | 90       | V <sub>CC</sub><br>DP3 | 142   | D3<br>D2               | 193        | NC                        |

| 39       | D/C#                               | 91       | D23                    | 142   | D1                     | 195        | A5                        |

| 40       | PWT                                | 92       | D23<br>D22             | 143   | DO                     | 196        | A3<br>A4                  |

| 40       | PCD                                | 93       | D22<br>D21             | 145   | DP0                    | 190        | A4<br>A3                  |

| 41       |                                    | 94       | VSS                    | 145   |                        | 198        | Vcc                       |

| 42       | V <sub>CC</sub><br>V <sub>SS</sub> | 94<br>95 | v SS<br>Vee            | 140   | Vss<br>A31             | 198        | VCC<br>VSS                |

| 43       |                                    | 95<br>96 | VCC<br>HITM#           | 147   | A31<br>A30             | 200        | *55<br>Voc                |

| 44 45    | Vcc                                | 90<br>97 |                        | 140   | A30<br>A29             | 200        | Vcc                       |

| 45       | VCC<br>EADS#                       | 97<br>98 | Vss<br>Vcc             | 149   | VCC                    | 201        | V <sub>SS</sub><br>A2     |

| 40       | A20M#                              | 98<br>99 | D20                    | 150   | VCC<br>A28             | 202        | AZ<br>ADS#                |

| 47       | RESET                              | 100      | D20<br>D19             | 151   | A26<br>A27             | 203        | BLAST#                    |

| 40       | FLUSH#                             | 100      | D19<br>D18             | 152   | A27<br>A26             | 204<br>205 |                           |

| 49<br>50 | INTR                               | 101      |                        | 153   | A26<br>A25             | 205        | V <sub>CC</sub><br>PLOCK# |

| 50<br>51 | NMI                                | 102      | V <sub>CC</sub>        | 154   |                        | 206<br>207 | LOCK#                     |

| 52       |                                    | 103      | D17                    | 155   | VCC                    | 207<br>208 |                           |

| 52       | V <sub>SS</sub>                    | 104      | V <sub>SS</sub>        | 100   | V <sub>SS</sub>        | 200        | V <sub>SS</sub>           |

Table 3. 208-Pin QFP Signal Names Sorted by Terminal Number

NC — Make no external connection

SRZS006A — MAY 1995 — REVISED JANUARY 1996

| Table 4. 208-Pin QFP | Terminal Numbers | Sorted by Signal Name |

|----------------------|------------------|-----------------------|

|----------------------|------------------|-----------------------|

| Signal<br>Name | Term.<br>No. | Signal<br>Name | Term.<br>No. | Signal<br>Name                     | Term.<br>No. | Signal<br>Name                     | Term.<br>No. |

|----------------|--------------|----------------|--------------|------------------------------------|--------------|------------------------------------|--------------|

| A2             | 202          | D8             | 124          | PLOCK#                             | 206          | Vcc                                | 163          |

| A3             | 197          | D9             | 123          | PWT                                | 40           | Vcc                                | 169          |

| A4             | 196          | D10            | 119          | RDY#                               | 12           | Vcc                                | 172          |

| A5             | 195          | D11            | 118          | RESET                              | 48           | Vcc                                | 176          |

| A6             | 193          | D12            | 117          | RPLSET0                            | 63           | Vcc                                | 179          |

| A7             | 192          | D13<br>D14     | 116          | RPLSET1                            | 64<br>70     | Vcc                                | 183          |

| A8             | 190          |                | 113          | RPLVAL#<br>SMADS#                  | 70           | Vcc                                | 185          |

| A9<br>A10      | 187<br>186   | D15<br>D16     | 112<br>108   | SMADS#<br>SMI#                     | 59<br>65     | Vcc                                | 188<br>191   |

| A10<br>A11     | 182          | D16<br>D17     | 108          | SUSP#                              | 65<br>73     | Vcc                                | 191          |

| A11<br>A12     | 180          | D17<br>D18     | 103          | SUSPA#                             | 73           | Vcc                                | 200          |

| A12<br>A13     | 178          | D18<br>D19     | 101          |                                    | 2            | Vcc                                | 200<br>205   |

| A13<br>A14     | 178          | D19<br>D20     | 99           | Vcc                                | 2<br>9       | Vcc                                | 205          |

| A14<br>A15     | 174          | D20<br>D21     | 93           | Vcc                                | 9<br>14      | VSS                                | 10           |

| A15<br>A16     | 174          | D21<br>D22     | 92           | VCC                                | 19           | VSS                                | 10           |

| A10<br>A17     | 173          | D22<br>D23     | 92           | VCC                                | 20           | V <sub>SS</sub><br>V <sub>SS</sub> | 21           |

| A17<br>A18     | 166          | D23<br>D24     | 87           | V <sub>CC</sub><br>V <sub>CC</sub> | 20           | VSS                                | 28           |

| A10<br>A19     | 165          | D24<br>D25     | 85           | VCC                                | 22           | VSS                                | 36           |

| A19<br>A20     | 164          | D25<br>D26     | 84           | VCC<br>VCC                         | 25           | V <sub>SS</sub><br>V <sub>SS</sub> | 43           |

| A20<br>A20M#   | 47           | D20<br>D27     | 83           | VCC                                | 29           | VSS                                | 43<br>52     |

| A20101#        | 161          | D28            | 79           | VCC                                | 35           | VSS<br>VSS                         | 53           |

| A21<br>A22     | 160          | D28<br>D29     | 78           | VCC                                | 38           | VSS                                | 55<br>55     |

| A22<br>A23     | 159          | D29            | 75           | VCC<br>VCC                         | 42           | VSS<br>VSS                         | 55<br>57     |

| A24            | 158          | D31            | 74           | VCC                                | 44           | VSS<br>VSS                         | 61           |

| A25            | 154          | D/C#           | 39           | VCC                                | 45           | VSS<br>VSS                         | 76           |

| A26            | 153          | DP0            | 145          | VCC                                | 40<br>54     | VSS<br>VSS                         | 81           |

| A27            | 152          | DP1            | 125          | VCC                                | 56           | VSS                                | 88           |

| A28            | 151          | DP2            | 109          | VCC                                | 60           | V <sub>SS</sub>                    | 94           |

| A29            | 149          | DP3            | 90           | VCC                                | 62           | VSS                                | 97           |

| A30            | 148          | EADS#          | 46           | VCC                                | 69           | VSS                                | 104          |

| A31            | 147          | FERR#          | 66           | VCC                                | 77           | V <sub>SS</sub>                    | 105          |

| ADS#           | 203          | FLUSH#         | 49           | VCC                                | 80           | VSS                                | 107          |

| AHOLD          | 17           | HITM#          | 96           | VCC                                | 82           | VSS                                | 110          |

| BE0#           | 31           | HLDA           | 26           | VCC                                | 86           | VSS                                | 115          |

| BE1#           | 32           | HOLD           | 16           | VCC                                | 89           | VSS                                | 120          |

| BE2#           | 33           | IGNNE#         | 72           | VCC                                | 95           | VSS                                | 122          |

| BE3#           | 34           | INTR           | 50           | VCC                                | 98           | VSS                                | 132          |

| BLAST#         | 204          | INVAL          | 67           | Vcc                                | 102          | Vss                                | 135          |

| BOFF#          | 6            | KEN#           | 13           | VCC                                | 106          | VSS                                | 138          |

| BRDY#          | 5            | LOCK#          | 207          | VCC                                | 111          | VSS                                | 146          |

| BREQ           | 30           | M/IO#          | 37           | Vcc                                | 114          | Vss                                | 156          |

| BS16#          | 7            | NC             | 3            | VCC                                | 121          | VSS                                | 157          |

| BS8#           | 8            | NC             | 11           | VCC                                | 128          | VSS                                | 170          |

| CLK            | 24           | NC             | 18           | Vcc                                | 131          | VSS                                | 175          |

| D0             | 144          | NC             | 68           | VCC                                | 133          | VSS                                | 181          |

| D1             | 143          | NC             | 127          | Vcc                                | 134          | Vss                                | 184          |

| D2             | 142          | NC             | 167          | Vcc                                | 136          | Vss                                | 189          |

| D3             | 141          | NC             | 168          | Vcc                                | 137          | VSS                                | 199          |

| D4             | 140          | NC             | 194          | Vcc                                | 139          | VSS                                | 201          |

| D5             | 130          | NMI            | 51           | Vcc                                | 150          | VSS                                | 208          |

| D6             | 129          | PCD            | 41           | Vcc                                | 155          | WM_RST                             | 58           |

| D7             | 126          | PCHK#          | 4            | VCC                                | 162          | W/R#                               | 27           |

|                |              |                |              |                                    |              |                                    |              |

NC — Make no external connection

# PC SYSTEMS PRODUCTS

## TI486DX2-G66, TI486DX2-G80 MICROPROCESSORS

SRZS006A — MAY 1995 — REVISED JANUARY 1996

#### **Terminal Functions**

|       | TERMINAL     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | N<br>168-PIN | O.<br>208-PIN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A2    | Q14          | 202           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A3    | R15          | 197           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A4    | S16          | 196           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A5    | Q12          | 195           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A6    | S15          | 193           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A7    | Q13          | 192           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A8    | R13          | 190           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A9    | Q11          | 187           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A10   | S13          | 186           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A11   | R12          | 182           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A12   | S7           | 180           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A13   | Q10          | 178           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A14   | S5           | 177           | Address Bus (active high). The address bus (A31–A2) signals provide addresses for physical memory and                                                                                                                                                                                                                                                                                                                                                                   |

| A15   | R7           | 174           | I/O ports. Address lines A31-A4 are bidirectional signals used by the TI486DX2 to drive addresses to                                                                                                                                                                                                                                                                                                                                                                    |

| A16   | Q9           | 173           | memory and I/O devices and are also used by the system logic to drive cache inquiry addresses into the                                                                                                                                                                                                                                                                                                                                                                  |

| A17   | Q3           | 171           | processor. Address lines A3–A2 are output signals only and are ignored during cache inquiry cycles. All                                                                                                                                                                                                                                                                                                                                                                 |

| A18   | R5           | 166           | address lines can be used for addressing physical memory allowing a 4G-byte address space (0000 0000h                                                                                                                                                                                                                                                                                                                                                                   |

| A19   | Q4           | 165           | to FFFF FFFFh). During I/O port accesses, A31–A16 are driven low (except for coprocessor accesses). This                                                                                                                                                                                                                                                                                                                                                                |

| A20   | Q4<br>Q8     | 164           | permits a 64-Kbyte I/O address space (0000 0000h to 0000 FFFFh).                                                                                                                                                                                                                                                                                                                                                                                                        |

| A21   | Q5           | 161           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A22   | Q7           | 160           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A23   | S3           | 159           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A24   | Q6           | 158           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A25   | R2           | 154           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A26   | S2           | 153           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A27   | S1           | 152           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A28   | R1           | 151           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A29   | P2           | 149           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A30   | P3           | 148           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A31   | Q1           | 147           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADS#  | S17          | 203           | Address Strobe (active low). This 3-state output indicates that the TI486DX2 microprocessor has driven a valid address (A31–A2, BE3#–BE0#) and bus-cycle definition (M/IO#, D/C#, W/R#) on the appropriate output pins. If the current cycle is a memory access, ADS# also indicates that the current bus cycle is intended for normal memory space rather than system management memory. ADS# floats while the microprocessor is in a hold-acknowledge or float state. |

|       |              |               | An external pullup resistor is recommended to ensure negation during hold-acknowledge states.                                                                                                                                                                                                                                                                                                                                                                           |

| AHOLD |              |               | Address Hold Request (active high). This input forces the microprocessor to float A31–2 in the next clock cycle. While AHOLD is asserted, only the address bus is disabled. The current bus cycle remains active and completes in the normal fashion. No additional bus cycles are generated while AHOLD is asserted, except cache line write-back cycles in response to a cache inquiry.                                                                               |

|       | A17          | 17            | The microprocessor samples AHOLD during RESET. If AHOLD is asserted at the clock edge prior to the falling edge of RESET, built-in self test is executed prior to issuing any bus cycles.                                                                                                                                                                                                                                                                               |

|       |              |               | AHOLD is internally connected to a pulldown resistor to prevent it from floating active when left unconnected.                                                                                                                                                                                                                                                                                                                                                          |

|                              | TERMINAL                 |                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|--------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | 168-PIN                  | _                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A20M#                        | D15                      | 47                   | <ul> <li>Address Bit-20 Mask (active low). This input causes the microprocessor to mask (force low) physical address bit 20 when driving the external address bus or performing an internal cache access. Asserting A20M# emulates the 1M-byte address wraparound that occurs on the 8086. A20 masking should not be done by external logic. The A20M# input is ignored during three conditions:</li> <li>While paging is enabled</li> <li>While writing back dirty cache data to system memory. (This occurs only if the data was loaded into the cache when A20M# was inactive.)</li> <li>During system management address space accesses.</li> </ul>                                                                                                                                                                                                                                                 |

|                              |                          |                      | A20M# is internally connected to a pullup resistor to prevent it from floating active when left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BE3#<br>BE2#<br>BE1#<br>BE0# | F17<br>J15<br>J16<br>K15 | 34<br>33<br>32<br>31 | Byte Enables BE3#–BE0# (active low). These 3-state outputs determine which bytes within the 32-bit data bus are transferred during a memory or I/O access. During the first cycle of a cache line fill, the microprocessor expects data to be returned as if all data bytes are enabled regardless of the state of the byte enable outputs. BE3#–BE0# float during bus hold states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BLAST#                       | R16                      | 204                  | Burst Last (active low). This output indicates that the current 32-bit data transfer is either the last transfer of a multiple transfer cycle or a single transfer cycle. BLAST# is valid for the second and subsequent clock cycles within both burstable and nonburstable cycles. BLAST# floats during bus hold states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BOFF#                        | D17                      | 6                    | Back Off (active low). This input forces the microprocessor to abort the current bus cycle and relinquish control of the CPU local bus in the next clock. When asserted, the microprocessor enters the bus hold state but the HLDA output is not asserted. The bus hold state persists until BOFF# is negated. Once BOFF# is negated, the aborted bus cycle is restarted. While BOFF# is asserted, the microprocessor ignores any data returned.<br>BOFF# is internally connected to a pullup resistor to prevent it from floating active when left unconnected.                                                                                                                                                                                                                                                                                                                                        |

| BRDY#                        | H15                      | 5                    | Burst Ready (active low). This input is generated by the system hardware to indicate that the current transfer within a bus cycle can be terminated. The microprocessor samples BRDY# in the second and subsequent clocks of a multiple transfer cycle. If BRDY# is returned instead of RDY# for the first transfer of a multiple transfer cycle, the microprocessor completes the remaining transfers as a burst cycle. BRDY# must be returned instead of RDY# for each transfer except the final transfer to maintain the burst cycle. If RDY# is returned simultaneously with BRDY#, BRDY# is ignored and the burst cycle is aborted. BRDY# is active during address hold states. The microprocessor is capable of bursting code fetches, memory data reads, memory data writes (also with BS16# or BS8# active), or cache line write-back cycles if the BWRT bit in CCR2 is set. The microprocessor |

|                              |                          |                      | bursts cache write-back cycles resulting from a cache inquiry only when all four doublewords within the cache line have been modified and need to be written back. When less than three doublewords are modified, the microprocessor issues the write-back cycles as nonburst 32-bit write cycles.<br>BRDY# is internally connected to a pullup resistor to prevent it from floating active when left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BREQ                         | Q15                      | 30                   | Bus Request (active high). This output is asserted when a bus cycle is pending internally. BREQ is asserted in the first clock of a bus cycle as well as during bus hold and address hold states if a bus cycle is pending. If no other bus cycles are pending, BREQ is negated prior to termination of the current cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BS16#<br>BS8#                | C17<br>D16               | 7<br>8               | Bus Size 16 and Bus Size 8 (active low). These inputs allow connection of the 32-bit microprocessor data bus to an external bus of either 16 or 8 bits. When these inputs are asserted, the microprocessor performs multiple bus cycles to complete a single 32-bit transfer. BS16# and BS8# are sampled each clock. The state of these pins during the clock before RDY# goes low is used to determine the bus size for the current cycle. If both BS8# and BS16# are asserted, BS8# is used. During write cycles, valid data is driven only on the data pins corresponding to the active byte enables.                                                                                                                                                                                                                                                                                                |

|                              |                          |                      | BS16# and BS8# are each connected internally to a pullup resistor to prevent them from floating active when left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

SRZS006A — MAY 1995 — REVISED JANUARY 1996

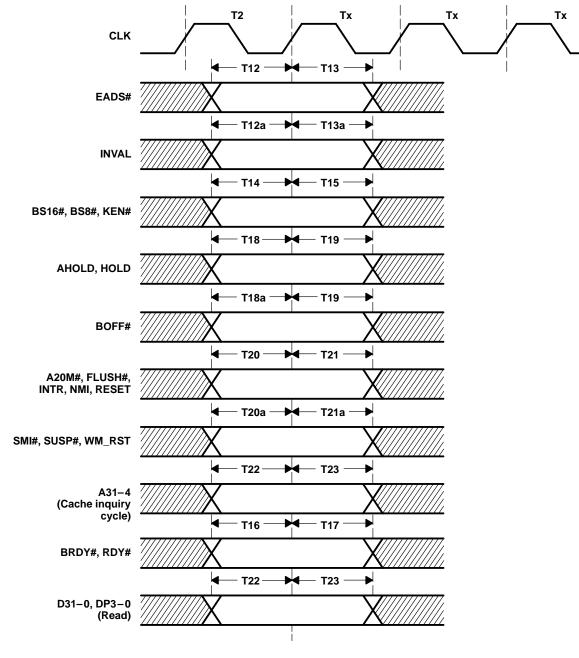

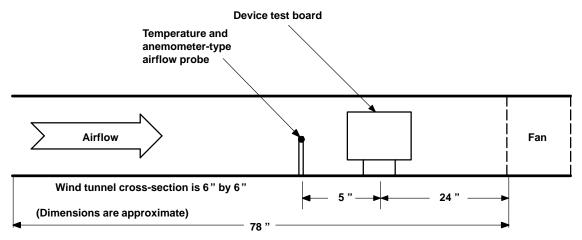

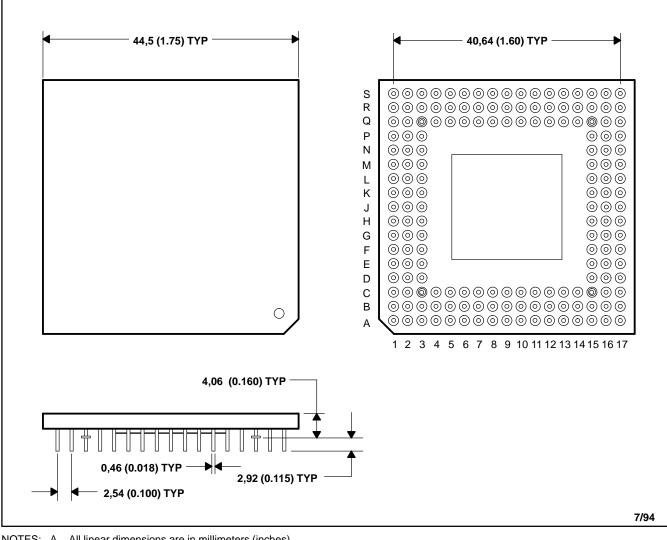

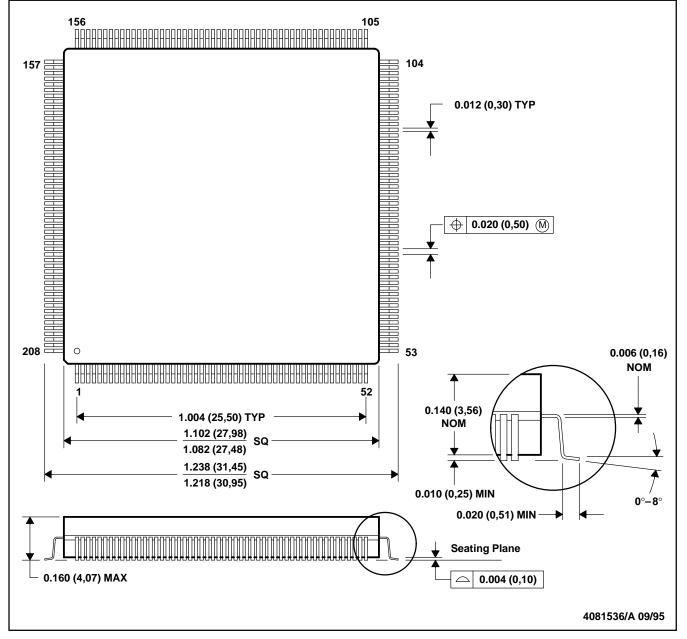

| TERMINAL                                                                                                                                                                                             |                                                                                                                                                                      |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |