# intel®

### Pentium<sup>®</sup> Processor Specification Update

Release Date: April, 1997

Order Number 242480-026

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium® processor may contain design defects or errors known as errata. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-7641

or call 1-800-879-4683 or visit Intel's website at http://www.intel.com

Copyright © Intel Corporation 1996, 1997.

\* Third-party brands and names are the property of their respective owners.

### CONTENTS

| REVISION HISTORY                                                                                                                | v       |

|---------------------------------------------------------------------------------------------------------------------------------|---------|

| PREFACE                                                                                                                         | x       |

| Part I: Specification Update for 75/90/100/120/133/150/166/200-MHz Pentium® Pro<br>and Pentium® Processors with MMX™ Technology | cessors |

| GENERAL INFORMATION                                                                                                             | 13      |

| SPECIFICATION CHANGES                                                                                                           | 39      |

| S-SPECS                                                                                                                         | 40      |

| ERRATA                                                                                                                          | 41      |

| SPECIFICATION CLARIFICATIONS                                                                                                    | 42      |

| DOCUMENTATION CHANGES                                                                                                           | 49      |

| Part II: Specification Update for Pentium® OverDrive® Processors                                                                |         |

| GENERAL INFORMATION                                                                                                             | 55      |

| SPECIFICATION CHANGES                                                                                                           | 63      |

| ERRATA                                                                                                                          | 65      |

| SPECIFICATION CLARIFICATIONS                                                                                                    | 70      |

| DOCUMENTATION CHANGES                                                                                                           | 73      |

| Appendix A: Pentium <sup>®</sup> Processor Related Technical Collateral                                                         |         |

### **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                                                        |

|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February, 1995   | -001    | This document consolidates information previously contained in various versions of stepping information, notably the B-, C- and D-stepping of Pentium <sup>®</sup> processor at iCOMP <sup>®</sup> index (510\60, 567\66) and the B- and C-stepping of Pentium processor at iCOMP index (610\75, 735\90, 815\100). |

| March, 1995      | -002    | Added Errata 22-25 and Spec Clarification 15 to Part I. Added Spec Change 12, Errata 24-27, 8DP-12DP, 11AP, Spec Clarification 3, and Doc Change 6 to Part II.                                                                                                                                                     |

| April, 1995      | -003    | Part II: Added new markings for 120 MHz; added Spec Changes 13, 14, 15, 16, 17, 2TCP, 3TCP; revised Spec Change 7, 11, 1TCP; added Errata 28 and 29; revised Errata 2TCP.                                                                                                                                          |

| May, 1995        | -004    | Part I: Added Errata 26 and 27; added Spec Clarification 17 and 18; added Doc Change 3.                                                                                                                                                                                                                            |

|                  |         | Part II: Revised Spec Change 12 and 17; added Spec Change 18;<br>revised Errata 25 and 4DP and added Errata 30-33; added Spec<br>Clarifications 9-13; added Doc Changes 7 and 8.                                                                                                                                   |

|                  |         | Part III: New Section — Pentium® OverDrive® Processor.                                                                                                                                                                                                                                                             |

| June, 1995       | -005    | Part I: Added Spec Change 5; added Erratum 28; added Spec Clarification 19.                                                                                                                                                                                                                                        |

|                  |         | Part II: Added Pentium Processor with Voltage Reduction<br>Technology; added 133 MHz; added spec changes 19-23; revised<br>Spec Changes 12-17; added S-Specs 1 and 2; added Errata 34, 35<br>and 13DP; revised Errata 4DP and 9AP; added Spec Clarification<br>14-17; revised Spec Clarification 8.                |

|                  |         | Part III: Added Spec Change 3; added Erratum 22; added Spec Clarification 8-10                                                                                                                                                                                                                                     |

| July, 1995       | -006    | Part I: Added Erratum 29.                                                                                                                                                                                                                                                                                          |

|                  |         | Part II: Added Spec Change 24; revised Spec Change 7 and 17; added Erratum 36; added Spec Clarification 18.                                                                                                                                                                                                        |

|                  |         | Part III: Added Spec Change 4; added Errata 23 and 24.                                                                                                                                                                                                                                                             |

| August, 1995    | -007 | Part I: Added Errata 30-32; added Spec Clarification 20 and 21.                                                                                                                                                                             |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |      | Part II: Revised Spec Change 21; added S-Spec 3; added Errata 37-41; revised Erratum 9; added Spec Clarification 19-26.                                                                                                                     |

|                 |      | Part III: Added Errata 25-29; added Spec Clarification 11, 12.                                                                                                                                                                              |

| September, 1995 | -008 | Removed Spec Changes, Spec Clarifications and Doc Changes which were incorporated into the 1995 <i>Pentium<sup>®</sup> Processor Family Developer's Manual</i> (Order Number 241563-004).                                                   |

|                 |      | Part I: Added Errata 33 and 34; added Doc Changes 1 and 2.                                                                                                                                                                                  |

|                 |      | Part II: Added Errata 42, 43 and 12AP; added Spec Clarification 13; added Doc Changes 1-6.                                                                                                                                                  |

|                 |      | Part III: Added Erratum 30; added Doc Changes 1 and 2.                                                                                                                                                                                      |

| October, 1995   | -009 | Part I: Added Spec Changes 1 and 2; added Errata 35-37; added Spec Clarification 4-7; added Doc Changes 3 and 4.                                                                                                                            |

|                 |      | Part II: Added Spec Changes 12 and 13; added Errata 44-48;<br>revised Erratum 11; added Spec Clarification 14-17; revised Spec<br>Clarification 1; added Doc Changes 7-9; revised Doc Change 3.                                             |

|                 |      | Part III: Added 83 MHz Pentium OverDrive processor; added Spec Changes 4-6; added Errata 31-33; revised erratum 7; added Spec Clarification 6 and 7; added Doc Changes 3 and 4.                                                             |

| November, 1995  | -010 | Part I: Added Errata 38-40; added Spec Clarifications 8-10; added Doc Change 5.                                                                                                                                                             |

|                 |      | Part II: Added 120 MHz Pentium processor with Voltage Reduction<br>Technology; added Spec Changes 14-15; added S-Spec 4; added<br>Errata 49-53, 13AP and 14AP; revised Erratum 10; added Spec<br>Clarifications 18-21; added Doc Change 10. |

|                 |      | Part III: Added Errata 34-36; revised Erratum 10; added Spec Clarification 8-9; added Doc Change 5.                                                                                                                                         |

| December, 1995 | -011 | Part I: Added Errata 41-44; revised errata 35 and 37; added Spec Clarifications 11-12; revised Spec Clarification 5 and 10; added Doc Change 6.                                                                                                                   |  |  |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                |      | Part II: Added Spec Change 16; added Errata 54-58; revised<br>Errata 44 and 46; added Spec Clarifications 22 and 23; revised<br>Spec Clarifications 5, 15 and 20; added Doc Change 11.                                                                            |  |  |

|                |      | Part III: Added Errata 37-40; revised Erratum 31; added Spec<br>Clarification 10-12; revised Spec Clarification 6; added Doc Change<br>6.                                                                                                                         |  |  |

| January, 1996  | -012 | Part I: Added Errata 45-46; revised Errata 37 and 43; added Spec Clarification 13; added Doc Changes 7 and 8.                                                                                                                                                     |  |  |

|                |      | Part II: Added Pentium Processor 150-MHz and 166-MHz, added<br>Spec Changes 17-20; added Errata 59-64, 14DP, 15AP and 16AP;<br>revised Errata 46, 56, 9AP and 11AP; added Spec Clarifications 24<br>and 25; revised Spec Clarification 9; added Doc Change 12-13. |  |  |

|                |      | Part III: Added Spec Change 7; added Errata 41-45; revised<br>Erratum 39; added Spec Clarification 13; added Doc Change 7 and<br>8.                                                                                                                               |  |  |

| February, 1996 | -013 | Part I: Added Erratum 47.                                                                                                                                                                                                                                         |  |  |

|                |      | Part II: Added S-Spec 5 and 6; added Errata 65 and 66.                                                                                                                                                                                                            |  |  |

|                |      | Part III: Added Erratum 46.                                                                                                                                                                                                                                       |  |  |

| March, 1996    | -014 | Part I: Revised Erratum 35; added Spec Clarification 14; added Doc Change 9.                                                                                                                                                                                      |  |  |

|                |      | Part II: Added S-Spec 7; revised Erratum 44; added Spec<br>Clarifications 26-29; added Doc Change 14.                                                                                                                                                             |  |  |

|                |      | Part III: Added 120/133-, 125-, 150- and 166-MHz OverDrive processors; added Spec Change 6; revised Erratum 31; added Errata 47-55; added Spec Clarification 14-16; added Doc Changes 9 and 10.                                                                   |  |  |

| April, 1996 | -016* | Part I: Added Erratum 48; revised Erratum 35; added Spec<br>Clarification 15-17; revised Spec Clarification 5; added Doc Change<br>10.                                                                 |  |  |

|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |       | Part II: Added Spec change 21; added S-Spec 8; revised S-Spec 4; added Errata 67-68; revised Errata 28 and 44; added Spec Clarifications 30-35; revised Spec Clarification 15; added Doc Change 15-16. |  |  |

|             |       | Part III: Added Errata 56-57; revised Errata 19 and 31; added Spec Clarifications 17-19; revised Spec Clarification 6; added Doc Changes 11 and 12.                                                    |  |  |

| May, 1996   | -017  | Part I: Added Spec Clarification 18.                                                                                                                                                                   |  |  |

|             |       | Part II: Revised Spec Changes 19 and 21; added Errata 15DP,<br>16DP and 18AP; revised Erratum 17AP; added Spec Clarification<br>36.                                                                    |  |  |

|             |       | Part III: Revised Spec Change 7; added Erratum 58; revised Erratum 57; added Spec Clarification 20.                                                                                                    |  |  |

| June, 1996  | -018  | Part I: Added Spec Change 3; added Erratum 49; added Spec Clarification 19.                                                                                                                            |  |  |

|             |       | Part II: Added Spec Change 22; revised Spec Change 20; added Errata 69; added Spec Clarifications 37 and 38; revised Spec Clarification 5 and 25.                                                      |  |  |

|             |       | Part III: Added Spec Change 8; added Erratum 59; added Spec Clarification 21 and 22.                                                                                                                   |  |  |

| July, 1996  | -019  | Part I: Added Erratum 50; revised Erratum 49; revised Spec<br>Clarification 10.                                                                                                                        |  |  |

|             |       | Part II: Added Spec Change 23; added Erratum 70; revised Erratum 69; revised Spec Clarification 20.                                                                                                    |  |  |

|             |       | Part III: Added Erratum 60; revised Erratum 59; revised Spec Clarification 10.                                                                                                                         |  |  |

Note:

\* Revision -015 was issued as revision -016.

| August, 1996    | -020 | Part I: Added Erratum 51; added Spec Clarification 20.                                                                                                                                                                                                                                                                                               |

|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |      | Part II: Added Erratum 71; added Spec Clarification 39.                                                                                                                                                                                                                                                                                              |

|                 |      | Part III: Added Erratum 61; added Spec Clarification 23.                                                                                                                                                                                                                                                                                             |

| September, 1996 | -021 | Part I: Added Spec Clarification 21; revised Spec Clarification 5.                                                                                                                                                                                                                                                                                   |

|                 |      | Part II: Added Spec Clarification 40; revised Spec Clarification 15.                                                                                                                                                                                                                                                                                 |

|                 |      | Part III: Added Spec Clarification 24; revised Spec Clarification 6.                                                                                                                                                                                                                                                                                 |

| October, 1996   | -022 | Part I: Revised Spec Change 3.                                                                                                                                                                                                                                                                                                                       |

|                 |      | Part II: Added Spec Change 24; revised Spec Change 22.                                                                                                                                                                                                                                                                                               |

|                 |      | Part III: Added Spec Change 9; revised Spec Change 8.                                                                                                                                                                                                                                                                                                |

| November, 1996  | -023 | Part I: Revised Spec Change 3.                                                                                                                                                                                                                                                                                                                       |

|                 |      | Part II: Added Spec Change 24; revised Spec Change 22.                                                                                                                                                                                                                                                                                               |

|                 |      | Part III: Added Spec Change 9; revised Spec Change 8.                                                                                                                                                                                                                                                                                                |

| January, 1996   | -024 | Part I: Added Spec Clarification 22, 23.                                                                                                                                                                                                                                                                                                             |

|                 |      | Part II: Changed Spec Changes 1, 2, 4-7 to S-Specs 9-14; added S-Specs 15-21; added Errata 72-78 and 19AP; revised Errata 14 and 69; added Spec Clarification 41-49; added Doc Change 17.                                                                                                                                                            |

|                 |      | Part III: Revised Erratum 11, 59; added Spec Clarifications 25, 26.                                                                                                                                                                                                                                                                                  |

| March, 1997     | -025 | Removed Spec Changes, S-Specs, Errata, Spec Clarifications and<br>Doc Changes which were incorporated in the 1997 edition of the<br>Pentium <sup>®</sup> Processor Family Developer's Manual (order number<br>241428) and the Intel Architecture Software Developer's Manual<br>Volume 1 (order number 243190) and Volume 2 (order number<br>243191) |

|                 |      | Part I: This section has been replaced with Part II from January's edition. The old section I has been removed and has been converted into the Pentium Processor 60 and 66 MHz Specification Update (order# 243326). Added erratum 79, added Doc Change 6.                                                                                           |

|                 |      | Part II: This section has been replaced with Part III from January's edition. Added erratum 62.                                                                                                                                                                                                                                                      |

| April, 1997     | -026 | Part I: Added Spec Change 3; added Doc Changes 7-8.                                                                                                                                                                                                                                                                                                  |

|                 |      | Part II: Added new Pentium <sup>®</sup> OverDrive <sup>®</sup> processor with MMX <sup>™</sup><br>Technology Stepping oxA3; added Spec Change 6 and 7; added<br>Errata 63-68; added Spec Clarification 14 and 15; added Doc<br>Change 5.                                                                                                             |

### PREFACE

This document is an update to the specifications contained in the *Pentium<sup>®</sup> Processor Family Developer's Manual*, (Order Number 241428) and Intel Architecture Software Developer's Manual, Volume 1 and 2 (order number 243190 and 243191). It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It contains Specification Changes, S-Specs, Errata, Specification Clarifications, and Documentation Changes, and is divided into the following two parts:

- Part I: Specification Update for 75/90/100/120/133/150/166/200-MHz Pentium<sup>®</sup> processors and Pentium processors with MMX<sup>™</sup> technology.

- Part II: Specification Update for Pentium® OverDrive® Processors.

#### Nomenclature

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the specifications.

S-Specs are exceptions to the published specifications, and apply only to the units assembled under that sspec.

**Errata** are design defects or errors. Errata may cause the Pentium processor's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

### Identification Information

The Pentium processor can be identified by the following register contents:

| Family <sup>1</sup> | 75/90/100/120/133/<br>150/166/200-MHz<br>Model 2 <sup>2</sup> | 63- and 83-MHz<br>Model 3 <sup>2</sup> | Pentium processors with<br>MMX™ Technology<br>Model 4 <sup>2</sup> |

|---------------------|---------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------|

| 05h                 | 02h (described in Part I)                                     | 03h (described in Part II)             | 04h (described in Part I)                                          |

NOTES:

1 The Family corresponds to bits [11:8] of the EDX register after RESET, bits [11:8] of the EAX register after the CPUID instruction is executed, and the generation field of the Device ID register accessible through Boundary Scan.

2 The Model corresponds to bits [7:4] of the EDX register after RESET, bits [7:4] of the EAX register after the CPUID instruction is executed, and the model field of the Device ID register accessible through Boundary Scan.

### Part I:

Specification Update for 75/90/100/120/133/150/166/200-MHz Pentium<sup>®</sup> Processors and Pentium<sup>®</sup> Processors with MMX<sup>™</sup> Technology

### **GENERAL INFORMATION**

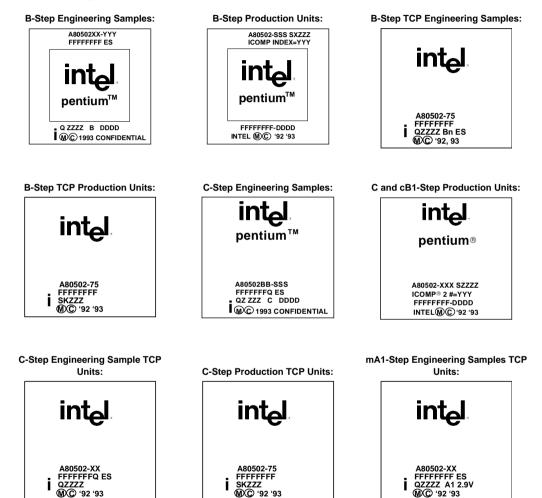

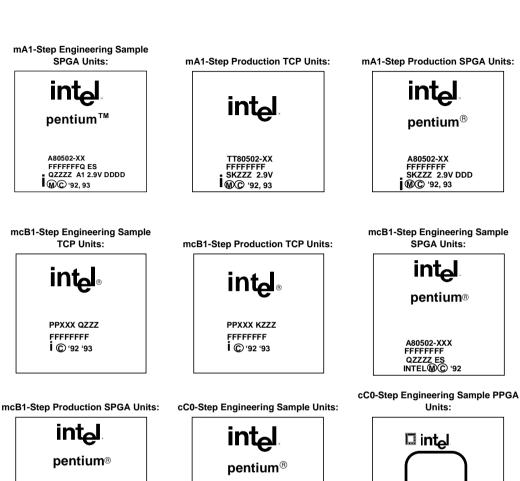

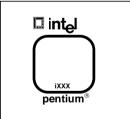

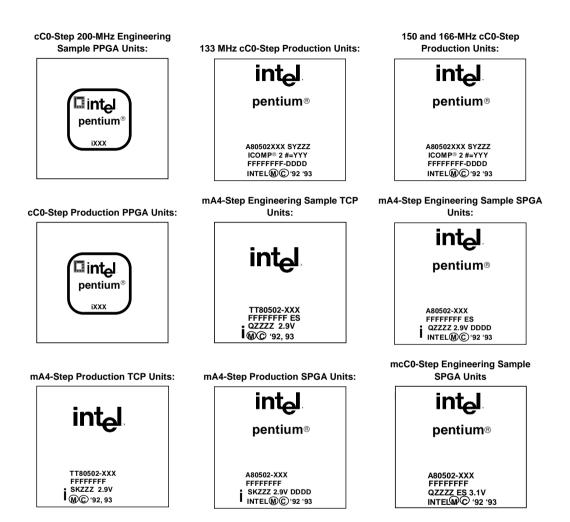

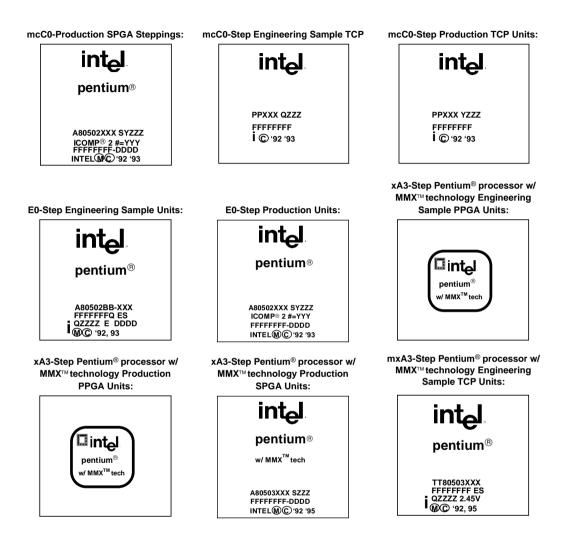

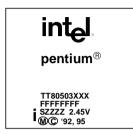

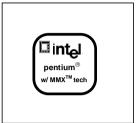

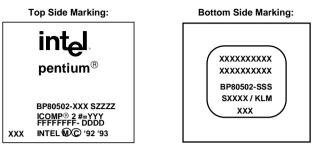

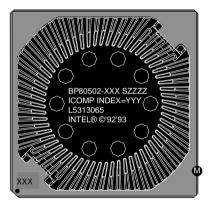

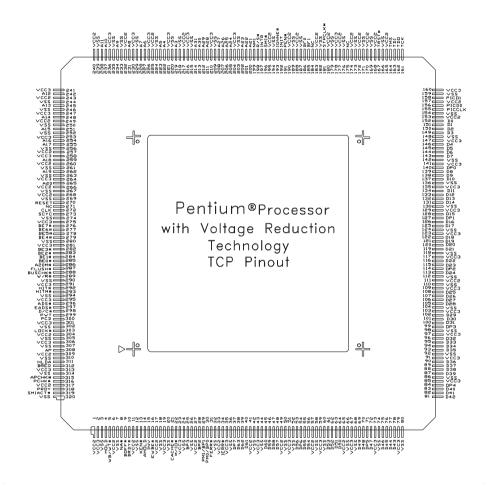

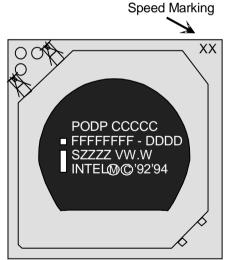

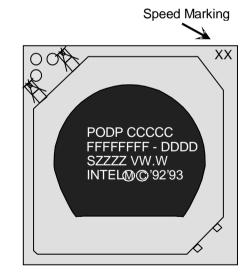

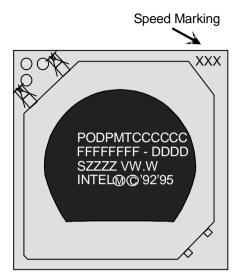

### Top Markings

A80502-XXX FFFFFFF SXZZZ 3.3V DDDD INTEL (M)(C) '92

A80502BB-XXX FFFFFFQ ES QZZZZ C DDDD MC '92, 93

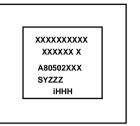

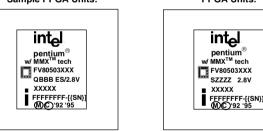

mxA3-Step Pentium<sup>®</sup> processor w/ MMX™ technology Production TCP Units:

mxA3-Step Pentium<sup>®</sup> processor w/ MMX<sup>™</sup> technology Engineering Sample PPGA Units:

mxA3-Step Pentium<sup>®</sup> processor w/ MMX™ technology Production PPGA Units:

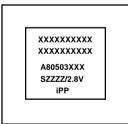

### **Bottom Markings**

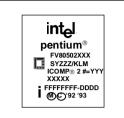

# in

### cC0-Step 200 MHz Engineering Sample PPGA Units:

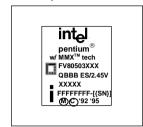

mcC0-Step Engineering Sample SPGA Units

mcC0-Step Production SPGA Units:

cC0-Step Production PPGA Units:

**E0-Step Engineering Sample Units**

MMX<sup>™</sup> Technology Production SPGA

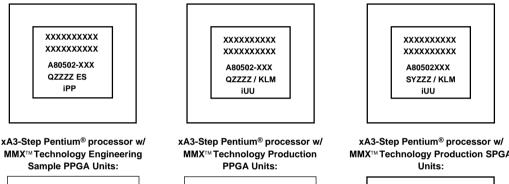

mxA3-Step Pentium<sup>®</sup> processor w/ MMX<sup>™</sup> Technology Engineering Sample PPGA Units:

mxA3-Step Pentium<sup>®</sup> processor w/ MMX™ Technology Production PPGA Units:

### Boxed Pentium<sup>®</sup> Processors with Attached Fan Heatsink

Fan Heatsink Base Marking:

#### NOTES:

- XX or XXX = Core Speed (MHz).

- BB = Bus speed (MHz)

- SXZZZ/SYZZZ/SZZZZ = Product S-Spec number

- FFFFFFF = FPO # (Test Lot Traceability #).

- For packages with heat spreaders, the inner line box defines the spreader edge.

- Ink Mark = All logo information on the heat spreader.

- Laser Mark = The two lines of information above and below the heat spreader. All bottomside information is laser mark.

- ES = Engineering Sample.

- QZZZZ = Sample Specification number.

- DDDD = Serialization code.

- YYY = : iCOMP<sup>®</sup> Index 2.0 OR iCOMP Index . Intel is making an enhancement to the current plastic PGA (PPGA) and ceramic PGA (CPGA) desktop and mobile Pentium processors with the addition of the iCOMP Index 2.0 rating as part of the processor package mark. For PPGA Pentium processors, the iCOMP Index 2.0 will be marked on the bottom side (pin side) of the package and for CPGA it will be marked on the top side of the package. The part marking will be: iCOMP 2 # = XXX (67 for 75-MHz, 81 for 90-MHz, 90 for 100-MHz, 100 for 120-MHz, 111 for 133-MHz, 114 for 150-MHz, 127 for 166-MHz, and 142 for 200-MHz). Older parts may be marked with the iCOMP Index (610 for 75-MHz and 735 for 90-MHz, 815 for 100-MHz, 1000 for 120-MHz, 1110 for 133-MHz, 1176 for 150-MHz and 1308 for 166-MHz parts).

#### PENTIUM® PROCESSOR SPECIFICATION UPDATE

- TT = TCP Package, A = SPGA Package

- The bottom markings on the C and cB1-step production units will replace the existing bottom marking on C-step parts effective 7/95.

- UU = 75 or 133 for 75- or 133-MHz Pentium processors, PP for all other speeds and MPP for mobile Pentium processors

- K = V for VRE voltage range and S for standard voltage range

- L = M for min valid MD timings and S for min valid standard timings

- M = U is not tested for DP, is tested for UP and MP and S is tested for DP, UP and MP

|        | C      | PUID  |          |                           |                           |                    |            |

|--------|--------|-------|----------|---------------------------|---------------------------|--------------------|------------|

| Туре   | Family | Model | Stepping | Manufacturing<br>Stepping | Speed (MHz)<br>Core / Bus | S-Spec             | Comments   |

| 0      | 5      | 2     | 1        | B1                        | 75/50                     | Q0540              | ES         |

| 2      | 5      | 2     | 1        | B1                        | 75/50                     | Q0541              | ES         |

| 0      | 5      | 2     | 1        | B1                        | 90/60                     | Q0542              | STD        |

| 0      | 5      | 2     | 1        | B1                        | 90/60                     | Q0613              | VR         |

| 2      | 5      | 2     | 1        | B1                        | 90/60                     | Q0543              | DP         |

| 0      | 5      | 2     | 1        | B1                        | 100/66                    | Q0563              | STD        |

| 0      | 5      | 2     | 1        | B1                        | 100/66                    | Q0587              | VR         |

| 0      | 5      | 2     | 1        | B1                        | 100/66                    | Q0614              | VR         |

| 0      | 5      | 2     | 1        | B1                        | 75/50                     | Q0601              | TCP Mobile |

| 0      | 5      | 2     | 1        | B1                        | 90/60                     | SX879              | STD        |

| 0      | 5      | 2     | 1        | B1                        | 90/60                     | SX885              | MD         |

| 0      | 5      | 2     | 1        | B1                        | 90/60                     | SX909              | VR         |

| 2      | 5      | 2     | 1        | B1                        | 90/60                     | SX874              | DP, STD    |

| 0      | 5      | 2     | 1        | B1                        | 100/66                    | SX886              | MD         |

| 0      | 5      | 2     | 1        | B1                        | 100/66                    | SX910              | VR, MD     |

| 0      | 5      | 2     | 2        | B3                        | 90/60                     | Q0628              | STD        |

| 0 or 2 | 5      | 2     | 2        | B3                        | 90/60                     | Q0611              | STD        |

| 0 or 2 | 5      | 2     | 2        | B3                        | 90/60                     | Q0612              | VR         |

| 0      | 5      | 2     | 2        | B3                        | 100/66                    | Q0677              | VRE/MD     |

| 0      | 5      | 2     | 2        | B3                        | 75/50                     | Q0606              | TCP Mobile |

| 0      | 5      | 2     | 2        | B3                        | 75/50                     | SX951              | TCP Mobile |

| 0      | 5      | 2     | 2        | B3                        | 90/60                     | SX923              | STD        |

| 0      | 5      | 2     | 2        | B3                        | 90/60                     | SX922              | VR         |

| 0      | 5      | 2     | 2        | B3                        | 90/60                     | SX921              | MD         |

| 2      | 5      | 2     | 2        | B3                        | 90/60                     | SX942              | DP, STD    |

| 2      | 5      | 2     | 2        | B3                        | 90/60                     | SX943              | DP, VR     |

| 2      | 5      | 2     | 2        | B3                        | 90/60                     | SX944              | DP, MD     |

| 0      | 5      | 2     | 2        | B3                        | 90/60                     | SZ951 <sup>5</sup> | STD        |

| 0      | 5      | 2     | 2        | B3                        | 100/66                    | SX960              | VRE/MD     |

#### Basic 75/90/100/120/133/150/166/200-MHzPentium<sup>®</sup> Processor and Pentium processor with MMX<sup>™</sup> Technology Identification Information

| CPUID  |        |       |          |                           |                           |                    |                     |

|--------|--------|-------|----------|---------------------------|---------------------------|--------------------|---------------------|

| Туре   | Family | Model | Stepping | Manufacturing<br>Stepping | Speed (MHz)<br>Core / Bus | S-Spec             | Comments            |

| 0 or 2 | 5      | 2     | 4        | B5                        | 75/50                     | Q0704              | TCP Mobile          |

| 0 or 2 | 5      | 2     | 4        | B5                        | 75/50                     | Q0666              | STD                 |

| 0 or 2 | 5      | 2     | 4        | B5                        | 90/60                     | Q0653              | STD                 |

| 0 or 2 | 5      | 2     | 4        | B5                        | 90/60                     | Q0654              | VR                  |

| 0 or 2 | 5      | 2     | 4        | B5                        | 90/60                     | Q0655              | MD                  |

| 0 or 2 | 5      | 2     | 4        | B5                        | 100/66                    | Q0656              | MD                  |

| 0 or 2 | 5      | 2     | 4        | B5                        | 100/66                    | Q0657              | VR, MD              |

| 0 or 2 | 5      | 2     | 4        | B5                        | 100/66                    | Q0658              | VRE/MD              |

| 0      | 5      | 2     | 4        | B5                        | 120/60                    | Q0707              | VRE/MD <sup>1</sup> |

| 0      | 5      | 2     | 4        | B5                        | 120/60                    | Q0708              | STD <sup>1</sup>    |

| 0      | 5      | 2     | 4        | B5                        | 75/50                     | SX975              | TCP Mobile          |

| 0 or 2 | 5      | 2     | 4        | B5                        | 75/50                     | SX961              | STD                 |

| 0 or 2 | 5      | 2     | 4        | B5                        | 75/50                     | SZ977 <sup>5</sup> | STD                 |

| 0 or 2 | 5      | 2     | 4        | B5                        | 90/60                     | SX957              | STD                 |

| 0 or 2 | 5      | 2     | 4        | B5                        | 90/60                     | SX958              | VR                  |

| 0 or 2 | 5      | 2     | 4        | B5                        | 90/60                     | SX959              | MD                  |

| 0 or 2 | 5      | 2     | 4        | B5                        | 90/60                     | SZ978 <sup>5</sup> | STD                 |

| 0 or 2 | 5      | 2     | 4        | B5                        | 100/66                    | SX962              | VRE/MD              |

| 0      | 5      | 2     | 5        | C2                        | 75/50                     | Q0725              | TCP Mobile          |

| 0 or 2 | 5      | 2     | 5        | C2                        | 75/50                     | Q0700              | STD                 |

| 0 or 2 | 5      | 2     | 5        | C2                        | 75/50                     | Q0749              | MD                  |

| 0 or 2 | 5      | 2     | 5        | C2                        | 90/60                     | Q0699              | STD                 |

| 0 or 2 | 5      | 2     | 5        | C2                        | 100/50 or 66              | Q0698              | VRE/MD              |

| 0 or 2 | 5      | 2     | 5        | C2                        | 100/50 or 66              | Q0697              | STD                 |

| 0      | 5      | 2     | 5        | C2                        | 120/60                    | Q0711              | VRE/MD              |

| 0      | 5      | 2     | 5        | C2                        | 120/60                    | Q0732              | VRE/MD              |

| 0      | 5      | 2     | 5        | C2                        | 133/66                    | Q0733              | MD                  |

| 0      | 5      | 2     | 5        | C2                        | 133/66                    | Q0751              | MD                  |

| 0      | 5      | 2     | 5        | C2                        | 133/66                    | Q0775              | VRE/MD              |

#### Basic 75/90/100/120/133/150/166/200-MHzPentium<sup>®</sup> Processor and Pentium processor with MMX<sup>™</sup> Technology Identification Information (Cont'd)

|        | C      | PUID  | , melegy rue |                           | . ,                       |                    |                             |

|--------|--------|-------|--------------|---------------------------|---------------------------|--------------------|-----------------------------|

| Туре   | Family | Model | Stepping     | Manufacturing<br>Stepping | Speed (MHz)<br>Core / Bus | S-Spec             | Comments                    |

| 0      | 5      | 2     | 5            | C2                        | 75/50                     | SK079              | TCP Mobile                  |

| 0 or 2 | 5      | 2     | 5            | C2                        | 75/50                     | SX969              | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 75/50                     | SX998              | MD                          |

| 0 or 2 | 5      | 2     | 5            | C2                        | 75/50                     | SZ994 <sup>5</sup> | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 75/50                     | SU070 <sup>6</sup> | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 90/60                     | SX968              | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 90/60                     | SZ995 <sup>5</sup> | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 90/60                     | SU031 <sup>6</sup> | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 100/50 or 66              | SX970              | VRE/MD                      |

| 0 or 2 | 5      | 2     | 5            | C2                        | 100/50 or 66              | SX963              | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 100/50 or 66              | SZ996 <sup>5</sup> | STD                         |

| 0 or 2 | 5      | 2     | 5            | C2                        | 100/50 or 66              | SU032 <sup>6</sup> | STD                         |

| 0      | 5      | 2     | 5            | C2                        | 120/60                    | SK086              | VRE/MD                      |

| 0      | 5      | 2     | 5            | C2                        | 120/60                    | SX994              | VRE/MD                      |

| 0      | 5      | 2     | 5            | C2                        | 120/60                    | SU033 <sup>6</sup> | VRE/MD                      |

| 0      | 5      | 2     | 5            | C2                        | 133/66                    | SK098              | MD                          |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 75/50                     | Q0686              | VRT <sup>2</sup> , TCP      |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 75/50                     | Q0689              | VRT <sup>2</sup> , SPGA     |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 90/60                     | Q0694              | VRT <sup>2</sup> , TCP      |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 90/60                     | Q0695              | VRT <sup>2</sup> , SPGA     |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 75/50                     | SK089              | VRT <sup>2</sup> , TCP      |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 75/50                     | SK091              | VRT <sup>2</sup> , SPGA     |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 90/60                     | SK090              | VRT <sup>2</sup> , TCP      |

| 0      | 5      | 2     | 5            | mA1 <sup>4</sup>          | 90/60                     | SK092              | VRT <sup>2</sup> , SPGA     |

| 0 or 2 | 5      | 2     | В            | cB1 <sup>4</sup>          | 120/60                    | Q0776              | STD/no Kit <sup>3</sup>     |

| 0 or 2 | 5      | 2     | В            | cB1 <sup>4</sup>          | 133/66                    | Q0772              | STD/no Kit <sup>3</sup>     |

| 0 or 2 | 5      | 2     | В            | cB1 <sup>4</sup>          | 133/66                    | Q0773              | STD                         |

| 0 or 2 | 5      | 2     | В            | cB1 <sup>4</sup>          | 133/66                    | Q0774              | VRE/MD, no Kit <sup>3</sup> |

| 0 or 2 | 5      | 2     | В            | cB1 <sup>4</sup>          | 120/60                    | SK110              | STD/no Kit <sup>3</sup>     |

| 0 or 2 | 5      | 2     | В            | cB1 <sup>4</sup>          | 133/66                    | SK106              | STD/no Kit <sup>3</sup>     |

#### Basic 75/90/100/120/133/150/166/200-MHz Pentium<sup>®</sup> Processor and Pentium processor with MMX™ Technology Identification Information (Cont'd)

|        | C      | PUID  | , interesty rate |                           |                           |                      |                          |

|--------|--------|-------|------------------|---------------------------|---------------------------|----------------------|--------------------------|

| Туре   | Family | Model | Stepping         | Manufacturing<br>Stepping | Speed (MHz)<br>Core / Bus | S-Spec               | Comments                 |

| 0 or 2 | 5      | 2     | В                | cB1 <sup>4</sup>          | 133/66                    | S106J <sup>7</sup>   | STD/no Kit <sup>3</sup>  |

| 0 or 2 | 5      | 2     | В                | cB1 <sup>4</sup>          | 133/66                    | SK107                | STD                      |

| 0 or 2 | 5      | 2     | В                | cB1 <sup>4</sup>          | 133/66                    | SU038 <sup>6</sup>   | STD/no Kit <sup>3</sup>  |

| 0      | 5      | 2     | В                | mcB1 <sup>4</sup>         | 100/66                    | Q0884                | VRT <sup>2</sup> , TCP   |

| 0      | 5      | 2     | В                | mcB1 <sup>4</sup>         | 120/60                    | Q0779                | VRT <sup>2</sup> , TCP   |

| 0      | 5      | 2     | В                | mcB1 <sup>4</sup>         | 120/60                    | Q0808                | 3.3V, SPGA               |

| 0      | 5      | 2     | В                | mcB1 <sup>4</sup>         | 100/66                    | SY029                | VRT <sup>2</sup> , TCP   |

| 0      | 5      | 2     | В                | mcB1 <sup>4</sup>         | 120/60                    | SK113                | VRT <sup>2</sup> , TCP   |

| 0      | 5      | 2     | В                | mcB1 <sup>4</sup>         | 120/60                    | SK118 <sup>7</sup>   | VRT <sup>2</sup> , TCP   |

| 0      | 5      | 2     | В                | mcB1 <sup>4</sup>         | 120/60                    | SX999                | 3.3V, SPGA               |

| 0 or 2 | 5      | 2     | С                | cC0                       | 133/66                    | Q0843                | STD/No Kit <sup>3</sup>  |

| 0 or 2 | 5      | 2     | С                | cC0                       | 133/66                    | Q0844                | STD                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 150/60                    | Q0835                | STD                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 150/60                    | Q0878                | STD, PPGA <sup>9</sup>   |

| 0 or 2 | 5      | 2     | С                | cC0                       | 166/66                    | Q0836                | VRE/No Kit <sup>3</sup>  |

| 0 or 2 | 5      | 2     | С                | cC0                       | 166/66                    | Q0841                | VRE                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 166/66                    | Q0886                | VRE, PPGA <sup>9</sup>   |

| 0 or 2 | 5      | 2     | С                | cC0                       | 166/66                    | Q0890                | VRE, PPGA <sup>9</sup>   |

| 0      | 5      | 2     | С                | cC0                       | 166/66                    | Q0949 <sup>8</sup>   | VRE, PPGA <sup>9</sup>   |

| 0 or 2 | 5      | 2     | С                | cC0                       | 200/66                    | Q0951F <sup>10</sup> | VRE, PPGA <sup>9</sup>   |

| 0      | 5      | 2     | С                | cC0                       | 200/66                    | Q0951 <sup>8</sup>   | VRE, PPGA <sup>9</sup>   |

| 0 or 2 | 5      | 2     | С                | cC0                       | 120/60                    | SY062                | STD                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 133/66                    | SY022                | STD/ No Kit <sup>3</sup> |

| 0 or 2 | 5      | 2     | С                | cC0                       | 133/66                    | SY023                | STD                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 133/66                    | SU073 <sup>6</sup>   | STD/ No Kit <sup>3</sup> |

| 0 or 2 | 5      | 2     | С                | cC0                       | 150/60                    | SY015                | STD                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 150/60                    | SU071 <sup>6</sup>   | STD                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 166/66                    | SY016                | VRE/ No Kit <sup>3</sup> |

| 0 or 2 | 5      | 2     | С                | cC0                       | 166/66                    | SY017                | VRE                      |

| 0 or 2 | 5      | 2     | С                | cC0                       | 166/66                    | SU072 <sup>6</sup>   | VRE/ No Kit <sup>3</sup> |

| 0      | 5      | 2     | С                | cC0                       | 166/66                    | SY037 <sup>8</sup>   | VRE, PPGA <sup>9</sup>   |

#### Basic 75/90/100/120/133/150/166/200-MHzPentium<sup>®</sup> Processor and Pentium processor with MMX<sup>™</sup> Technology Identification Information (Cont'd)

|        | C      | PUID  |          |                           | . ,                       |                    |                         |

|--------|--------|-------|----------|---------------------------|---------------------------|--------------------|-------------------------|

| Туре   | Family | Model | Stepping | Manufacturing<br>Stepping | Speed (MHz)<br>Core / Bus | S-Spec             | Comments                |

| 0 or 2 | 5      | 2     | С        | cC0                       | 200/66                    | SY044              | VRE, PPGA <sup>9</sup>  |

| 0      | 5      | 2     | С        | cC0                       | 200/66                    | SY045 <sup>8</sup> | VRE, PPGA <sup>9</sup>  |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 75/50                     | Q0848              | VRT <sup>2</sup> , TCP  |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 75/50                     | Q0851              | VRT <sup>2</sup> , SPGA |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 90/60                     | Q0849              | VRT <sup>2</sup> , TCP  |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 90/60                     | Q0852              | VRT <sup>2</sup> , SPGA |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 100/66                    | Q0850              | VRT <sup>2</sup> , TCP  |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 100/66                    | Q0853              | VRT <sup>2</sup> , SPGA |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 75/50                     | SK119              | VRT <sup>2</sup> , TCP  |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 75/50                     | SK122              | VRT <sup>2</sup> , SPGA |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 90/60                     | SK120              | VRT <sup>2</sup> , TCP  |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 90/60                     | SK123              | VRT <sup>2</sup> , SPGA |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 100/66                    | SK121              | VRT <sup>2</sup> , TCP  |

| 0      | 5      | 7     | 0        | mA4 <sup>4</sup>          | 100/66                    | SK124              | VRT <sup>2</sup> , SPGA |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 100/66                    | Q0887              | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 120/60                    | Q0879              | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 120/60                    | Q0880              | SPGA 3.1V               |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 133/66                    | Q0881              | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 133/66                    | Q0882              | SPGA 3.1V               |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 150/60                    | Q024               | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 150/60                    | Q0906              | TCP 3.1V                |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 150/60                    | Q040               | SPGA/VRT <sup>2</sup>   |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 75/50                     | SY056              | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 100/66                    | SY020              | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 100/66                    | SY046              | SPGA 3.1V               |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 120/60                    | SY021              | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 120/60                    | SY027              | SPGA 3.1V               |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 120/60                    | SY030              | SPGA 3.3V               |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 133/66                    | SY019              | TCP/VRT <sup>2</sup>    |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 133/66                    | SY028              | SPGA 3.1V               |

| 0      | 5      | 2     | С        | mcC0 <sup>4</sup>         | 150/60                    | SY061              | TCP/VRT <sup>2</sup>    |

#### Basic 75/90/100/120/133/150/166/200-MHz Pentium<sup>®</sup> Processor and Pentium processor with MMX™ Technology Identification Information (Cont'd)

|        | C      | PUID  | , including , incl | itification informa       |                           |                    |                        |

|--------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|--------------------|------------------------|

| Туре   | Family | Model | Stepping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Manufacturing<br>Stepping | Speed (MHz)<br>Core / Bus | S-Spec             | Comments               |

| 0      | 5      | 2     | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mcC0 <sup>4</sup>         | 150/60                    | SY043              | TCP 3.1V               |

| 0      | 5      | 2     | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mcC0 <sup>4</sup>         | 150/60                    | SY058              | SPGA/VRT <sup>2</sup>  |

| 0      | 5      | 2     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E0                        | 75/50                     | Q0846              | TCP Mobile             |

| 0 or 2 | 5      | 2     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E0                        | 75/50                     | Q0837              | STD                    |

| 0 or 2 | 5      | 2     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E0                        | 90/60                     | Q0783              | STD                    |

| 0 or 2 | 5      | 2     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E0                        | 100/50 or 66              | Q0784              | STD                    |

| 0 or 2 | 5      | 2     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E0                        | 120/60                    | Q0785              | VRE                    |