# Pentium<sup>®</sup> Processor for Embedded Applications

**Specification Update**

December 1998

**Notice:** The Pentium  $^{\circledR}$  processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Order Number: 273183-002

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium® processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

| Revision History                                           | 5    |

|------------------------------------------------------------|------|

| Preface                                                    | 6    |

| Specification Changes                                      | . 19 |

| S-Specs                                                    | . 22 |

| Errata                                                     | . 26 |

| Specification Clarifications                               | . 61 |

| Documentation Changes                                      | . 69 |

| Appendix A Pentium® Processor Related Technical Collateral | . 72 |

# Revision History

## **Revision History**

| Revision Date | Version | Description                                                                                                                                                     |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12/11/98      | 002     | Added: Specification Change 20; Errata 83; and Specification Clarification 25. Updated the Processor Identification section to reflect new SL2TU S-spec number. |

| 6/11/98       | 001     | This is the first publication of this document.                                                                                                                 |

## **Preface**

This document is an update to the specifications contained in the *Pentium* Processor Family Developer's Manual, (Order Number 241428) and the *Intel Architecture Software Developer's Manual*, Volume 1, 2 and 3 (Order Numbers 243190, 243191, and 243192). It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It contains Specification Changes, S-Specs, Errata, Specification Clarifications and Documentation Changes for Pentium processors for high-performance embedded applications. The following processors are included in this Specification Update:

- 100 MHz Pentium® Processor

- 133 MHz Pentium® Processor

- 133 MHz Pentium® Processor with Voltage Reduction Technology

- 166 MHz Pentium® Processor

For information pertaining to processors not listed above, refer to the *Pentium*<sup>®</sup> *Processor Specification Update* (order number 242480).

## **Nomenclature**

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the specifications.

**S-Specs** are exceptions to the published specifications and apply only to the units assembled under that s-spec.

**Errata** are design defects or errors. Errata may cause the Pentium<sup>®</sup> processor's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

## **Identification Information**

The Pentium processor can be identified by the following register contents:

### **Processor Identification**

| Family <sup>(1)</sup> | 100/133/166 MHz Model 2 <sup>(2)</sup> |

|-----------------------|----------------------------------------|

| 05H                   | 02H                                    |

#### NOTES:

- The Family corresponds to bits [11:8] of the EDX register after RESET, bits [11:8] of the EAX register after the CPUID instruction is executed, and the generation field of the Device ID register accessible through Boundary Scan.

- The Model corresponds to bits [7:4] of the EDX register after RESET, bits [7:4] of the EAX register after the CPUID instruction is executed, and the model field of the Device ID register accessible through Boundary Scan.

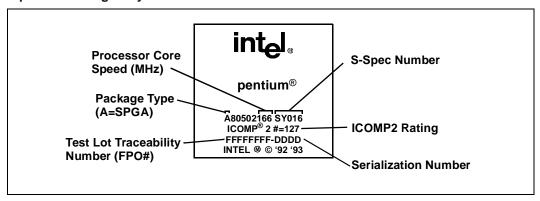

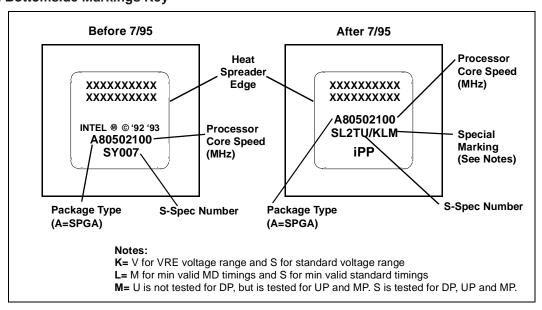

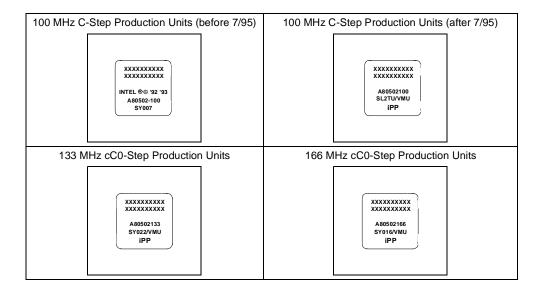

## **Marking Information**

Figure 1. Topside Markings Key

Figure 2. Bottomside Markings Key

## **Top Markings**

## **Bottom Markings**

## **Processor Identification**

- CPU Type of "2" or "0 or 2" indicates this part supports dual processing.

- The Type corresponds to bits [13:12] of the EDX register after RESET, bits [13:12] of the EAX register after the CPUID instruction is executed. This is shown as two different values based on the operation of the device as the primary processor or the dual processor upgrade.

- The Family corresponds to bits [11:8] of the EDX register after RESET, bits [11:8] of the EAX register after the CPUID instruction is executed.

- The Model corresponds to bits [7:4] of the EDX register after RESET, bits [7:4] of the EAX register after the CPUID instruction is executed.

- The Stepping corresponds to bits [3:0] of the EDX register after RESET, bits [3:0] of the EAX register after the CPUID instruction is executed.

- The absence of a package type in the comments column means the processor is SPGA by default.

I

| Table 1. Classic 100/133/166 MHz Pentium® Processor Identification Informati | Table 1. | Classic 100/133/166 | MHz Pentium <sup>®</sup> Processor | Identification Information |

|------------------------------------------------------------------------------|----------|---------------------|------------------------------------|----------------------------|

|------------------------------------------------------------------------------|----------|---------------------|------------------------------------|----------------------------|

|        | CI     | PUID  |          |                                |                           |        |                                        |

|--------|--------|-------|----------|--------------------------------|---------------------------|--------|----------------------------------------|

| Туре   | Family | Model | Stepping | Manufac-<br>turing<br>Stepping | Speed (MHz)<br>Core / Bus | S-Spec | Comments                               |

| 0 or 2 | 5      | 2     | С        | cC0                            | 133/66                    | SY022  | STD                                    |

| 0 or 2 | 5      | 2     | С        | cC0                            | 166/66                    | SY016  | VRE <sup>1</sup> , No Kit <sup>2</sup> |

| 0      | 5      | 2     | С        | mcC0 <sup>3</sup>              | 133/66                    | SY028  | SPGA 3.1V                              |

| 0 or 2 | 5      | 2     | С        | E0                             | 100/50 or 66              | SL2TU  | STD <sup>4</sup>                       |

#### NOTES:

- VRE: These parts have a reduced and shifted voltage specification, and reductions in the minimum output valid delays on the pins listed in the specifications in S-Spec 10. The VRE voltage range for the C2 and subsequent steppings of the Pentium processor is VCC = 3.40-3.60V. The VRE voltage range for Bstep parts remains at 3.45-3.60V.

- 2. No Kit means that part meets the specifications but is not tested to support 82498/82493 and 82497/82492 cache timings.

- 3. The mcC0-step uses Intel's VRT (Voltage Reduction Technology) to support mobile applications.

- 4. STD: The VCC specification for the C2 and subsequent steppings of the Pentium processor is VCC = 3.135V to 3.6V. The voltage range for B-step parts remains at 3.135V-3.465V (B-step devices are no longer offered). All E0-step production parts are standard voltage.

## **Summary Table of Changes**

The following table indicates the Specification Changes, S-Specs, Errata, Specification Clarifications or Documentation Changes, which apply to the listed 100/133/166 MHz Pentium processor steppings. Intel intends to fix some of the errata in a future stepping of the component, and to account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

## **Codes Used in Summary Table**

X: Erratum, Specification Change or Clarification that applies to this

stepping.

Doc: Document change or update that will be implemented.

Fix: This erratum is intended to be fixed in a future stepping of the

component.

Fixed: This erratum has been previously fixed.

NoFix: There are no plans to fix this erratum.

(No mark) or (Blank Box): This erratum is fixed in listed stepping or specification change does not

apply to listed stepping.

DP: Dual processing related errata.

AP: APIC related errata.

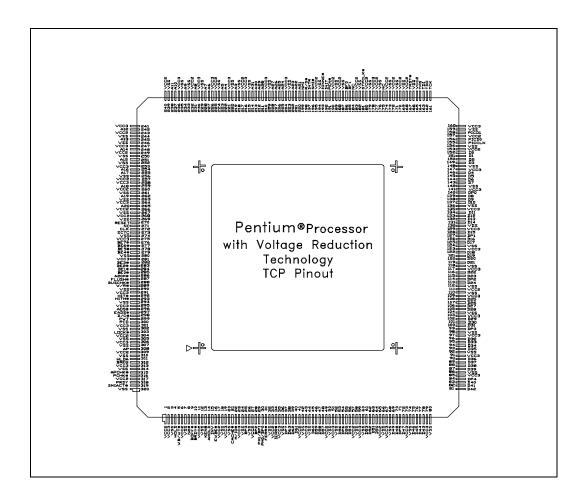

TCP: Applies to the listed stepping of a mobile Pentium processor in a TCP

package only.

Change bar to left of table row indicates this erratum is either new or

modified from the previous version of the document.

## **Specification Changes**

| No. | сС0 | mcC0   | E0 | Plans | Specification Changes                                                                                           |

|-----|-----|--------|----|-------|-----------------------------------------------------------------------------------------------------------------|

| 1   | Х   | Х      | Х  | Doc   | IDT limit violation causes GP fault, not interrupt 8                                                            |

| 2   |     | Note 1 |    | Doc   | 150 MHz active power dissipation (typical) change                                                               |

| 3   | Х   | Х      | Х  | Doc   | Redundant timing spec: t42d for all bus frequencies                                                             |

| 4   |     |        |    | Doc   | Stop clock power                                                                                                |

| 5   |     |        |    | Doc   | Max valid delay A3 – A31                                                                                        |

| 6   |     |        |    | Doc   | Max valid delay data bus D0 – D63                                                                               |

| 7   |     |        |    | Doc   | Maximum Stop-Grant/AutoHALT Power                                                                               |

| 8   |     |        |    | Doc   | TCK VIL                                                                                                         |

| 9   |     |        |    | Doc   | 2/7 bus fraction                                                                                                |

| 10  |     |        |    | Doc   | 233-MHz Icc specifications                                                                                      |

| 11  |     |        |    | Doc   | Active power                                                                                                    |

| 12  |     | Note 4 |    | Doc   | 133-MHz current and power specifications                                                                        |

| 13  |     | Note 1 |    | Doc   | 1/2 bus fraction                                                                                                |

| 14  |     |        |    | Doc   | Maximum thermal design power                                                                                    |

| 15  |     |        |    | Doc   | PCHK# Low state output current in DP mode                                                                       |

| 16  |     |        |    | Doc   | Absolute maximum rating for Vcc3                                                                                |

| 17  |     |        |    | Doc   | 120/60 MHz Vcc, Icc, power, DC and AC specifications                                                            |

| 18  |     |        |    | Doc   | 166- and 266-MHz Vcc2, Icc and power specifications                                                             |

| 19  |     |        |    | Doc   | Mobile 200/66 MHz on 0.35 micron Vcc2, Icc, Tcase and power specifications                                      |

| 20  |     |        |    | Doc   | Low Voltage 266 MHz on 0.25 micron Process Technology (for TCP only) VCC , ICC , TCASE and Power Specifications |

## NOTE:

I

This item does not apply to Pentium<sup>®</sup> processors for embedded applications. For the full text of this item, refer to the Pentium<sup>®</sup> Processor Specification Update, order number 242480.

| No. | сС0    | mcC0   | E0    | Plans                 | S-Spec Changes                                                                                                                         |

|-----|--------|--------|-------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1   |        |        |       | Fixed                 | t6a, t6b, max valid delay A31 - A3, BE7# - BE0#, ADS#, LOCK#                                                                           |

| 2   | Note 1 |        |       | Fixed                 | Minimum required voltage separation between Vcc3 and Vcc2                                                                              |

| 3   |        | Note 1 |       |                       | VIH for TRST#                                                                                                                          |

| 4   |        |        |       | Fixed                 | V <sub>I</sub> L for BF and BF1 is reduced                                                                                             |

| 5   |        | Х      |       | Fixed                 | Boundary scan timing changes                                                                                                           |

| 6   |        | Х      |       | Fixed                 | SPGA Vcc2 supply voltage change                                                                                                        |

| 7   |        | Note 1 |       | Fixed                 | AC specifications for the Pentium Processor with Voltage Reduction Technology                                                          |

| 8   |        | Х      |       | Fixed                 | Reduced VIL for TCK                                                                                                                    |

| 9   |        | Note 1 | •     | Fixed                 | Mixing steppings in dual processing mode                                                                                               |

| 10  | Х      |        |       | Fixed                 | MD/VR/VRE specifications                                                                                                               |

| 11  |        |        |       | Fixed                 | 120-MHz and 133-MHz parts (Q0707, Q0708, Q0711, Q0732, Q0733, Q0751, Q0775, SK086, SX994, SK098, SU033) do not support dual processing |

| 12  |        |        |       | Fixed                 | 120-MHz and 133-MHz parts (Q0707, Q0708, Q0711, Q0733, Q0751, Q0775, SK086, SK098) do not support FRC                                  |

| 13  |        |        |       | Fixed                 | 120-MHz and 133-MHz parts (Q0707, Q0708, Q0711, Q0733, Q0751, Q0775, SK086, SK098) Vcc to CLK startup specification                    |

| 14  |        |        |       | Fixed                 | 120-MHz and 133-MHz parts (Q0707, Q0708, Q0711, Q0733, Q0751, Q0775, SK086, SK098) current leakage on PICD1 pin                        |

| 15  |        | Note 1 |       | Fixed                 | Mobile stop clock power                                                                                                                |

| 16  |        |        |       | Fixed                 | Ін, input leakage current                                                                                                              |

| 17  |        |        |       | NoFix                 | Max valid delay A3 – A31 (Replaced by a Spec Change)                                                                                   |

| 18  |        |        |       | Fixed                 | Max valid delay ADS#                                                                                                                   |

| 19  |        |        | Fixed | Max valid delay HITM# |                                                                                                                                        |

| 20  |        |        |       | NoFix                 | Max valid delay data bus D0 – D63 (Replaced by a Spec Change)                                                                          |

| 21  |        |        |       | Fixed                 | Desktop stop clock power                                                                                                               |

| 22  |        |        |       | Fix                   | Min valid delay data bus D0 – D63                                                                                                      |

This item does not apply to Pentium processors for embedded applications. For the full text of this item, refer to the Pentium® Processor Specification Update, order number 242480.

## Errata (Sheet 1 of 5)

| Fixed Stanch trace messages during lock cycles  Fixed Breakpoint or single-step may be missed for one instruction following STI  Fixed Breakpoint or single-step may be missed for one instruction following STI  Fixed Processor cycle may be missed for one instruction following STI  Note 1  Note 2  Note 3  Note 4  Fixed Processor core may not serialize on bus idle  Fixed Processor core may not serialize on bus idle  Fixed SMIACT# premature assertion during replacement writeback cycle  STPCLK# deassertion not recognized for 5 CLKs after BRDY# returned  Fixed Fixed SMIACT# premature assertion during replacement writeback cycle  STPCLK# deassertion not recognized for 5 CLKs after BRDY# returned  Fixed STPCLK# deassertion during execution of the HALT instruction hangs system  Code cache lines are not invalidated if snooped during AutoHALT or Stop-Grant states  Fixed STPCLK# assertion during execution of the HALT instruction hangs system  Nofix Nofix Ax X X Fixed RUNBIST restrictions when run through boundary scan circuitry  Fixed StrpCk# restrictions during EWBE#  Fixed Multiple allocations during EWBE#  Fixed Note 1  Fixed Singht precision loss for floating-point divides on specific operand pairs  Fixed Singht precision loss for floating-point divides on specific operand pairs  Fixed Fixed Fixed Fixed Singht precision loss for floating-point divides on specific operand pairs  Fixed Fixed Fixed Singht precision loss for floating-point divides on specific operand pairs  Fixed Fixed Fixed Fixed Processor page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT  Brack Ax X X Fixed Branch trace message corruption                                                                                                                                                                    | No. | cC0 | mcC0   | E0 | Plans | Errata                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------|----|-------|-----------------------------------------------------------------|

| Fixed STI  Fixed by Fixed Fixed by Fixed Fixed by Fixed b | 1   |     |        |    | Fixed | Branch trace messages during lock cycles                        |

| Fixed   Fixed   Fried   Fried  | 2   |     |        |    | Fixed |                                                                 |

| Fixed SMI# and FLUSH# during shutdown  Note 1  Fixed FLUSH# with a breakpoint pending causes false DR6 values  Fixed Processor core may not serialize on bus idle  Fixed Processor core may not serialize on bus idle  Fixed SMIACT# premature assertion during replacement writeback cycle  STPCLK# deassertion not recognized for 5 CLKs after BRDY# returned  Fixed Future Pentium OverDrive® processor FERR# contention in two-socket systems  Fixed STPCLK# assertion during execution of the HALT instruction hangs system  STPCLK# assertion during execution of the HALT instruction hangs system  STPCLK# assertion during execution of the HALT instruction hangs system  NoFix NoFix NoFix Prace and the processor of the HALT instruction hangs system  Tixed Stream NoFix NoFix Prace and the processor of the HALT instruction hangs system  STPCLK# assertion during execution of the HALT instruction hangs system  NoFix Prace And Total Prac | 3   |     |        |    | Fixed |                                                                 |

| Fixed No shutdown after IERR#  Fixed FluSH# with a breakpoint pending causes false DR6 values  Fixed FluSH# with a breakpoint pending causes false DR6 values  Fixed Processor core may not serialize on bus idle  Fixed SMIACT# premature assertion during replacement writeback cycle  STPCLK# deassertion not recognized for 5 CLKs after BRDY# returned  Fixed Future Pentium OverDrive® processor FERR# contention in two-socket systems  Code cache lines are not invalidated if snooped during AutoHALT or Stop-Grant states  Fixed STPCLK# assertion during execution of the HALT instruction hangs system  NMI or INIT during HALT within SMM may cause large amount of bus activity  STPCLK# restrictions when run through boundary scan circuitry  Fixed FRC mode miscompare due to uninitialized internal register  STPCLK# restrictions during EWBE#  Fixed Multiple allocations into branch target buffer  Fixed Overflow undetected on some numbers on FIST  Fixed Six operands result in unexpected FIST operation  Fixed Six operands result in unexpected FIST operation  Fixed Sinop with table-walk violation may not invalidate snooped line  Fixed Silght precision loss for floating-point divides on specific operand pairs  Fixed FluSH#, INIT or machine check dropped due to floating-point exception  Fixed CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4   |     |        |    | Fixed | NMI or INIT in SMM with I/O restart during single-stepping      |

| Fixed   FLUSH# with a breakpoint pending causes false DR6 values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5   |     |        |    | Fixed | SMI# and FLUSH# during shutdown                                 |

| Note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6   |     |        |    | Fixed | No shutdown after IERR#                                         |

| Fixed   Processor core may not serialize on bus idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7   |     |        |    | Fixed | FLUSH# with a breakpoint pending causes false DR6 values        |

| STPCLK# deassertion not recognized for 5 CLKs after BRDY# returned  Fixed Future Pentium OverDrive® processor FERR# contention in two-socket systems  Fixed STPCLK# assertion during execution of the HALT instruction hangs system  13 Fixed STPCLK# assertion during execution of the HALT instruction hangs system  14 X X X NoFix NMI or INIT during HALT within SMM may cause large amount of bus activity  15 X X X Fixed RUNBIST restrictions when run through boundary scan circuitry  16 X X Fixed FRC mode miscompare due to uninitialized internal register  17 STPCLK# restrictions during EWBE#  Fixed Multiple allocations into branch target buffer  Fixed 100-MHz REP MOVS speed path  Fixed Overflow undetected on some numbers on FIST  Fixed Six operands result in unexpected FIST operation  Fixed Snoop with table-walk violation may not invalidate snooped line  Fixed Snoop with precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8   |     | Note 1 |    | Fixed | Processor core may not serialize on bus idle                    |

| Fixed Fixed RUNBIST restrictions when run through boundary scan circuitry  18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9   |     |        |    | Fixed | SMIACT# premature assertion during replacement writeback cycle  |

| Fixed two-socket systems  Fixed Stop-Grant states  Fixed STPCLK# assertion during execution of the HALT instruction hangs system  14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10  |     |        |    |       | j v                                                             |

| Fixed Stop-Grant states  Fixed STPCLK# assertion during execution of the HALT instruction hangs system  14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11  |     |        |    | Fixed |                                                                 |

| 14 X X X NoFix NoFix NoFix Pixed System  15 X X X Fixed RUNBIST restrictions when run through boundary scan circuitry  16 X X Fixed FRC mode miscompare due to uninitialized internal register  17 STPCLK# restrictions during EWBE#  Fixed Multiple allocations into branch target buffer  Fixed 100-MHz REP MOVS speed path  Fixed Overflow undetected on some numbers on FIST  Fixed Six operands result in unexpected FIST operation  Fixed Snoop with table-walk violation may not invalidate snooped line  Fixed Slight precision loss for floating-point divides on specific operand pairs  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12  |     |        |    | Fixed |                                                                 |

| 14 X X X NOFIX activity  15 X X X Fixed RUNBIST restrictions when run through boundary scan circuitry  16 X X Fixed FRC mode miscompare due to uninitialized internal register  17 STPCLK# restrictions during EWBE#  Fixed Multiple allocations into branch target buffer  Fixed 100-MHz REP MOVS speed path  Fixed Overflow undetected on some numbers on FIST  Fixed Six operands result in unexpected FIST operation  Fixed Snoop with table-walk violation may not invalidate snooped line  Fixed Slight precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13  |     |        |    | Fixed |                                                                 |

| 16 X X Fixed FRC mode miscompare due to uninitialized internal register  17 STPCLK# restrictions during EWBE#  18 Fixed Multiple allocations into branch target buffer  19 Fixed 100-MHz REP MOVS speed path  10 Fixed Overflow undetected on some numbers on FIST  11 Fixed Six operands result in unexpected FIST operation  12 Fixed Snoop with table-walk violation may not invalidate snooped line  13 Fixed Slight precision loss for floating-point divides on specific operand pairs  14 Fixed Floating-point operations may clear alignment check bit  15 CMPXCHG8B across page boundary may cause invalid opcode exception  16 NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14  | Х   | Х      | Х  | NoFix |                                                                 |

| STPCLK# restrictions during EWBE#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15  | Х   | Х      | Χ  | Fixed | RUNBIST restrictions when run through boundary scan circuitry   |

| Fixed Multiple allocations into branch target buffer  Fixed 100-MHz REP MOVS speed path  Fixed Overflow undetected on some numbers on FIST  Fixed Six operands result in unexpected FIST operation  Fixed Snoop with table-walk violation may not invalidate snooped line  Fixed Slight precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16  | Х   |        | Χ  | Fixed | FRC mode miscompare due to uninitialized internal register      |

| Fixed 100-MHz REP MOVS speed path  Fixed Overflow undetected on some numbers on FIST  Fixed Six operands result in unexpected FIST operation  Fixed Snoop with table-walk violation may not invalidate snooped line  Fixed Slight precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  Fixed CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17  |     |        |    |       | STPCLK# restrictions during EWBE#                               |

| Fixed Six operands result in unexpected FIST operation  Fixed Snoop with table-walk violation may not invalidate snooped line  Fixed Slight precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18  |     |        |    | Fixed | Multiple allocations into branch target buffer                  |

| Fixed Six operands result in unexpected FIST operation  Fixed Snoop with table-walk violation may not invalidate snooped line  Slight precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19  |     |        |    | Fixed | 100-MHz REP MOVS speed path                                     |

| Pixed Snoop with table-walk violation may not invalidate snooped line  Slight precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20  |     |        |    | Fixed | Overflow undetected on some numbers on FIST                     |

| Pixed Slight precision loss for floating-point divides on specific operand pairs  Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21  |     |        |    | Fixed | Six operands result in unexpected FIST operation                |

| 23 Fixed Sight precision loss for locating-point divides on specific operand pairs  24 Fixed FLUSH#, INIT or machine check dropped due to floating-point exception  25 Fixed Floating-point operations may clear alignment check bit  26 CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22  |     |        |    | Fixed | Snoop with table-walk violation may not invalidate snooped line |

| 25 Exception  26 Exception  Fixed Floating-point operations may clear alignment check bit  CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23  |     | Note 1 |    |       |                                                                 |

| 26 Fixed CMPXCHG8B across page boundary may cause invalid opcode exception  NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24  |     |        |    |       |                                                                 |

| 26 exception 27 NoFix Single-step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25  |     |        |    | Fixed | Floating-point operations may clear alignment check bit         |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26  |     |        |    | Fixed |                                                                 |

| 28 X X Fixed Branch trace message corruption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27  |     |        |    |       | Single-step debug exception breaks out of HALT                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28  | Х   | Х      | Х  | Fixed | Branch trace message corruption                                 |

<sup>1.</sup> This item does not apply to Pentium processors for embedded applications. For the full text of this item, refer to the *Pentium® Processor Specification Update*, order number 242480.