# I<sup>2</sup>ICE<sup>™</sup> Integrated Instrumentation and In-Circuit Emulation System

- **Provides Real-Time In-Circuit Emulation**

- Offers Symbolic Debugging Capabilities

- Accesses Memory Locations and Program Variables (Including Dynamic Variables) Using Program-Defined Names

- Maintains a Virtual Symbol Table

- Offers Multi-Condition, Multi-Level,

Multi-Probe Break and Trace Capability

- Provides Built-In AEDIT Editor to Allow Editing of Development System Files without Exiting from I<sup>2</sup>ICE Operation

- Provides Low Cost Conversions Among 8086, 8088, 80186, 80188 and 80286 Microprocessors

- Simultaneously Controls up to Four Microprocessors for Debugging Multiprocessor Systems for a Single Work Station

- Supports Common Memory between Processor without Any User System Hardware

- Offers an Integrated 16-Channel 100-MHz Logic Timing Analyzer

- Maps User Program Memory into a Maximum of 288K Zero-Wait-State RAM (Zero Wait-States up to 10 MHz)

- Maps User I/O to Console or to Debugging Procedures

- Provides Disassembly and Single-Line Assembly to Help with On-Line Code Patching

- Common Human Interface Provided by the PSCOPE-86 Debugging Language and the I<sup>2</sup>ICE Command Language

- Uses Integrated Command Directory, ICD™, for Command Syntax Direction/ Correction to Ease Debug Operations

The Intel Integrated Instrumentation and In-Circuit Emulation (I²ICE™) system aids the design of systems that use the 8086, 8088, 80186, 80188, and 80286 microprocessors. The I²ICE system combines symbolic software debugging, in-circuit emulation, and the optional Intel Logic Timing Analyzer (iLTA). Support features for the 8087 and 80287 coprocessors are also included. For the 8086/8088, 80186/80188, and 80286 processors, the I²ICE system support programs written in "C", PL/M, FORTRAN, Pascal, Ada\*, and assembly language. Up to four I²ICE system instrumentation chassis can be hosted by one of Intel's Intellec® microcomputer development systems or by an IBM PC AT or PC XT.

210469-1

<sup>\*</sup>Ada is a trademark of the Joint Ada Program Office. U.S. Department of Defense.

#### PHYSICAL DESCRIPTION

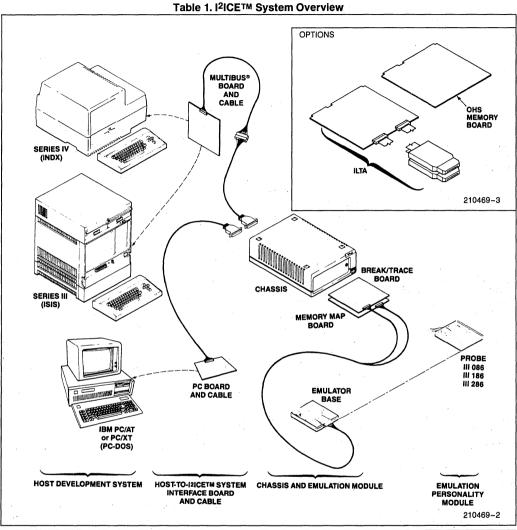

The I²ICE system hardware consists of the host interface board, the I²ICE system instrumentation chassis, the emulation base module, the emulation personality module, a host/chassis cable, interchassis cables (for multiple chassis systems), a user cable, optional high-speed memory boards, and an optional logic timing analyzer. The I²ICE system software consists of I²ICE system host software, I²ICE system probe software, confidence tests, PSOPE 86, and optional iLTA software. Table 1 shows elements of the I²ICE system.

The host interface board resides in the host development system. A cable connects the host interface board to the I<sup>2</sup>ICE system instrumentation chassis. Another cable connects the I<sup>2</sup>ICE system instrumentation chassis to the buffer box.

The instrumentation chassis contains high-speed zero-wait-state emulation memory, break-and-trace logic, memory and I/O maps, and the emulation clips assembly.

The chassis may also contain the optional logic timing analyzer and optional high-speed memory. High-speed memory is expandable from 32K bytes to 288K bytes in 128K increments.

The buffer box contains the emulation personality module. This module configures the I<sup>2</sup>ICE system for a particular iAPX microprocessor. The user cable connects the buffer box to user prototype hardware.

The host development system may host up to four I<sup>2</sup>ICE system instrumentation chassis. Each chassis may have its own buffer box, user cable, emulation clips, optional high-speed memory boards, and logic timing analyzer.

#### **FUNCTIONAL DESCRIPTION**

#### **Resource Borrowing**

The I<sup>2</sup>ICE system memory map allows the prototype system to borrow memory resources from the I<sup>2</sup>ICE system.

If prototype memory is not yet available, the user program may reside in I2ICE system memory. Because this memory is RAM, changes can be made quickly and easily. For example, if the prototype contains EPROM, it does not need to be erased and reprogrammed during development.

Later, as prototype memory becomes available, the verified user program can be reassigned, memory block by memory block to prototype memory.

### The I<sup>2</sup>ICE™ System Memory Map

The I<sup>2</sup>ICE system can direct (map) an emulated microprocessor's memory space (the user program memory) to any combination of the following:

- High-speed I<sup>2</sup>ICE system memory—this consists of 32K bytes of programamble wait-state memory (programmable from 0 to 15). This memory resides in the I<sup>2</sup>ICE system chassis on the map-I/O board

- Optional high-speed I<sup>2</sup>ICE system memory—this consists of up to 256K bytes of programmable wait-state memory (0 wait-states up to 10 MHz). This memory resides in the I<sup>2</sup>ICE system chassis on one or two optional high-speed memory boards (128 K bytes each).

- MULTIBUS® bus memory (host system memory)—this resides in the host development system itself. (Any amount of unused host memory can be used in 1K increments.) Note that this feature is not available for a PC host.

- User memory—this resides in the user prototype hardware.

When a user program runs in I2ICE system memory or user memory, the I2ICE system emulates in real time. A memory access to MULTIBUS bus memory, however, inserts approximately 25 wait-states into the memory cycle.

#### **Access Restrictions**

In addition to directing memory accesses, the following access restrictions can be specified:

- Read-only—the I<sup>2</sup>ICE system displays an error message if a user program attempts to write to an area of memory designated as read-only. The user can, however, write to a read-only area with I<sup>2</sup>ICE system commands.

- Read/write, no verify—normally, the I<sup>2</sup>ICE system performs a read-after-write verification after program loads and after writing to memory with an I<sup>2</sup>ICE system command. The I<sup>2</sup>ICE system can suppress this verification. For example, if a prototype has memory-mapped I/O, a verifying read may change the state of the I/O device.

- Guarded—initially, the I<sup>2</sup>ICE system puts all memory in a guarded state. Neither the user program nor the I<sup>2</sup>ICE system user can access guarded memory.

# The I<sup>2</sup>ICE™ System I/O Map

The I<sup>2</sup>ICE system can direct (map) an emulated microprocessor's I/O space to the host development

| Name                       | Description                                                                                                                                                                                                                                                                             |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Development<br>System | Required for all applications. Use one of the following:  Intellec Series III development system  Intellec Series IV development system  IBM PC AT or PC XT (with 512K bytes of available memory and version 3.0 of PC DOS)  IBM 50 system (available in Japan; features <i>kanji</i> ) |

Table 1. I<sup>2</sup>ICE<sup>TM</sup> System Overview (Continued)

| Name                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host-to-l <sup>2</sup> ICE System<br>Interface Board, Cable,<br>and Host Software | Required for communication between the host and the I²ICE system.  • MULTIBUS® bus interface board for Series III and Series IV (product code III520)  • Host-to-I²ICE system cable for Series III and Series IV (product code III530 or                                                                                                                                                                                                                                                                       |

|                                                                                   | III531)  • I <sup>2</sup> ICE system host software for the Series III and Series IV (product code                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                   | III951A, B, or C)  • Package with PC host interface board, cable and PC DOS version of I <sup>2</sup> ICE host software (product code III520AT954D)                                                                                                                                                                                                                                                                                                                                                            |

| Instrumentation Chassis and Emulation Module                                      | Required for real-time microprocessor emulation, break and trace capability, and memory and i/O capability.  Instrumentation chassis (product code III514B) has four board slots:  1 slot for break/trace board  1 slot for map-I/O board  2 slots for 1 (or 2) optional high-speed memory board(s) and/or 1 optional logic timing analyzer board  Maximum of four chassis for multi-probe applications  Emulation module (product code III620) includes break/trace board, map-I/O board, and buffer base box |

| Emulation Personality<br>Module (Probe) and Probe<br>Software                     | Required for emulation of specific microprocessors: 8086/8088, 80186/80188, or 80286.  • Module includes personality board, buffer box cover, and user cable  • Series III or IV: Order probe and probe software separately  • PC host: Probe and probe software packaged together                                                                                                                                                                                                                             |

| Logic Timing Analyzer<br>(iLTA) [not shown]                                       | Required for acquisition and storage of events and glitches for signal measurement applications.  Complete with iLTA board (mounts in instrumentation chassis), probe pods, and cables  User Series III or Series IV host (cannot be used with the IBM PC AT and PC XT)                                                                                                                                                                                                                                        |

| Optional High-Speed<br>Memory Board (OHS) [not<br>shown]                          | Required for memory expansion.  128K bytes of programmable (0 to 15) wait-state memory  One or two boards mount in the instrumentation chassis                                                                                                                                                                                                                                                                                                                                                                 |

system's console, to the prototype system, to debugging procedures, or to a combination of these.

# SIMULATING I/O WITH THE HOST DEVELOPMENT CONSOLE

Suppose a user program requires input from an I/O device not yet part of the prototype. Map the input port range assigned to that device to the host development systems' console. Then, when the user program requires input, it halts and the I<sup>2</sup>ICE system console displays a message requesting the data. When you enter the required data at the keyboard, the user program continues.

# SIMULATING I/O WITH I<sup>2</sup>ICE™ SYSTEM DEBUGGING PROCEDURES

Procedures that supply the needed input data can be written in the I<sup>2</sup>ICE system command language. When setting up the I/O map, the user specifies that the I/O procedure is invoked when certain I/O ports are accessed.

I/O ports are mapped in blocks of 64 byte-wide ports or 32 word-wide ports. A total of 64K byte-wide ports or 32K word-wide ports can be mapped.

#### Symbolic Debugging

With symbolic debugging, a memory location can be referenced by specifying its symbolic reference. A symbolic reference is a procedure name, line number, or label in the user program that corresponds to a location in the user program's memory space.

#### TYPICAL SYMBOLIC FUNCTIONS

Symbolic functions include:

- Changing or inspecting the value and type of a program variable by using its program-defined name, rather than the address of the memory location where the variable and a hexadecimal value for the data are stored.

- Defining break and trace events using sourcecode symbols.

With symbolic debugging, the user can reference static variables, dynamic (stack-resident) variables, based variables, and record structures combining primitive data types. The primitive data types are ADDRESS, BOOLEAN, BYTE BCD, CHAR, WORD, DWORD, SELECTOR, POINTER, three INTEGER Types, and four REAL types.

#### THE VIRTUAL SYMBOL TABLE

The I<sup>2</sup>ICE system maintains a virtual symbol table for program symbols; that is, the entire symbol table need not fit into memory at the same time. (The size of the virtual symbol table is constrained only by the capacity of the storage device.)

The I<sup>2</sup>ICE system divides the symbol table into pages. If a program's symbol table is large, the I<sup>2</sup>ICE system reads only some of the symbol table pages into memory. When the user references a variable whose symbol is not currently defined in memory, the I<sup>2</sup>ICE system reads the needed symbol table page from disk into memory.

# Breakpoint, Trace, and Arm Specifications

With I2ICE system commands, breakpoint, trace, and arm specifications can be defined.

Breakpoints allow halting of a user program in order to examine the effect of the program's execution on the prototype. With the I<sup>2</sup>ICE system, a breakpoint can be set at a particular memory location or at a particular statement in a user program (including high-level language programs). A break can also be set to occur when the user program enters or ac-

cesses a specified memory partition or reads or writes a user program variable. When the user program resumes execution, it picks up from where it left off.

Normally, the I<sup>2</sup>ICE system traces while the user program executes. With a trace specification, however, the user can choose to have tracing occur only when specific conditions are met.

An arm specification describes an event or combination of events that must occur before the I<sup>2</sup>ICE system can recognize certain breakpoint and trace specifications. Typical events are the execution of an instruction or the modification of a data value.

The I<sup>2</sup>ICE system command language allows you to specify complex, multilevel events. For example, you can specify that a break occurs when a variable is written, but only if that write occurs within a certain procedure. The execution of the procedure is the arm condition; the variable modification is the break condition. The I<sup>2</sup>ICE system command language allows users to specify complex events with up to four states with four conditions and to use such events as arm, break, or trace conditions; a specified number of events can be used as a condition.

### **Coprocessor Support**

The 8086/8088 emulation personality module provides transparent RQ/GT and MN/MX pin emulation to support real-time prototype systems that use the 8087 as a coprocessor. The 8086/8088 (and the 80186/80188) emulation personality module also provides debugging features specific to the 8087. I2ICE system commands provide access to the 8087's stack, status registers, and flags. The I2ICE system's disassembly and trace features extend to 8087 instructions and data types.

The 80186 and 80286 emulation personality modules also allow the prototype hardware to contain coprocessors. The 80186 probe can qualify break points and collect trace information when the coprocessor drives the status lines (\$\overline{S0} - \overline{S2}\$) in the prescribed manner. The 80286 personality module allows the hardware to contain the 80287 processor extension and provides special debugging features—the user can enable and disable the 80287 and change and examine its registers.

# DUBUGGING WITH THE 12ICETM SYSTEM

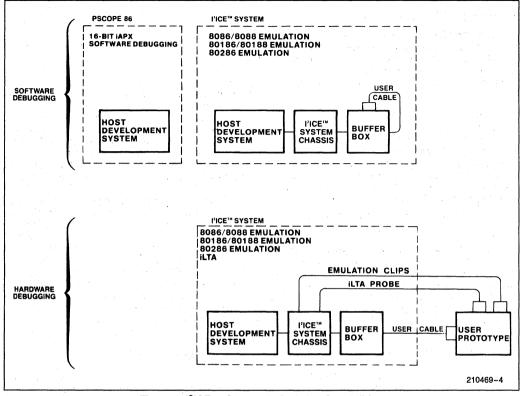

The I2ICE system allows both hardware and software debugging (see Figure 1).

Figure 1. I<sup>2</sup>ICE™ System Debugging Capabilities

- Software debugging—I<sup>2</sup>ICE system commands permit symbolic debugging of user programs written in high-level languages as well as assembly language. By looping the user cable back into the buffer box, a user program can be debugged even if no prototype hardware is present. In a multi-probe environment, the I<sup>2</sup>ICE system can map common memory from the host development system and support semaphore operation even with no user system prototype hardware. This feature makes possible detailed debugging of multi-processor software before the hardware is available.

- Hardware debugging—the I<sup>2</sup>ICE system is a realtime, in-circuit emulator. Trace data are collected in real time, and I<sup>2</sup>ICE system software does

not intrude into user program space. The optional iLTA adds the high-speed timing and data acquisition of a logic timing analyzer.

The userfulness of an I<sup>2</sup>ICE system extends throughout the development cycle, beginning with the symbolic debugging of prototype software and ending with the final integration of debugged software and prototype hardware.

#### **PSCOPE 86**

PSCOPE 86 is a high-level language, symbolic debugger, designed for use with Pascal 86, PL/M 86, and FORTRAN 86. It is a separate product included with Series III and Series IV versions of the I<sup>2</sup>ICE

system; it runs in the host development system. PSCOPE 86 is field-proven, familiar to Intel customers, and suited for the debugging of applications software when the hardware capabilities of the I<sup>2</sup>ICE system are not needed. The PSCOPE 86 and I<sup>2</sup>ICE system command languages are similar. (Note that PSCOPE 86 is available as an option for use with the PC AT or PC XT.)

Designing a product that contains a microcomputer requires close coordination of hardware and software development. A typical design process takes advantage of both the I<sup>2</sup>ICE system and PSCOPE 86. Use PSCOPE 86 for debugging software before downloading the software into a target environment; use the I<sup>2</sup>ICE system for debugging and emulation in the target system.

# THE 12ICE™ SYSTEM COMMAND LANGUAGE

The syntax of I<sup>2</sup>ICE system commands resembles that of a high-level language. The I<sup>2</sup>ICE system command language is versatile and powerful while remaining easy to learn and use.

The Integrated Command Directory (ICD™) assists users with command syntax.

- The ICD directory directs the user in choosing commands from display on the bottom line of the screen. As commands are entered, the bottom line indicates syntax elements available for use in the commands.

- The ICD directory flags syntax errors. Syntax errors are flagged as they occur (rather than after the carriage return is pressed).

- The ICD directory provides on-line help with the HELP command.

Automatic expansion of LITERALLY expressions is available. When the feature is activated, each character string defined by a LITERALLY definition is automatically expanded to its full length.

The I<sup>2</sup>ICE system command language deals with user-created, debugging objects. By manipulating debugging objects, the user can streamline complex debugging sessions.

Debugging objects are uniquely named, user-created, software constructs that the I<sup>2</sup>ICE system uses to manage the debugging environment. The four types of debugging objects are: debugging procedures, LITERALLY definitions, debugging registers, and debugging variables. In the following examples, I<sup>2</sup>ICE system keywords are shown in all caps.

Debugging procedures (named groups of I<sup>2</sup>ICE system commands) can simulate missing software or hardware, collect debugging information, and make troubleshooting decisions. For example, consider a debugging procedure (called init) that simulates input from I/O ports 2 and 4.

The procedure and MAPIO command are given first, followed by an explanation.

```

*DEFINE PROCEDURE init = DO

.*IF %0 = = 2 THEN

..*FORTDATA = 100T

.*ELSE IF %0 = = 4 THEN

..*PORTDATA = 65T ...*END

..*END

```

\*MAPIO O LENGTH 64K ICE (init)

Whenever the MAPIO command maps I/O ports to an I<sup>2</sup>ICE system procedure, three parameters are made available to the procedure (even if the procedure does not use them): %0, %1, %2. The parameter %0 passes the port number; %1 passes a Boolean value that indicates whether read or write I/O activity will occur; and %2 passes a Boolean value that indicates whether the I/O is a byte-wide or a word-wide port. PORTDATA is a pseudo-variable that contains the actual

port data. This procedure specifies that if port 2 is

used, the procedure returns 100 (base ten); if,

however, port 4 is used, the procedure returns 65

LITERALLY definitions are shorthand names for previously defined character strings. LITERALLY definitions can save keystrokes and improve clarity. For example, here is the definition of a LITER-ALLY that saves keystrokes. This LITERALLY allows the user to type DEF for DEFINE.

(base ten).

#### \*DEFINE LITERALLY DEF = "DEFINE"

These definitions may be saved to disk and autoreloaded. In addition, an automatic LITERALLY expansion feature can be turned on and off.

• Debugging registers are user-created, software registers that hold arm, breakpoint, and trace specifications. The I<sup>2</sup>ICE system can be ordered to emulate the user program and specify one or more debugging registers. There is no need to reenter the specification for each emulation. For example here is the definition of a debugging register called pay that contains a trace specification. This example takes advantage of the previous LITERALLY definition.

\*DEF TRCREG pay = :cmaker.payment

To emulate a user program and trace only during the procedure **payment**, specify the debugging register **pay** as part of the GO command.

\*GO USING pay

Debugging variables are user-created variables used with I2ICE system commands. For example, here is the definition of a debugging variable called **begin**. Its type is POINTER.

\*DEFINE POINTER begin = 0020H:0006H During a debugging session, the user can set the execution point to this pointer value by typing:

The I<sup>2</sup>ICE system pseudo-variable \$ represents the current execution point.

# **Example of a Debugging Session**

Figures 2, 3, and 4 illustrate some of the key capabilities of the I<sup>2</sup>ICE system. The user program is written in Pascal-86. It was compiled, linked, and located on an Intellec Series III development system. The resulting file consists of absolute code and is called CMAKER.86. Figure 2 shows the Pascal listing; Figure 3 shows a sample debugging session; and Figure 4 briefly explains the debugging steps shown in Figure 3.

The CMAKER.86 program controls an automatic changemaker. The program reads the amount tendered (the variable **paid**) and the amount of the purchase (the variable **purchase**). It calculates the coins needed for change and asserts control signals to a change release mechanism by writing an output port. Each of the lower four bits of the output port controls the release of a different coin denomination.

# I<sup>2</sup>ICETM System Command Functions

The I<sup>2</sup>ICE system command language contains a number of functional categories.

- Emulation commands—the GO command instructs the I2ICE system to begin emulation. The user can also command the I2ICE system to break or trace under certain specified conditions.

- Utility commands—these are general purpose commands for use in a debugging environment.

For example, one use of the EVAL command is to

calculate the nearest source-code line number that corresponds to the address of an assembly language instruction. The HELP command provides on-line assistance. The EDIT command invokes a menu-driven text editor (AEDIT) that allows updating of debugging object definitions and editing of development system files without exiting from the I<sup>2</sup>ICE system. A command line editior and history key are also provided.

- Environment commands—these are commands that set up the debugging environment. For example, the MAP command sets up the memory map. Another environment command (WAIT-STATE) inserts wait-states into memory accesses, allowing the simulation of slow memories.

- File handling commands—these are commands that access disk files. Debugging object definitions can be saved in a disk file and loaded in later debugging sessions. Debugging sessions can also be recorded in a disk file for later analysis.

- Probe-specific commands—these are commands whose effects are different for different probes.

For example, the PINS command displays the state of selected signals lines on the current probe.

- Option-specific commands—these are commands that control an optional test/measurement device, such as the logic timing analyzer.

# I<sup>2</sup>ICE™ SYSTEM INSTRUMENTATION SUPPORT

# I<sup>2</sup>ICE™ System Emulation Clips

Eight external input lines are sampled during each processor bus cycle. The I<sup>2</sup>ICE system records the values of these lines in it trace buffer during each execution cycle. The I<sup>2</sup>ICE system can use these values when defining events.

Four additional output lines synchronize I<sup>2</sup>ICE system events with external hardware. Two lines are active and programmable with I<sup>2</sup>ICE system commands. Two other lines, break and trace, allow an I<sup>2</sup>ICE system chassis to be linked to other I<sup>2</sup>ICE system chassis.

# Intel Logic Timing Analyzer (iLTA)

The iLTA analyzer is a chassis-resident, test/measurement module designed to extend the capability of the I<sup>2</sup>ICE system to recognize events and collect data. The iLTA and the I<sup>2</sup>ICE system emulator work together. They can trigger and arm/disarm each other. In addition, waveforms acquired by the

```

SERIES-III Pascal-86, V2.0

Source File: CMAKER.SRC

Object File: CMAKER.OBJ

Controls Specified: XREF, DEBUG, TYPE

NESTING

SOURCE TEXT: MAKER.SRC

STMT

LINE

1

0 0

PROGRAM cmaker:

2

2

0

0

VAR change, coins

:integer;

3

3

0

0

quarters, nickels, dimes, pennies

:integer:

4

4

0

0

paid, purchase

:word;

5

PROCEDURE payment;

6

0

0

7

VAR numberofcoins

6

0

1

:integer;

7

8

0

release

1

:word;

8

9

1

0

BEGIN

(*payment*)

8

10

numberofcoins: = quarters + dimes + nickels + pennies;

1

1

9

while number of coins < > 0 do

11

1

1

10

BEGIN

12

1

1

10

13

release: = 0:

11

14

1

2

if quarters < >0 then

12

15

1

2

BEGIN

12

16

3

release := release + 8;

13

17

1

3

quarters: = quarters - 1

END;

15

19

1

2

if dimes < > 0 then

16

20

1

2

BEGIN

16

21

3

release: = release + 4;

1

17

22

3

dimes: = dimes - 1

END;

19

24

1

2

if nickels < >0 then

20

25

1

2

BEGIN

20

26

1

3

release: = release + 2:

21

27

1

3

nickels: = nickels - 1

END;

23

29

1

2

if pennies < > 0 then

24

30

1

2

BEGIN

24

3

31

1

release: = release + 1;

25

32

1

3

pennies: = pennies -1

27

34

1

2

numberofcoins: = quarters + dimes + nickels + pennies;

28

35

1

2

OUTWRD(130,release);

29

2

36

1

END;

31

37

END:

1

(*payment*)

32

39

0

0

BEGIN (*main*)

32

40

0

INWRD(2,paid);

33

0

41

1

INWRD(70,purchase);

34

42

0

1

change := paid - purchase;

35

43

0

1

:=change mod 100;

36

44

0

1

quarters: = coins div 25;

37

45

0

1

coins

:=coins mod 25;

38

46

0

1

dimes

:=coins div 10;

39

47

0

1

coins

:=coins mod 10;

40

48

0

nickels := coins div 5;

1

41

49

0

1

pennies :=coins mod 5;

42

50

0

payment:

1

43

0

1

END.

(*main*)

210469-5

```

Figure 2. Listing of CMAKER.86

```

(1) *BASE

DECIMAL

(2) *MAP OK LENGTH 32K HS

*MAPIO 0T LENGTH 192T ICE

*MAP

MAP

OK LENGTH

32K HS

MAP

32K LENGTH

992K GUARDED

*MAPIO

MAPIO 00000H LENGTH

000C0H ICE

MAPIO 000C0H LENGTH

0FF40H USER

(3) *LOAD :F1:CMAKER.86

(4) *DEFINE POINTER begin = $

*DEFINE BRKREG pay = :cmaker #9

*DEFINE PROC display = DO

.*WRITE USING (' "quarters = ",T,0,>')quarters

.*WRITE USING (' "dimes = ",T,0")dimes

.*WRITE USING (' "nickels = ".T.0.>')nickels

.*WRITE USING (""pennies = ",T,0")pennies

.*RETURN TRUE

.*END

(5) *GO USING pay

?UNIT 0 PORT 2H REQUESTS WORD INPUT (ENTER VALUE)*100

?UNIT 0 PORT 46H REQUESTS WORD INPUT (ENTER VALUE)*65

Probe 0 stopped at :CMAKER #9 + 4 because of execute break

Break register is PAY Trace Buffer Overflow

(6) *quarters:dimes:numberofcoins

+1

+1

(7) *DEFINE SYSREG wr_number = WRITE AT .:cmaker.payment.numberofcoins &

**CALL display

*GO USING wr__number

quarters = +1 dimes = +1

nickels = +0

pennies = +0

Probe 0 stopped at :CMAKER # 28 + 3 because of bus break

Break register is WR__NUMBER

(8) *numberofcoins

+0

*EVAL release

1100Y 12T CH'..'

(9) *CLIPSOUT = 11Y

(10) *GO FOREVER

?UNIT 0 PORT 82H OUTPUT WORD 0C

?Probe 0 stopped at location 0033:00AEH because of bus not active

Bus address = 0203DE

*$ = begin

```

Figure 3. Sample Debugging Session (Explanations in Figure 4)

- (1) Checking to see that the default radix is decimal.

- (2) Mapping user program memory to I<sup>2</sup>ICE high-speed memory and user I/O ports to the I<sup>2</sup>ICE system console.

- (3) Loading the user program.

- (4) Defining debugging objects.

The debugging variable **begin** is set to \$, an I<sup>2</sup>ICE pseudo-variable representing the current execution point. At this point is the debugging session, \$ is the beginning of the user program.

The break register pay specifies a breakpoint at statement 9 in the user program.

The debuggning procedure display displays the value of some user program variables on the console.

- (5) Beginning emulation with the debugging register pay. The console requests the two input values, paid and purchase. Then, the break occurs.

- (6) Displaying three user program variables.

- (7) Defining another debugging register. The specified event is the writing of the user program variable numberofcoins. When that event occurs, the I<sup>2</sup>ICE system calls the debugging procedure display. In addition to displaying some user program variables, this debugging procedure returns a Boolean value. Because this value is TRUE, the break occurs; if the value were FALSE, emulation would continue.

- (8) Displaying the two user program variables, numberofcoins and release. The EVAL command displays release in binary, decimal, hexadecimal, and ASCII. Unprintable ASCII characters appear as periods (.).

- (9) Asserting both output lines on the emulation clips. These lines are input to the prototype hardware and control a change release mechanism.

- (10) Resuming emulation. The console displays the write of **release** to the output port. The user program finishes exeucting, and the probe stops emulating because of bus inactivity. The \$ is set back to the beginning of the user program in preparation for another emulation.

#### Figure 4. Explanation of Sample Debugging Session in Figure 3

iLTA can be time-aligned with I<sup>2</sup>ICE system traces. (Note that iLTA is not available for use with the PC AT or PC XT.)

The iLTA analyzer brings the flexibility of high-speed triggering and glitch detection to the I<sup>2</sup>ICE system. The iLTA is a general purpose logic timing analyzer, supplemented with special features for microsystem debugging and I<sup>2</sup>ICE system integration. Following are some of iLTA's features.

- 16-channel, 100 MHz asynchronous operation

- 16-channel, 50 MHz asynchronous operation

- Single- or double-height timing waveforms presented with data scrolling, magnification, and delta-time read-out features.

- Minimum 3 nanosecond glitch detection (3 ns + 1 ns/volt for signal swings greater than 3 volts)

- A dual-threshold acquisition mode, with programmable logic level thresholds.

- A burst acquisition mode with window boundary indicators.

- User-defined channel labels and state display radixes.

- Disk storage for preservation and restoration of analyzer setups and acquired waveforms.

- Logic waveform comparison features (compares current acquisitions with pervious traces stored in auxiliary memory or on disk).

- Menu-driven operation and user-friendly display.

The display takes advantage of screen highlighting, blinking characters, and reverse video.

- Powerful post-processing data analysis commands that are part of the I<sup>2</sup>ICE system command language.

- Multiple emulator break/trace and iLTA trigger/ trace conditions may be shared with as many as four emulators and four iLTAs.

### 12ICETM SYSTEM SPECIFICATIONS

## **Host Requirements**

Series III, Series IV, Model 800, or IBM PC AT or PC XT.

512K bytes in host development system memory space.

Two double-density diskette drives or a hard disk.

For the iLTA to run on a Series III, the III-820 board must be installed. Model 800 systems and the IBM PC AT and PC XT systems do not support the iLTA option.

# I<sup>2</sup>ICE™ System Software

I<sup>2</sup>ICE system host software

I<sup>2</sup>ICE system probe software

I<sup>2</sup>ICE system confidence tests

I<sup>2</sup>ICE tutorial

PSCOPE 86 (not currently available for PC-DOS)

Optional iLTA software and iLTA confidence tests

(not available for PC-DOS)

### **System Performance**

Mappable zero wait-state memory (zero wait-states up to 10 MHz for 8086; 8 MHz for 8088 and 80186/80188; and 6 or 8 MHz for 80286): Minimum 32K bytes, maximum 288K bytes

Trace buffer:

1023 x 48 bits

Virtual symbol table:

The number of user program symbols is limited only by available disk space

### **Physical Characteristics**

#### **INSTRUMENTATION CHASSIS**

Width: 17.0 in (43.2 cm)

Height: 8.25 in (21.0 cm)

Depth: 24.13 in (61.3 cm)

Weight: 48 lbs (21.9 kg)

#### HOST/CHASSIS CABLE

10 ft (3.0m) and 40 ft (12.2 m) options for Series III/Series IV host 15 ft (4.6m) for PC host

#### **INTER-CHASSIS CABLE SET**

2 ft (61 cm) and 10 ft (3.0m) options

#### **BUFFER BOX**

Width: 8.5 in (21.6 cm)

Height: 3.0 in (7.6 cm)

Depth: 10.0 in (25.4 cm)

Weight: 8 lbs (3.7 kg)

#### **Electrical Characteristics**

90-132V or 180-264V (selectable) 47-63 Hz 12 amps (AC)

#### **Environmental Requirements**

Operating Temperature: 0°C to 40°C (32°F to

104°F)

Operating Humidity: Maximum of 85% relative

humidity, non-condensing

# **Emulation Clips**

Emulation clipsin lines are sampled once every bus cycle when the address bits become valid on the address bus. During emulation, the I<sup>2</sup>ICE system records the value of the clipsin lines in the trace buffer once very execution cycle.

Table 2. I<sup>2</sup>ICE™ Emulation Clips—DC Characteristics

|                      | Input \                     | Input Voltage                |                                      | Current                         | Output Current |                  |

|----------------------|-----------------------------|------------------------------|--------------------------------------|---------------------------------|----------------|------------------|

| Signal               | Low<br>V <sub>IL</sub><br>V | High<br>V <sub>IH</sub><br>V | Low<br>I <sub>IL</sub><br>μ <b>A</b> | l <sub>IL</sub> l <sub>IH</sub> |                | High<br>OH<br>mA |

| Clipsout Lines       |                             |                              |                                      |                                 | 33 at 0.7V     | 4.8 at 2.0V      |

| SYSBREAK<br>SYSTRACE |                             |                              |                                      |                                 | 38 at 0.7V     | 1.0 at 2.0V      |

| Clipsin Lines        | 1.05                        | 2.5                          | 50                                   | 50                              |                |                  |

### 12ICETM SYSTEM 8086/8088 PROBE HIGHLIGHTS

- Provides up to 10 MHz real-time emulation

- One-megabyte addressing

- · Emulates both Minimum and Maximum modes

- Provides 8087 coprocessor support

Table 3. I<sup>2</sup>ICE™ System 8086/8088 User Interface—DC Characteristics

|                                      | Inp<br>Volt                 |                             | 1                           | put<br>tage                 | 1 -                          | out<br>rent                  |                              |                              | utput<br>urrent                          | san de d                                 |

|--------------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------------------|------------------------------------------|

| Signal                               | Max<br>V <sub>IL</sub><br>V | Min<br>V <sub>IH</sub><br>V | Max<br>V <sub>OL</sub><br>V | Min<br>V <sub>OH</sub><br>V | Max<br>I <sub>IL</sub><br>mA | Max<br>I <sub>IH</sub><br>mA | Max<br>I <sub>OL</sub><br>mA | Max<br>I <sub>OH</sub><br>mA | 3-State<br>Max<br>I <sub>OZL</sub><br>mA | 3-State<br>Max<br>I <sub>OZH</sub><br>mA |

| AD15-AD0                             | 0.8                         | 2.0                         | 0.5                         | 2.0                         | -0.20                        | 0.02                         | 24                           | -12.0                        | -0.20                                    | 0.02                                     |

| A19-A16, BHE/S7                      | 0.8                         | 2.0                         | 0.55                        | 2.0                         | -0.25                        | 0.07                         | 63.9                         | <b>-15.0</b>                 | -0.07                                    | 0.07                                     |

| RD                                   | NA                          | NA                          | 0.55                        | 2.0                         | NA                           | NA                           | 63.9                         | -15.0                        | -0.84                                    | 0.05                                     |

| DEN (SO),<br>DT/R (S1),<br>M/IO (S2) | 0.8                         | 2.0                         | 0.55                        | 2.0                         | -1.20                        | 0.12                         | 18.8                         | -6.6                         | -1.30                                    | 0.12                                     |

| WR (LOCK)                            | NA                          | NA                          | 0.55                        | 2.0                         | NA                           | NA                           | 63.9                         | -15.0                        | -0.94                                    | -0.05                                    |

| ĪNTA (QS1)                           | NA                          | NA                          | 0.5                         | 2.4                         | NA                           | NA                           | 19.1                         | -6.50                        | NA                                       | NA                                       |

| ALE (QS0)                            | NA                          | NA                          | 0.5                         | 2.4                         | NA                           | NA                           | 19.9                         | -6.54                        | NA                                       | NA                                       |

| MN/MX                                | 8.0                         | 2.0                         | NA                          | NA                          | -1.6                         | 0.04                         | NA                           | NA                           | NA                                       | NA                                       |

| NMI                                  | 0.77                        | 2.0                         | NA                          | NA                          | -0.4                         | 0.05                         | NA                           | NA                           | NA                                       | NA                                       |

| CLK, READY*                          | 0.8                         | 2.0                         | NA                          | NA                          | -3.2                         | 0.04                         | NA                           | NA                           | NA                                       | NA                                       |

| INTR                                 | 0.77                        | 2.0                         | NA                          | NA                          | -0.4                         | 0.05                         | NA                           | NA                           | NA                                       | NA                                       |

| TEST                                 | 0.8                         | 2.0                         | NA                          | NA                          | -0.60                        | 0.04                         | NA                           | NA                           | NA                                       | NA                                       |

| RESET                                | 0.8                         | 2.0                         | NA                          | NA                          | -2.2                         | 0.07                         | NA                           | NA                           | NA                                       | NA                                       |

| HOLD (RQ/GT0),<br>HOLDA (RQ/GT1)     | 0.72                        | 2.0                         | 0.80                        | 2.0                         | -1.60                        | -0.11                        | 7.60                         | -7.06                        | NA                                       | NA                                       |

#### \*NOTES:

Negative currents (-) are defined as currents flowing out of a terminal, and positive currents are defined as currents flowing into a terminal. "NA" means "not applicable."

The 8086 and 8088 chip specifications indicate that the chips have an output drive capacity of  $I_{OH}=-400~\mu A$  and  $I_{OL}=2.5~mA$  (2.0 mA for the 8088); the chips' input and 3-state loading specification is  $\pm 10~\mu A$ . As can be seen from the table, the 8086/8088 probe has a greater output drive capacity and presents greater input loading than the 8086 or 8088 chip.

The 8086/8088 probe does not draw any current from the user V<sub>CC</sub>.

# Capacitive Loading—8086/8088 Probe

- The 8086/8088 probe presents the user system with a maximum load of 70 pF (135 pF for INTR, NMI).

- All 8086/8088 probe outputs are capable of driving 0 pF while meeting all the probe's timing specifications. The 8086/8088 probe will drive larger capacitive loads, but with possible performance degradation. Derate the timing specifications by 0.04 ns/pF corresponding to input capacitance of the user system.

$I_{II} = -0.8$  mA and  $I_{IH} = 0.1$  mA if a 74S244 is used at U30 for CLOCK and READY inputs.

# Coprocessor Operation—8086/8088 Probe

- During emulation with external coprocessors, a two-clock delay precedes each RQ, GT, and RLS pulse in MAX mode and each HOLD and HOLDA assertion in MIN mode.

- The user can choose to have the coprocessor run only during emulation or all the time. If the

- coprocessor runs all the time, then during interrogation mode, the coprocessor may have as much as a one-microsecond delay in addition to the two-clock delay mentioned above.

- The I<sup>2</sup>ICE system ignores a coprocessor when the probe is in the reset state. If a coprocessor asserts RQ during this time, the RQ/GT sequence may get out of synchronization. The probe is reset when the I<sup>2</sup>ICE host software loads I<sup>2</sup>ICE probe software.

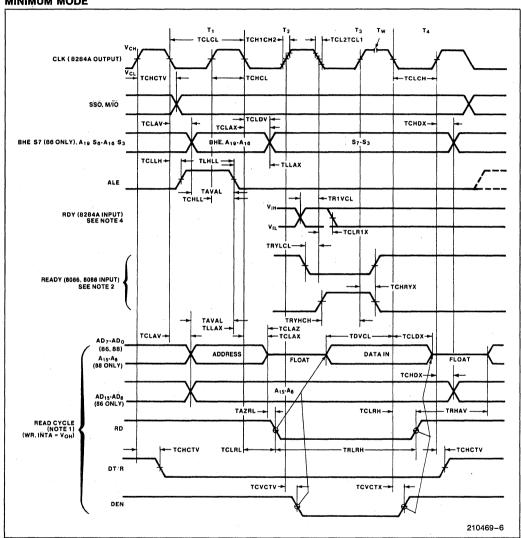

# A.C. CHARACTERISTICS FOR THE I<sup>2</sup>ICETM SYSTEM 8086 PROBE

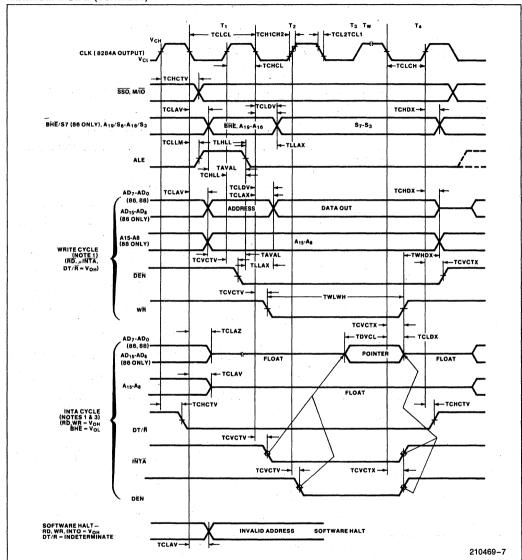

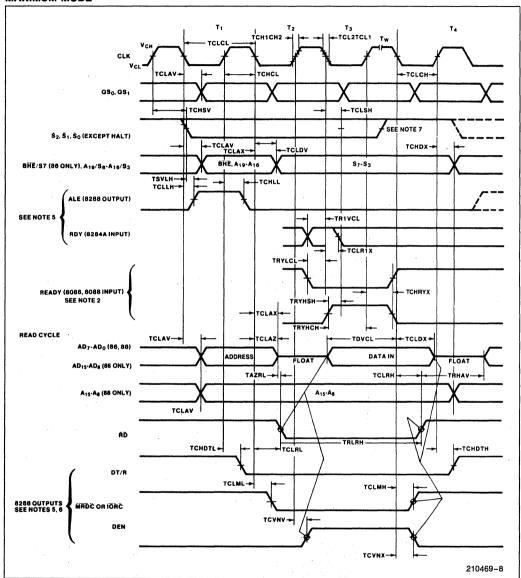

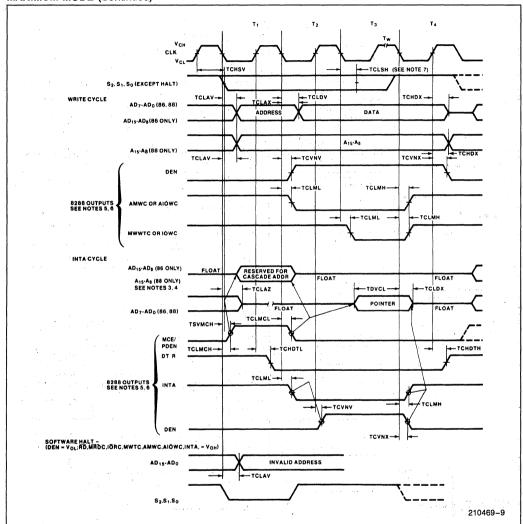

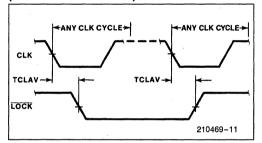

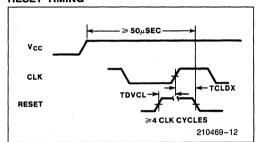

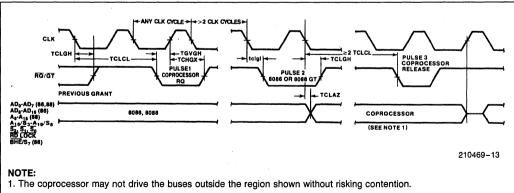

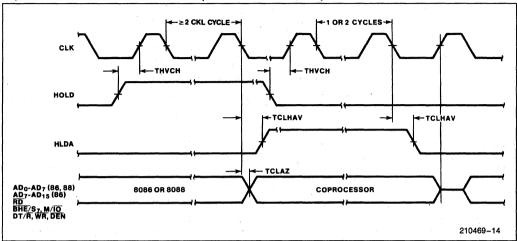

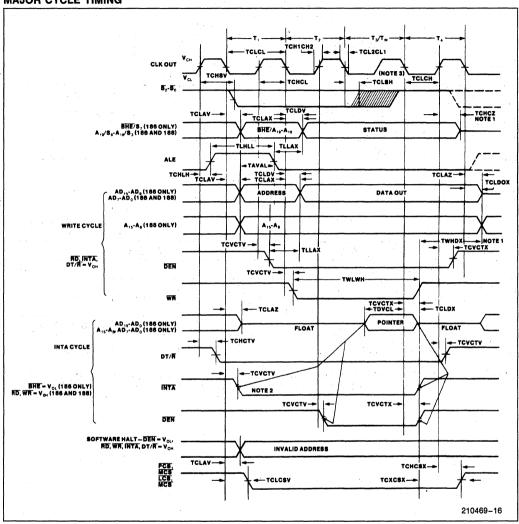

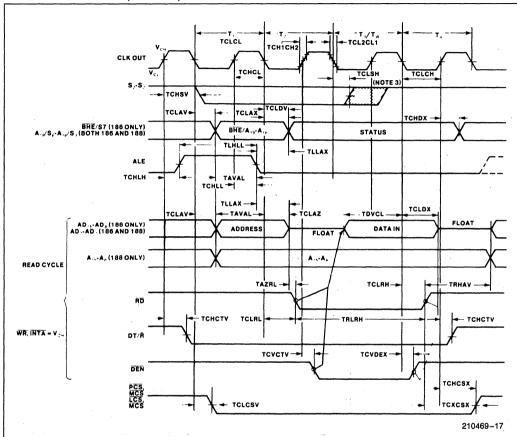

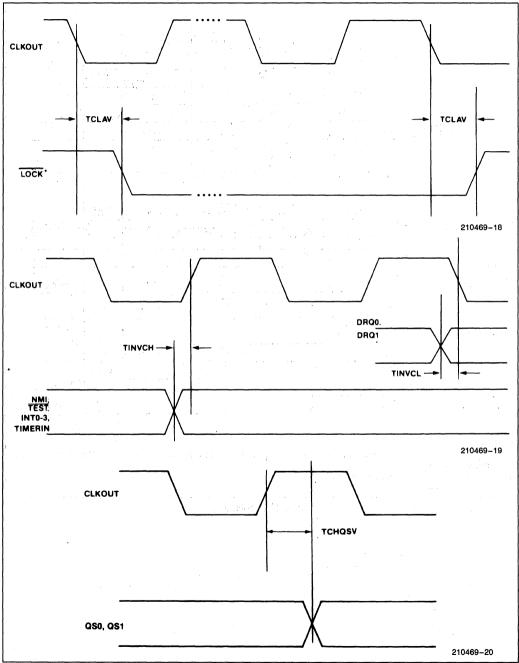

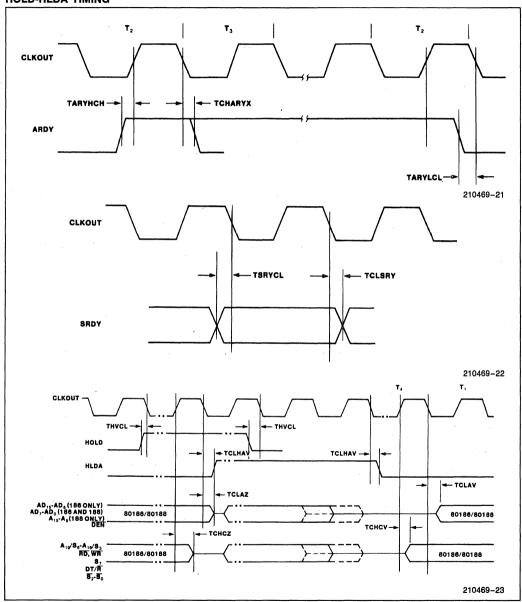

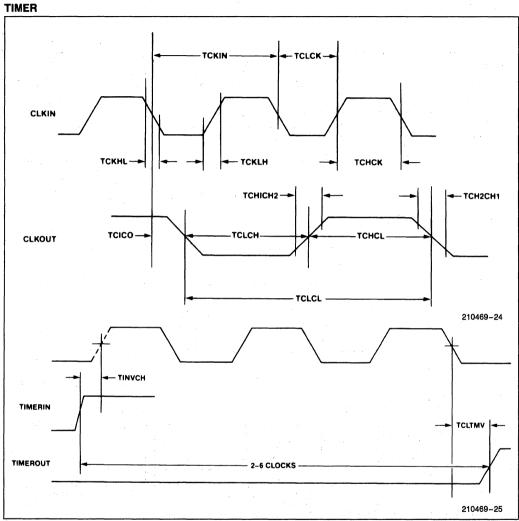

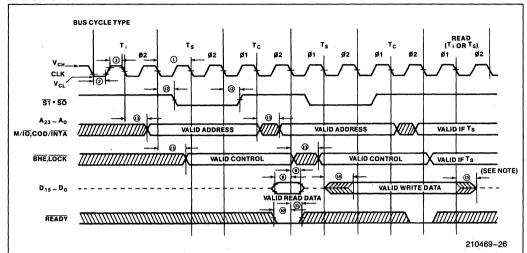

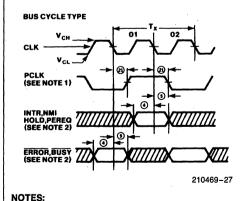

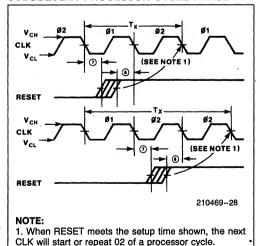

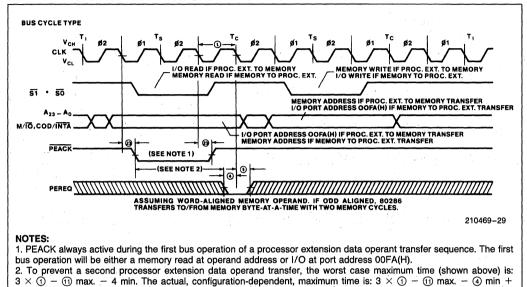

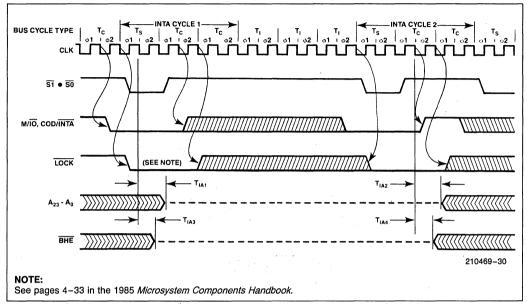

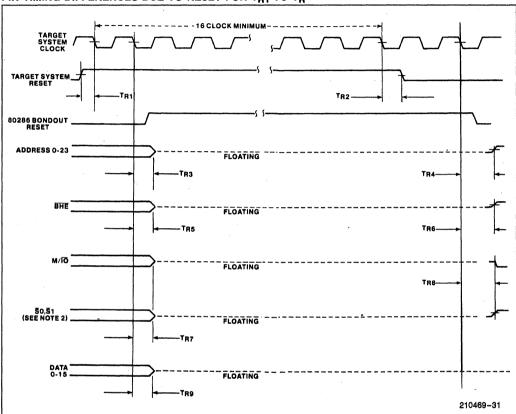

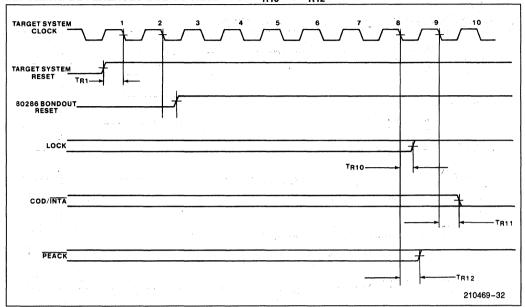

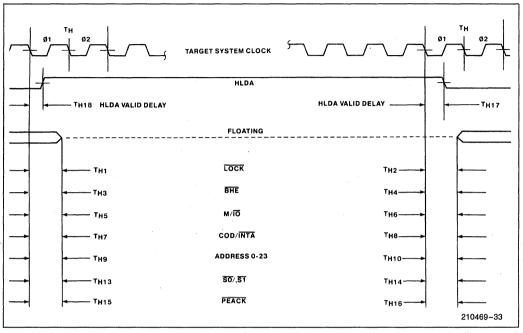

Tables 4 through 7 provide timing information for the 8086 probe. Figures 5 through 12 define the timing symbols.

Table 4 Minimum Complexity System Timing Requirements

|                                        | l able 4. William               | <del></del>                       |        | m Timing Red                              | <u></u> |                                           |        |

|----------------------------------------|---------------------------------|-----------------------------------|--------|-------------------------------------------|---------|-------------------------------------------|--------|

| Min Mode                               | Parameter                       | 5 MHz (8                          | 3086)  | 10 MHz (8                                 | 086-1)  | 8 MHz (8                                  | 086-2) |

| Symbol                                 | raramotor                       | Min ns                            | Max ns | Min ns                                    | Max ns  | Min ns                                    | Max ns |

| TCLCL                                  | CLK Cycle Period                | 200                               | 500    | 100                                       | 500     | 125                                       | 500    |

| TCLCH                                  | CLK Cycle Low<br>Time           | 118                               |        | 53                                        |         | 68                                        |        |

| TCHCL                                  | CLK High Time                   | 69                                |        | 39                                        |         | 44                                        |        |

| TCH1CH2                                | CLK Rise Time                   |                                   | 10     |                                           | 10      |                                           | 10     |

| TCL2CL1                                | CLK Fall Time                   |                                   | 10     |                                           | 10      |                                           | 10     |

| TDVCL(1)                               | Data in Setup Time              | 21.1                              |        | 21.1(5)                                   |         | 21.1(20)                                  |        |

| TCLDX(2)                               | Data in Hold Time               | 13.5(10)                          |        | 13.5(10)                                  |         | 13.5(10)                                  |        |

| TR1VCL(3, 4)                           | RDY Hold Time<br>into 8284A     | 35                                |        | 35                                        |         | 35                                        |        |

| TCLR1X(3, 4)                           | RDY Hold Time<br>into 8284A     | 0                                 |        | 0                                         |         | 0                                         |        |

| TRYHCH(5)                              | READY Setup<br>Time into 8086   | 44.5                              |        | 44.5                                      |         | 44.5                                      |        |

| TCHRYX(6)                              | READY Hold Time into 8086       | 20.5                              |        | 20.5(20)                                  |         | 20.5(20)                                  |        |

| TRYLCL(5)                              | READY Inactive to CLK           | -18.5                             |        | - 18.5                                    |         | 18.5                                      |        |

| THVCH(1)                               | HOLD Setup Time                 | 12.7                              |        | 12.7                                      |         | 12.7                                      |        |

| TINVCH<br>NMI(1)<br>INTR(1)<br>TEST(1) | INTR, NMI, TEST<br>Setup Time   | 50.5 +<br>TCLCH(30)<br>20<br>21.5 |        | 50.5 +<br>TCLCH(15)<br>20(15)<br>21.5(150 |         | 50.5 +<br>TCLCH(15)<br>20(15)<br>21.5(15) |        |

| TILIH                                  | Input Rise Time<br>(Except CLK) |                                   | 20     |                                           | 20      |                                           | 20     |

| TIHIL                                  | Input Fall Time<br>(Except CLK) |                                   | 12     |                                           | 12      |                                           | 12     |

Numbers followed by parentheses deviate from the 8086 chip specification; the 1985 *Microsystem Components Handbook* chip specification timing is given in the parentheses.

- 1. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 0.7 ns to the timings.

- 2. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 2.5 ns to the timings.

- 3. The signal at 8284 is for reference only.

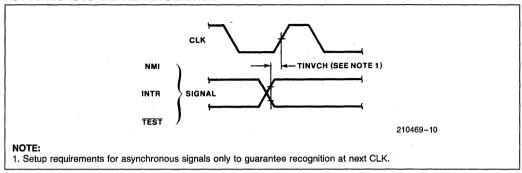

- 4. The setup requirement, for asynchronous signal is only to guarantee recognition at the next CLK.

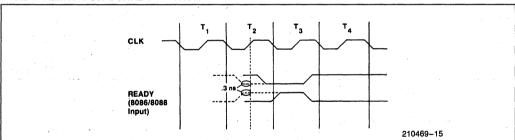

- 5. If BTHRDY = TRUE, READY must be set up 0.3 ns before the rising edge of T2.

- 6. If BTHRDY = TRUE, READY must be held 16.5 ns after the rising edge of T2.

### A.C. CHARACTERISTICS FOR THE 12ICETM SYSTEM 8086 PROBE (Continued)

**Table 5. Minimum Complexity System Timing Responses**

| Min Mode                             | Damanatas                              | 5 MHz                    | (8086)                | 10 MHz                         | (8086-1)                       | 8 MHz (8086-2)                 |                      |  |

|--------------------------------------|----------------------------------------|--------------------------|-----------------------|--------------------------------|--------------------------------|--------------------------------|----------------------|--|

| Symbol                               | Parameter                              | Min ns                   | Max ns                | Min ns                         | Max ns                         | Min ns                         | Max ns               |  |

| TCLAV(1)                             | Address Valid<br>Delay                 | 17.5                     | 64.5                  | 17.5                           | 64.5(50)                       | 17.5                           | 64.5(60)             |  |

| TCLAX(2)                             | Address Hold .<br>Time                 | 17.5                     |                       | 17.5                           |                                | 17.5                           |                      |  |

| TCLAZ(1)                             | Address Float<br>Delay                 | 14.6                     | 61.5                  | 14.6                           | 61.5(40)                       | 14.6                           | 61.5(50)             |  |

| TLHLL                                | ALE Width                              | TCLCH-17.5<br>(TCLCH-20) |                       | TCLCH-17.5                     | II                             | TCLCH-17.5                     |                      |  |

| TCLLH(1)                             | ALE Active Delay                       |                          | 42                    |                                | 42(40)                         |                                | 42                   |  |

| TCHLL(1)                             | ALE Inactive<br>Delay                  |                          | 35                    |                                | 35                             |                                | 35                   |  |

| TLLAX                                | Address Hold Time to ALE Inactive      | TCHCL-8.5                |                       | TCHCL-8.5                      |                                | TCHCL-8.5                      |                      |  |

| TCLDV(1)                             | Data Valid Delay                       | 17.5                     | 69.5                  | 17.5                           | 69.5(50)                       | 17.5                           | 69.5(60)             |  |

| TCHDX(2)                             | Data Hold Time                         | 17.5                     |                       | 17.5                           |                                | 17.5                           |                      |  |

| TWHDX                                | Data <u>Hold</u> Time<br>after WR      | TCLCH-34<br>(TCLCH-30)   |                       | TCLCH-34<br>(TCLCH-25)         | , r                            | TCLCH-34<br>(TCLCH-30)         |                      |  |

| TCVCTV<br>DEN(READ,<br>INTA)(1)      | Control Active<br>Delay <sup>(1)</sup> | 15.6                     | 63.5                  | 15.6                           | 63.5(50)                       | 15.6                           | 63.5                 |  |

| DEN(WR)(1)                           |                                        | TCHCL+15.6               | TCHCL + 63.5<br>(110) | TCHCL+15.6                     | TCHCL + 63.5<br>(50)           | TCHCL + 15.6                   | TCHCL + 63.5<br>(70) |  |

| WR(1)<br>INTA(1)                     |                                        | 16.9<br>15.9             | 59.5<br>55            | 16.9<br>15.9                   | 59.5(50)<br>55(50)             | 16.9<br>15.9                   | 59.5<br>55           |  |

| TCHCTV<br>M/IO(1, 3)<br>DT/R(1, 4)   | Control Active<br>Delay 2              | 19<br>18.4               | 77<br>73.5            | 19<br>18.4                     | 77(45)<br>73.5(45)             | 19<br>18.4                     | 77(60)<br>73.5(60)   |  |

| TCVCTX<br>DEN(1)<br>WR(1)<br>INTA(1) | Control Inactive<br>Delay              | 15.6<br>16.9<br>15.9     | 63.5<br>59.5<br>55    | 15.6<br>16.9<br>15.9           | 63.5(50)<br>59.5(50)<br>55(50) | 15.6<br>16.9<br>15.9           | 63.5<br>59.5<br>55   |  |

| TAZRL                                | Address Float<br>to READ Active        | -37.2(0)                 | , i                   | -37.2(0)                       |                                | -37.2(0)                       |                      |  |

| TCLRL(1)                             | RD Active Delay                        | 15.9                     | 80.5                  | 15.9                           | 80.5(70)                       | 15.9                           | 80.5                 |  |

| TCLRH(1)                             | RD Inactive Delay                      | 15.9                     | 70.5                  | 15.9                           | 70.5(60)                       | 15.9                           | 70.5                 |  |

| TRHAV                                | RD Inactive to<br>Next Address Active  | (Note 5)                 |                       | (Note 5)                       |                                | (Note 5)                       |                      |  |

| TCLHAV(1)                            | HLDA Valid Delay                       | 11.3                     | 57                    | 11.3                           | 57                             | 11.3                           | - 57                 |  |

| TRLRH                                | RD Width                               | 2TCLCL-52.5              |                       | 2TCLCL - 52.5<br>(2TCLCL - 40) |                                | 2TCLCL - 52.5<br>(2TCLCL - 50) |                      |  |

| TWLWH                                | WR Width                               | 2TCLCL-27.5              |                       | 2TCLCL - 27.5                  |                                | 2TCLCL - 27.5                  |                      |  |

| TAVAL                                | Address Valid<br>to ALE Low            | TCLCH-47.2               |                       | TCLCH-47.2<br>(TCLCH-35)       |                                | TCLCH-47.2<br>(TCLCH-40)       |                      |  |

| TOLOH                                | Output Rise Time                       |                          | 20                    |                                | 20                             |                                | 20                   |  |

| TOHOL .                              | Output Fall Time                       |                          | 12                    |                                | 12                             |                                | 12                   |  |

Numbers followed by parenthese deviate from the 8086 chip specification; the 1985 *Microsystem Components Handbook* chip specification timing is given in the parentheses.

- 1. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 2.5 ns to the timings.

- 2. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 0.7 ns to the timings.

- 3. When performing consecutive I/O cycles (i.e., word I/O to an odd address), the M/IO line goes high for a short time during T4. The 8086 microprocessor keeps M/IO low between consecutive I/O cycles.

- 4. When performing consecutive reads to program memory, the  $DT/\overline{R}$  line of the probe microprocessor (at the end of the user cable) goes high for a short time between reads. The 8086 microprocessor keeps  $DR/\overline{R}$  low between consecutive reads.

- 5. The address data lines are only floated during T4 when RD is active.

### A.C. CHARACTERISTICS FOR THE I<sup>2</sup>ICE<sup>TM</sup> SYSTEM 8086 PROBE (Continued)

**Table 6. Maximum Complexity System Timing Requirements**

| Min Mode                               | Doromotor                                          | 5 MHz (8                          | 3086)  | 10 MHz (8                                 | 086-1) | 8 MHz (8086-2)                            |        |

|----------------------------------------|----------------------------------------------------|-----------------------------------|--------|-------------------------------------------|--------|-------------------------------------------|--------|

| Symbol                                 | Parameter                                          | Min                               | Max ns | Min ns                                    | Max ns | Min ns                                    | Max ns |

| TCLCL                                  | CLK Cycle Period                                   | 200                               | 500    | 100                                       | 500    | 125                                       | 500    |

| TCLCH                                  | CLK Low Time                                       | 118                               |        | 60(53)                                    |        | 68                                        |        |

| TCHCL                                  | CLK High Time                                      | 69                                |        | 39                                        |        | 44                                        |        |

| TCH1CH2                                | CLK Rise Time                                      |                                   | 10     |                                           | 10     |                                           | 10     |

| TCL2CL1                                | CLK Fall Time                                      |                                   | 10     |                                           | 10     |                                           | 10     |

| TDVCL(1)                               | Data in Setup Time                                 | 21.1                              |        | 21.1(5)                                   |        | 21.1(20)                                  |        |

| TCLDX(2)                               | Data in Hold Time                                  | 13.5(10)                          |        | 13.5(10)                                  |        | 13.5(10)                                  |        |

| TR1VCL(3, 4)                           | RDY Setup Time into 8284A                          | 35                                |        | 35                                        |        | 35                                        |        |

| TCLR1X(3, 4)                           | RDY Hold Time<br>into 8284A                        | 0                                 |        | 0                                         |        | 0                                         |        |

| TRYHCH(5)                              | READY Setup Time into 8086                         | 44.5                              |        | 44.5                                      |        | 44.5                                      |        |

| TCHRYX(6)                              | READY Hold Time into 8086                          | 20.5                              |        | 20.5(20)                                  |        | 20.5(20)                                  |        |

| TRYLCL <sup>(5)</sup>                  | READY Inactive to CLK                              | <b>- 18.5</b>                     |        | -18.5                                     |        | 18.5                                      |        |

| TINVCH<br>NMI(1)<br>INTR(1)<br>TEST(1) | Setup Time for<br>Recognition (INTR,<br>NMI, TEST) | 50.5 +<br>TCLCH(30)<br>20<br>21.5 |        | 50.5 +<br>TCLCH(15)<br>20(15)<br>21.5(15) |        | 50.5 +<br>TCLCH(15)<br>20(15)<br>21.5(15) |        |

| TGVCH(1)                               | RQ/GT Setup Time                                   | 12.7                              |        | 12.7(12)                                  |        | 12.7                                      |        |

| TCHGX(2)                               | RQ Hold Time<br>into 8086                          | 16.1                              | 16.1   | ,                                         |        | 16.1                                      |        |

| TILIH                                  | Input Rise Time<br>(Except CLK)                    |                                   | 20     |                                           | 20     |                                           | 20     |

| TIHIL                                  | Input Fall Time<br>(Except CLK)                    |                                   | 12     |                                           | 12     |                                           | 12     |

Numbers followed by parentheses deviate from the 8086 chip specification; the 1985 Microsystem Components Handbook chip specification timing is given in the parentheses.

- 1. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 0.7 ns to the timings.

- 2. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 2.5 ns to the timings.

- 3. The signal at 8284 or 8288 is for reference only.

- 4. The setup requirement, for asynchronous signal is only to guarantee recognition at the next CLK.

- 5. If BTHRDY = TRUE, READY must be set up 0.3 ns before the rising edge of T2.

6. If BTHRDY = TRUE, READY must be held 16.5 ns after the rising edge of T2.

# A.C. CHARACTERISTICS FOR THE I<sup>2</sup>ICETM SYSTEM 8086 PROBE (Continued)

**Table 7. Maximum Complexity System Timing Responses**

| Min Mode        | Danamatan                             | 5 MHz (80      | 86)    | 10 MHz (80                     | 86-1)    | 8 MHz (8086-2)                 |          |

|-----------------|---------------------------------------|----------------|--------|--------------------------------|----------|--------------------------------|----------|

| Symbol          | Parameter                             | Min ns         | Max ns | Min ns                         | Max ns   | Min ns                         | Max ns   |

| TCLML(1)        | Command Active<br>Delay               | 10             | 35     | 10                             | 35       | 10                             | 35       |

| TCLMH(1)        | Command Inactive Delay                | 10             | 35     | 10                             | 35       | 10                             | 35       |

| TRYHSH(2, 3, 4) | READY Active to<br>Status Passive     |                | 37.5   |                                | 37.5     |                                | 37.5     |

| TCHSV(4)        | Status Active Delay                   | 17             | 66.5   | 17                             | 66.5(45) | 17                             | 66.5(60) |

| TCLSH(4)        | Status Inactive Delay                 | 10.5           | 42.5   | 10.5                           | 42.5     | 10.5                           | 42.5     |

| TCLAV(4)        | Address Valid Delay                   | 17.5           | 64.5   | 17.5                           | 64.5(50) | 17.5                           | 64.5(60) |

| TCLAX(5)        | Address Hold Time                     | 17.5(10)       |        | 17.5(10)                       |          | 17.5(10)                       |          |

| TCLAZ(4)        | Address Float Delay                   | 14.6           | 61.5   | 14.6                           | 61.5(40) | 14.6                           | 61.5(50) |

| TSVLH(1)        | Status Valid to ALE<br>High           |                | 15     |                                | 15       |                                | 15       |

| TSVMCH(1)       | Status Valid to<br>MCE High           |                | 15     |                                | 15       |                                | 15       |

| TCLLH(1)        | CLK Low to ALE<br>Valid               |                | 15     |                                | 15       |                                | 15       |

| TCLMCH(1)       | CLK Low to MCE<br>High                |                | 15     |                                | 15       |                                | 15       |

| TCHLL(1)        | ALE Inactive Delay                    |                | 15     |                                | 15       |                                | 15       |

| TCLMCL(1)       | MCE Inactive Delay                    |                | 15     |                                | 15       |                                | 15       |

| TCLDV(4)        | Data Valid Delay                      | 17.5           | 69.5   | 17.5                           | 69.5(50) | 17.5                           | 69.5(60) |

| TCHDX(5)        | Data Hold Time                        | 17.5           | ;      | 17.5                           |          | 17.5                           |          |

| TCVNV(1)        | Control Active Delay                  | 5              | 45     | 5                              | 45       | 5                              | 45       |

| TCVNX(1)        | Control Inactive Delay                | 10             | 45     | 10                             | 45       | 10                             | 45       |

| TAZRL           | Address Float to<br>Read Active       | -37.2(0)       |        | -37.2(0)                       |          | -37.2(0)                       |          |

| TCLRL(4)        | RD Active Delay                       | 15.9           | 80.5   | 15.9                           | 80.5(70) | 15.9                           | 80.5     |

| TCLRH(4)        | RD Inactive Delay                     | 15.9           | 70.5   | 15.9                           | 70.5(60) | 15.9                           | 70.5     |

| TRHAV           | RD Inactive to<br>Next Address Active | (Note 6)       | -      | (Note 6)                       |          | (Note 6)                       |          |

| TCHDTL(1)       | Direction Control<br>Active Delay     | and the second | 50     | (A)                            | 50       |                                | 50       |

| TCHDTH(1)       | Direction Control<br>Inactive Delay   |                | 30     |                                | 30       |                                | 30       |

| TCLGL(4)        | GT Active Delay                       | 12.9           | 54.5   | 12.9                           | 54.5(45) | 12.9                           | 54.5(50) |

| TCLGH(4)        | GT Inactive Delay                     | 14.9           | 65     | 14.9                           | 65(45)   | 14.9                           | 65(50)   |

| TRLRH           | RD Width                              | 2TCLCL - 52.5  |        | 2TCLCL - 52.5<br>(2TCLCL - 40) |          | 2TCLCL - 52.5<br>(2TCLCL - 50) |          |

| TOLOH           | Output Rise Time                      |                | 20     |                                | 20       |                                | 20       |

| TOHOL           | Output Fall Time                      |                | 12     |                                | 12       |                                | 12       |

Numbers followed by parentheses deviate from the 8088 chip specification; the 1985 *Microsystem Components Handbook* chip specification timing is given in the parentheses.

- 1. The signal at 8284 or 8288 is for reference only.

- 2. If BTHRDY = TRUE, READY must be set up 0.3 ns before the rising edge of T2.

- 3. For BTHRDY = TRUE, TRYHSH = TRYHCH + 47.

- 4. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 2.5 ns to the timings.

- 5. Timings are calculated with a 74F244 as the buffer for CLOCK or READY. If a 74S244 is used, add 0.7 ns to the timings.

- 6. The address data lines are only floated during T4 when RD is active.

### A.C. CHARACTERISTICS FOR THE 12ICETM SYSTEM 8088 PROBE

Tables 8 through 11 provide timing information for the 8088 probe. Figures 5 through 12 define the timing symbols.

**Table 8. Minimum Complexity System Timing Requirements**

| Min Mode                               | Dava-markan.                  | 5 MHz (8                          | (880   | 8 MHz (80                                 | )88-1) |

|----------------------------------------|-------------------------------|-----------------------------------|--------|-------------------------------------------|--------|

| Symbol                                 | Parameter                     | Min ns                            | Max ns | Min ns                                    | Max ns |

| TCLCL                                  | CLK Cycle Period              | 200                               | 500    | 125                                       | 500    |

| TCLCH                                  | CLK Low Time                  | 118                               | 4. 1   | 68                                        |        |

| TCHCL                                  | CLK High Time                 | 69                                |        | 44                                        |        |

| TCH1CH2                                | CLK Rise Time                 |                                   | 10     |                                           | 10     |

| TCL2CL1                                | CLK Fall Time                 |                                   | 10     | -                                         | 10     |

| TDVCL(1)                               | Data in Setup Time            | 21.1                              |        | 21.1(20)                                  |        |

| TCLDX(2)                               | Data in Hold Time             | 13.5(10)                          | :      | 13.5(10)                                  |        |

| TR1VCL(3, 4)                           | RDY Setup Time<br>into 8284   | 35                                |        | 35                                        |        |

| TCLR1X(3, 4)                           | RDY Hold Time<br>into 8284    | 0                                 |        | 0                                         |        |

| TRYHCH(5)                              | READY Setup Time into 8088    | 57.8                              | -      | 57.8                                      |        |

| TCHRYX(6)                              | READY Hold Time<br>into 8088  | 20.5                              |        | 20.5(20)                                  |        |

| TRYLCL(5)                              | READY Inactive to CLK         | - 16.5                            |        | - 16.5                                    |        |

| THVCH(1)                               | Hold Setup Time               | 12.7                              | -      | 12.7                                      |        |

| TINVCH<br>NMI(1)<br>INTR(1)<br>TEST(1) | INTR, NMI, TEST<br>Setup Time | 50.5 +<br>TCLCH(30)<br>26<br>27.5 |        | 50.5 +<br>TCLCH(15)<br>26(15)<br>27.5(15) |        |

| TILIH                                  | Input Rise Time               |                                   | 20     |                                           | 20     |

| TIHIL                                  | Input Fall Time               |                                   | 12     | ur i                                      | 12     |