# M80C86/M80C86-2 16-BIT CHMOS MICROPROCESSOR

**MILITARY**

- Pin-for-Pin and Functionally Compatible to Industry Standard HMOS M8086

- Fully Static Design with Frequency Range from D.C. to:

- 5 MHz for M80C86

- -8 MHz for M80C86-2

- **Low Power Operation**

- Operating I<sub>CC</sub> = 10 mA/MHz

- Standby  $I_{CCS} = 500 \mu A \text{ max}$

- Bus-Hold Circuitry Eliminates Pull-Up Resistors

- Direct Addressing Capability of 1 MByte of Memory

- Architecture Designed for Powerful Assembly Language and Efficient High Level Languages

- 24 Operand Addressing Modes

- Byte, Word and Block Operations

- 8 and 16-Bit Signed and Unsigned Arithmetic

- Binary or Decimal

- Multiply and Divide

- Military Temperature Range:

- $-55^{\circ}$ C to  $+125^{\circ}$ C (T<sub>C</sub>)

The Intel M80C86 is a high performance, CHMOS version of the industry standard HMOS M8086 16-bit CPU. It is available in 5 and 8 MHz clock rates. The M80C86 offers two modes of operation: MINimum for small systems and MAXimum for larger applications such as multiprocessing. It is available in 40-pin DIP package.

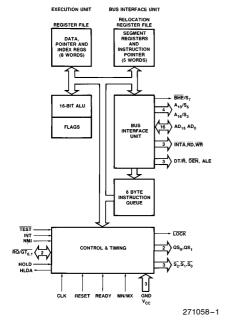

Figure 1. M80C86 CPU Block Diagram

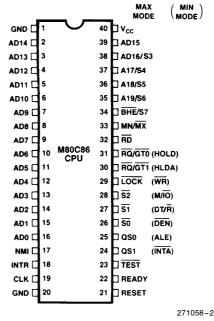

Figure 2. M80C86 40-Lead DIP Configuration

November 1989 Order Number: 271058-005

#### **Table 1. Pin Description**

The following pin function descriptions are for M80C86 systems in either minimum or maximum mode. The "Local Bus" in these descriptions is the direct multiplexed bus interface connection to the M80C86 (without regard to additional bus buffers).

| Symbol                                                                                                                                         | Pin No.  | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Name and                        | Function                                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------|--|--|--|

| AD <sub>15</sub> –AD <sub>0</sub>                                                                                                              | 2-16, 39 | 1/0  | ADDRESS DATA BUS: These lines constitute the time multiplexed memory/IO address (T <sub>1</sub> ) and data (T <sub>2</sub> , T <sub>3</sub> , T <sub>W</sub> , T <sub>4</sub> ) bus. A <sub>0</sub> is analogous to $\overline{BHE}$ for the lower byte of the data bus, pins D <sub>7</sub> –D <sub>0</sub> . It is LOW during T <sub>1</sub> when a byte is to be transferred on the lower portion of the bus in memory or I/O operations. Eight-bit oriented devices tied to the lower half would normally use A <sub>0</sub> to condition chip select functions. (See $\overline{BHE}$ .) These lines are active HIGH and float to 3-state OFF <sup>(1)</sup> during interrupt acknowledge and local bus "hold acknowledge."       |                                 |                                                 |  |  |  |

| A <sub>19</sub> /S <sub>6</sub> ,<br>A <sub>18</sub> /S <sub>5</sub> ,<br>A <sub>17</sub> /S <sub>4</sub> ,<br>A <sub>16</sub> /S <sub>3</sub> | 35–38    | 0    | <b>ADDRESS/STATUS:</b> During T <sub>1</sub> these are the four most significant address lines for memory operations. During I/O operations these lines are LOW. During memory and I/O operations, status information is available on these lines during T <sub>2</sub> , T <sub>3</sub> , T <sub>W</sub> , and T <sub>4</sub> . The status of the interrupt enable FLAG bit (S <sub>5</sub> ) is updated at the beginning of each CLK cycle. $A_{17}/S_4$ and $A_{16}/S_3$ are encoded as shown.                                                                                                                                                                                                                                      |                                 |                                                 |  |  |  |

|                                                                                                                                                |          |      | This information in<br>being used for dat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | location register is presently                  |  |  |  |

|                                                                                                                                                |          |      | These lines float to acknowledge."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | o 3-state OFF(1)                | during local bus "hold                          |  |  |  |

|                                                                                                                                                |          |      | A <sub>17</sub> /S <sub>4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A <sub>16</sub> /S <sub>3</sub> | Characteristics                                 |  |  |  |

|                                                                                                                                                |          |      | 0 (LOW)<br>0<br>1 (HIGH)<br>1<br>S <sub>6</sub> is 0<br>(LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0<br>1<br>0<br>1                | Alternate Data<br>Stack<br>Code or None<br>Data |  |  |  |

| BHE/S <sub>7</sub>                                                                                                                             | 34       | 0    | BUS HIGH ENABLE/STATUS: During T <sub>1</sub> the bus high enable sign (BHE) should be used to enable data onto the most significant hal of the data bus, pins D <sub>15</sub> -D <sub>8</sub> . Eight-bit oriented devices tied to the upper half of the bus would normally use BHE to condition chip select functions. BHE is LOW during T <sub>1</sub> for read, write, and interrul acknowledge cycles when a byte is to be transferred on the high portion of the bus. The S <sub>7</sub> status information is available during T <sub>2</sub> T <sub>3</sub> , and T <sub>4</sub> . The signal is active LOW, and floats to 3-state OFF(1) inhold." It is LOW during T <sub>1</sub> for the first interrupt acknowledge cycles. |                                 |                                                 |  |  |  |

|                                                                                                                                                |          |      | BHE A <sub>0</sub> Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |                                                 |  |  |  |

|                                                                                                                                                |          |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0<br>1                          | Whole word Upper byte from/ to odd address      |  |  |  |

|                                                                                                                                                |          |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                               | Lower byte from/<br>to even address             |  |  |  |

|                                                                                                                                                |          |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                               | None                                            |  |  |  |

Table 1. Pin Description (Continued)

| Symbol          | Pin No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD              | 32      | 0    | <b>READ:</b> Read strobe indicates that the processor is performing a memory of I/O read cycle, depending on the state of the $S_2$ pin. This signal is used to read devices which reside on the M80C86 local bus. $\overline{\text{RD}}$ is active LOW during $T_2$ , $T_3$ and $T_W$ of any read cycle, and is guaranteed to remain HIGH in $T_2$ until the M80C86 local bus has floated.                                            |

|                 |         |      | This floats to 3-state OFF in "hold acknowledge."                                                                                                                                                                                                                                                                                                                                                                                      |

| READY           | 22      | I    | <b>READY:</b> is the acknowledgement from the addressed memory or I/O device that it will complete the data transfer. The READY signal from memory/IO is synchronized by the M82C84A Clock Generator to form READY. This signal is active HIGH. The M80C86 READY input is not synchronized. Correct operation is not guaranteed if the setup and hold times are not met.                                                               |

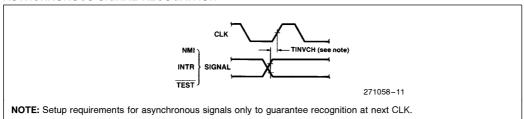

| INTR            | 18      | I    | INTERRUPT REQUEST: is a level triggered input which is sampled during the last clock cycle of each instruction to determine if the processor should enter into an interrupt acknowledge operation. A subroutine is vectored to via an interrupt vector lookup table located in system memory. It can be internally masked by software resetting the interrupt enable bit. INTR is internally synchronized. This signal is active HIGH. |

| TEST            | 23      | I    | <b>TEST:</b> input is examined by the "Wait" instruction. If the TEST input is LOW execution continues, otherwise the processor waits in an "Idle" state. This input is synchronized internally during each clock cycle on the leading edge of CLK.                                                                                                                                                                                    |

| NMI             | 17      | ı    | NON-MASKABLE INTERRUPT: an edge triggered input which causes a type 2 interrupt. A subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is not maskable internally by software. A transition from a LOW to HIGH initiates the interrupt at the end of the current instruction. This input is internally synchronized.                                                                          |

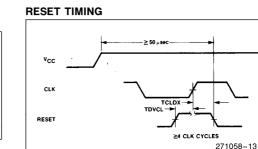

| RESET           | 21      | I    | <b>RESET:</b> causes the processor to immediately terminate its present activity. The signal must be active HIGH for at least four clock cycles. It restarts execution, as described in the Instruction Set description, when RESET returns LOW. RESET is internally synchronized.                                                                                                                                                     |

| CLK             | 19      | I    | <b>CLOCK:</b> provides the basic timing for the processor and bus controller. It is asymmetric with a 33% duty cycle to provide optimized internal timing.                                                                                                                                                                                                                                                                             |

| V <sub>CC</sub> | 40      |      | V <sub>CC</sub> : +5V power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                |

| GND             | 1, 20   |      | GROUND: Both must be connected.                                                                                                                                                                                                                                                                                                                                                                                                        |

| MN/MX           | 33      | I    | MINIMUM/MAXIMUM: indicates what mode the processor is to operate in. The two modes are discussed in the following sections.                                                                                                                                                                                                                                                                                                            |

#### Table 1. Pin Description (Continued)

The following pin function descriptions are for the M80C86/M82C88 system in maximum mode (i.e.,  $MN/\overline{MX} = V_{SS}$ ). Only the pin functions which are unique to maximum mode are described; all other pin functions are as described above.

| Symbol                                           | Pin No. | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ame and F                                                                                                                                                                                                                                      | unction                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------------------------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

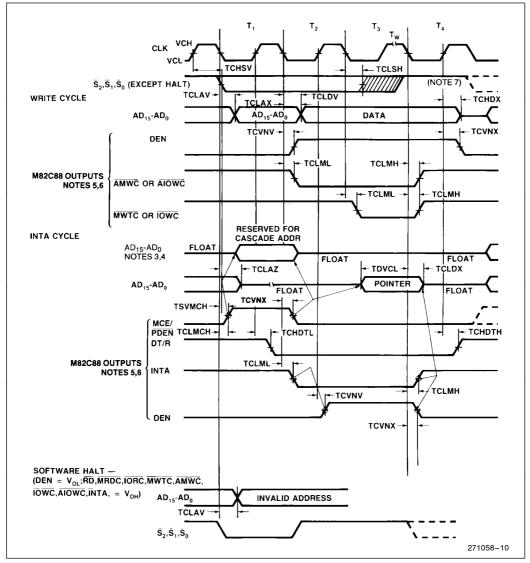

| $\overline{S_2}, \overline{S_1}, \overline{S_0}$ | 26–28   | 0    | <b>STATUS:</b> active during $T_4$ , $T_1$ , and $T_2$ and is returned to the passive state (1,1,1) during $T_3$ or during $T_W$ when READY is HIGH. This status is used by the M82C88 Bus Controller to generate all memory and I/O access control signals. Any change by $\overline{S_2}$ , $\overline{S_1}$ , $\overline{S_0}$ during $T_4$ is used to indicate the beginning of a bus cycle, and the return to the passive state in $T_3$ or $T_W$ is used to indicate the end of a bus cycle. These signals float to 3-state OFF <sup>(1)</sup> in "hold acknowledge." These status lines are encoded as shown. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                  |         |      | S <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | S <sub>0</sub>                                                                                                                                                                                                                                 | Characteristics                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                  |         |      | 0 (LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                              | Interrupt<br>Acknowledge                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                                                  |         |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                              | Read I/O Port                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                  |         |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                              | Write I/O Port                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                  |         |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                              | Halt                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                  |         |      | 1 (HIGH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                              | Code Access                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                                  |         |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                              | Read Memory                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                                  |         |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                              | Write Memory                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

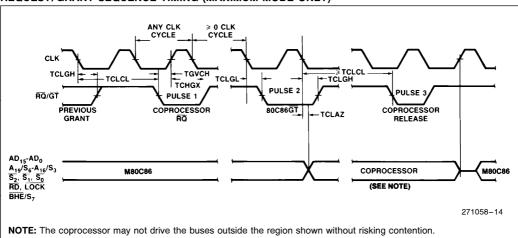

| RQ/GT <sub>0.</sub>                              |         |      | 1 1 1 Passive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RQ/GT <sub>1</sub>                               |         |      | processor's cur having higher p resistor so may as follows (see 1. A pulse of 1 (local bus reque 2. During a T <sub>4</sub> c M80C86 to the M80C86 has all "hold acknowled unit is disconne acknowledge." 3. A pulse 1 CL M80C86 (pulse M80C86 can re Each master-m pulses. There in Pulses are activity if the request is will release the conditions are in 1. Request occi 2. Current cycles.                                                                                                                                                                                                                     | rent bus cyriority than be left und timing diagonal continuity of T <sub>1</sub> clock requesting lowed the leader" states and the leader" states at the claim the leader with the leader while local bus of the leader on the | ycle. Each   RQ/GT <sub>1</sub> . is connected. gram): rom another to the M80 cycle, a pure master (procal bus to eat the nexually from the manage of the edead CLK during T <sub>4</sub> of efore T <sub>2</sub> . low byte of first acknown. | lse 1 ČLK wide from the ulse 2), indicates that the of loat and that it will enter the t CLK. The CPU's bus interface to local bus during "hold esting master indicates to the quest is about to end and that the next CLK.  I local bus is a sequence of 3 (cycle after each bus exchange.)  It is performing a memory cycle, it is the cycle when all the following is a word (on an odd address). |  |  |  |

Table 1. Pin Description (Continued)

| Symbol                            | Pin No. | Туре |                                                                                                                                                                                                                                                                                                                                        | Name an         | d Function                       |  |  |  |

|-----------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|--|--|--|

|                                   |         |      | If the local bus is idle when the request is made the two possible events will follow:                                                                                                                                                                                                                                                 |                 |                                  |  |  |  |

|                                   |         |      | Local bus will be released during the next clock.     A memory cycle will start within 3 clocks. Now the four rules for a currently active memory cycle apply with condition number 1 already satisfied.                                                                                                                               |                 |                                  |  |  |  |

| LOCK                              | 29      | 0    | LOCK: output indicates that other system bus masters are not to gain control of the system bus while LOCK is active LOW. The LOCK signal is activated by the "LOCK" prefix instruction and remains active until the completion of the next instruction. This signal is active LOW, and floats to 3-state OFF(1) in "hold acknowledge." |                 |                                  |  |  |  |

| QS <sub>1</sub> , QS <sub>0</sub> | 24, 25  | 0    | QUEUE STATUS: The queue status is valid during the CLK cycle after which the queue operation is performed. QS <sub>1</sub> and QS <sub>0</sub> provide status to allow external tracking of the internal M80C86 instruction queue.                                                                                                     |                 |                                  |  |  |  |

|                                   |         |      | QS <sub>1</sub>                                                                                                                                                                                                                                                                                                                        | QS <sub>0</sub> | Characteristics                  |  |  |  |

|                                   |         |      | 0 (LOW)                                                                                                                                                                                                                                                                                                                                | 0               | No Operation                     |  |  |  |

|                                   |         |      | 0                                                                                                                                                                                                                                                                                                                                      | 1               | First Byte of Op Code from Queue |  |  |  |

|                                   |         |      | 1 (HIGH)                                                                                                                                                                                                                                                                                                                               | 0               | Empty the Queue                  |  |  |  |

|                                   |         |      | 1                                                                                                                                                                                                                                                                                                                                      | 1               | Subsequent Byte from Queue       |  |  |  |

The following pin function descriptions are for the M80C86 in minimum mode (i.e.,  $MN/\overline{MX} = V_{CC}$ ). Only the pin functions which are unique to minimum mode are described; all other pin functions are described above.

| M/ĪŌ | 28 | 0 | <b>STATUS LINE:</b> logically equivalent to $S_2$ in the maximum mode. It is used to distinguish a memory access from an I/O access. M/ $\overline{\text{IO}}$ becomes valid in the $T_4$ preceding a bus cycle and remains valid until the final $T_4$ of the cycle (M=HIGH, IO=LOW). M/ $\overline{\text{IO}}$ floats to 3-state OFF <sup>(1)</sup> in local bus "hold acknowledge."                           |

|------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WR   | 29 | 0 | <b>WRITE:</b> indicates that the processor is performing a write memory or write I/O cycle, depending on the state of the M/ $\overline{\text{IO}}$ signal. $\overline{\text{WR}}$ is active for T <sub>2</sub> , T <sub>3</sub> and T <sub>W</sub> of any write cycle. It is active LOW, and floats to 3-state OFF <sup>(1)</sup> in local bus "hold acknowledge."                                              |

| ĪNTĀ | 24 | 0 | $\overline{\text{INTA}}$ is used as a read strobe for interrupt acknowledge cycles. It is active LOW during T <sub>2</sub> , T <sub>3</sub> and T <sub>W</sub> of each interrupt acknowledge cycle.                                                                                                                                                                                                              |

| ALE  | 25 | 0 | ADDRESS LATCH ENABLE: provided by the processor to latch the address into an address latch. It is a HIGH pulse active during T <sub>1</sub> of any bus cycle. Note that ALE is never floated.                                                                                                                                                                                                                    |

| DT/R | 27 | 0 | <b>DATA TRANSMIT/RECEIVE:</b> needed in minimum system that desires to use a data bus transceiver. It is used to control the direction of data flow through the transceiver. Logically $DT/\overline{R}$ is equivalent to $\overline{S_1}$ in the maximum mode, and its timing is the same as for $M/\overline{IO}$ . (T = HIGH, R = LOW.) This signal floats to 3-state OFF(1) in local bus "hold acknowledge." |

Table 1. Pin Description (Continued)

| Symbol        | Pin No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEN           | 26      | 0    | <b>DATA ENABLE:</b> provided as an output enable for the transceiver in a minimum system which uses the transceiver. $\overline{DEN}$ is active LOW during each memory and I/O access and for INTA cycles. For a read or $\overline{INTA}$ cycle it is active from the middle of $T_2$ until the middle of $T_4$ , while for a write cycle it is active from the beginning of $T_2$ until the middle of $T_4$ . $\overline{DEN}$ floats to 3-state OFF(1) in local bus "hold acknowledge."                                                                                                                                                                                                                                                                                                     |

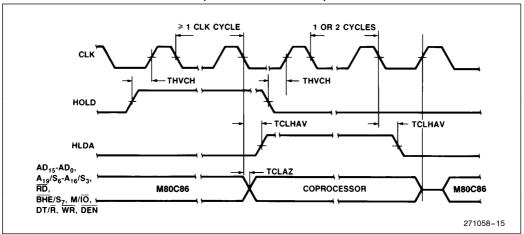

| HOLD,<br>HLDA | 31, 30  | 1/0  | HOLD: indicates that another master is requesting a local bus "hold." To be acknowledged, HOLD must be active HIGH. The processor receiving the "hold" request will issue HLDA (HIGH) as an acknowledgement in the middle of a T <sub>1</sub> clock cycle. Simultaneous with the issuance of HLDA the processor will float the local bus and control lines. After HOLD is detected as being LOW, the processor will LOWer the HLDA, and when the processor needs to run another cycle, it will again drive the local bus and control lines. The same rules as for \$\overline{RQ}/\overline{GT}\$ apply regarding when the local bus will be released. HOLD is not an asynchronous input. External synchronization should be provided if the system cannot otherwise guarantee the setup time. |

#### NOTE:

1. See the section on Bus Hold Circuitry.

#### **FUNCTIONAL DESCRIPTION**

#### STATIC OPERATION

All M80C86 circuitry is of static design. Internal registers, counters and latches are static and require no refresh as with dynamic circuit design. This eliminates the minimum operating frequency restriction placed on other microprocessors. The CMOS M80C86 can operate from DC to the appropriate upper frequency limit. The processor clock may be stopped in either state (high/low) and held there indefinitely. This type of operation is especially useful for system debug or power critical applications.

The M80C86 can be single stepped using only the CPU clock. This state can be maintained as long as is necessary. Single step clock operation allows simple interface circuitry to provide critical information for bringing up your system.

Static design also allows very low frequency operation. In a power critical situation, this can provide extremely low power operation since M80C86 power dissipation is directly related to operating frequency. As the system frequency is reduced, so is the operating power until, ultimately, at a DC input frequency, the M80C86 power requirement is the standby current.

#### INTERNAL ARCHITECTURE

The internal functions of the M80C86 processor are partitioned logically into two processing units. The first is the Bus Interface Unit (BIU) and the second is the Execution Unit (EU) as shown in the block diagram of Figure 1.

These units can interact directly but for the most part perform as separate asynchronous operational processors. The bus interface unit provides the functions related to instruction fetching and queuing, operand fetch and store, and address relocation. This unit also provides the basic bus control. The overlap of instruction pre-fetching provided by this unit serves to increase processor performance through improved bus bandwidth utilization. Up to 6 bytes of the instruction stream can be queued while waiting for decoding and execution.

The instruction stream queuing mechanism allows the BIU to keep the memory utilized very efficiently. Whenever there is space for at least 2 bytes in the queue, the BIU will attempt a word fetch memory cycle. This greatly reduces "dead time" on the memory bus. The queue acts as a First-In-First Out (FIFO) buffer, from which the EU extracts instruction bytes as required. If the queue is empty (following a branch instruction, for example), the first byte into the queue immediately becomes available to the EU.

The execution units receives pre-fetched instructions from the BIU queue and provides un-relocated operand addresses to the BIU. Memory operands are passed through the BIU for processing by the EU, which passes results to the BIU for storage. See the Instruction Set description for further register set and architectural descriptions.

#### NOTE:

Additional information on memory organization, requirements for supporting minimum and maximum modes, bus operation, basic system timing, and external interface of the M80C86 is described in the Microsystems Components Handbook.

#### **DEVIATION DESCRIPTION**

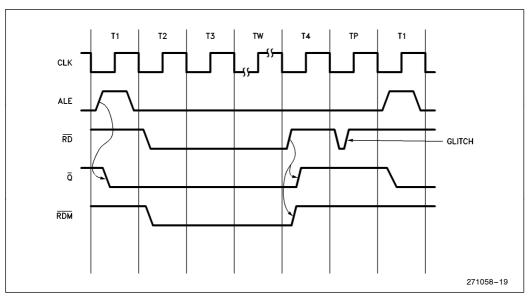

A 20-25 ns glitch occurs on the 80C86/80C88 RD pin immediately following a read cycle. The problem has been fully characterized with the following results:

- The read cycle must be 4 clocks followed by 2 passive clocks.

- Cycle following the read cycle must be a data read/write or an I/O read/write.

- 3. The # of bytes in the queue required to cause the glitch varies by instruction.

- 4. The glitch appears on the falling edge of the first passive clock.

- 5. The magnitude of the glitch depends on the capacitive loading of the RD# pin.

- The glitch occurs for both Min and Max mode operations.

- 7. V<sub>CC</sub> variations from 4.5V through 5.5V have no effect on the glitch.

- 8. Temperature variations (within allowed temperature range) also have no effect on the glitch.

#### **IMPACT ON SYSTEM DESIGN**

Systems which use the  $\overline{\text{RD}}$  strobe to clock a state machine or any other edge triggered device are most vulnerable and most likely to malfunction.

The problem may also impact other Min mode systems, particularly those in which the system address latches are enabled all the time (such as the example minimum mode system illustrated in the 80C86 data sheet). In such designs, the RD signal is used to turn off the output buffers of the memory and peripheral devices connected to the local bus at the end of a bus cycle. A false pulse on the RD pin in a TP or a T1 state following a read cycle may not allow for sufficient recovery time for a previously accessed device. The probability of a failure is higher for low speed designs using slow memory and peripheral devices which require high recovery times between successive accesses. The problem will not be seen if the address latches are disabled at the end of any bus cycle since all the devices connected to the bus will then be deselected when the false pulse occurs.

Most Max mode systems do not use the  $\overline{\text{RD}}$  signal and are therefore not likely to be affected.

#### **WORKAROUND**

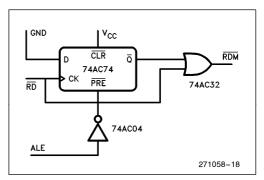

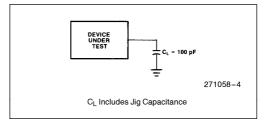

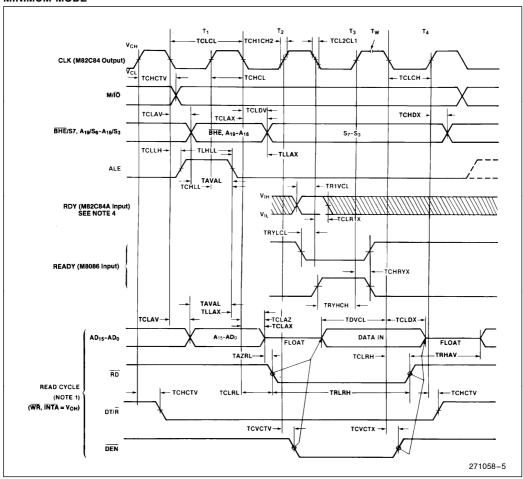

A hardware workaround has been designed and tested. The workaround circuit (Figure 3) qualifies the  $\overline{\text{RD}}$  signal coming out of the M80C86/80C88 during valid read cycles and forces it to be inactive otherwise (see the timing diagram in Figure 4). The-delay in the  $\overline{\text{RDM}}$  signal is limited to 6 ns (Max) by using fast gate devices. This should not have any impact in the design since the  $\overline{\text{RDM}}$  pulse width is still the same as the orginal  $\overline{\text{RD}}$  pulse width.  $\overline{\text{RDM}}$  is also guaranteed to go inactive during the T4 state of all read cycles.

Figure 3

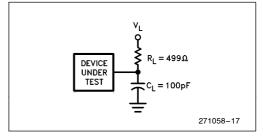

Figure 4

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage (With respect to ground)0.5 to 8.0V                  |

|---------------------------------------------------------------------|