PRELIMINARY

#### intal Intel386™ DX MICROPROCESSOR 32-BIT CHMOS MICROPROCESSOR WITH INTEGRATED MEMORY MANAGEMENT (PQFP SUPPLEMENT)

- Flexible 32-Bit Microprocessor - 8, 16, 32-Bit Data Types - 8 General Purpose 32-Bit Registers

- Very Large Address Space

- 4 Gigabyte Physical

- 64 Terabyte Virtual

- 4 Gigabyte Maximum Segment Size

- Integrated Memory Management Unit

- Virtual Memory Support

Optional On-Chip Paging

- 4 Levels of Protection - Fully Compatible with 80286

- Object Code Compatible with All 8086 **Family Microprocessors**

- Virtual 8086 Mode Allows Running of 8086 Software in a Protected and Paged System

- Hardware Debugging Support

- Optimized for System Performance

- Pipelined Instruction Execution

- On-Chip Address Translation Caches

- 20, 25 and 33 MHz Clock

- 40, 50 and 66 Megabytes/Sec Bus **Bandwidth**

- Numerics Support via Intel387<sup>TM</sup> DX Math Coprocessor

- Complete System Development Support

- Software: C, PL/M, Assembler System Generation Tools - Debuggers: PSCOPE, ICE™-386

- High Speed CHMOS IV Technology

- 132 Pin PQFP Package

(See Packaging Specification, Order #231369)

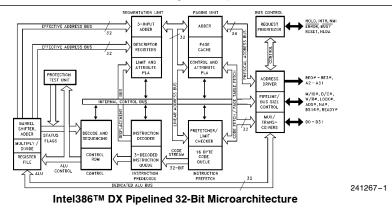

The Intel386 DX Microprocessor is an entry-level 32-bit microprocessor designed for single-user applications and operating systems such as MS-DOS and Windows. The 32-bit registers and data paths support 32-bit addresses and data types. The processor addresses up to four gigabytes of physical memory and 64 terabytes (2\*\*46) of virtual memory. The integrated memory management and protection architecture includes address translation registers, multitasking hardware and a protection mechanism to support operating systems. Instruction pipelining, on-chip address translation, ensure short average instruction execution times and maximum system throughput.

The Intel386 DX CPU offers new testability and debugging features. Testability features include a self-test and direct access to the page translation cache. Four new breakpoint registers provide breakpoint traps on code execution or data accesses, for powerful debugging of even ROM-based systems.

Object-code compatibility with all 8086 family members (8086, 8088, 80186, 80188, 80286) means the Intel386 DX offers immediate access to the world's largest microprocessor software base.

Intel386™ DX and Intel387™ DX are Trademarks of Intel Corporation. MS-DOS and Windows are Trademarks of MICROSOFT Corporation.

\*Other brands and names are the property of their respective owners. Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata. COPYRIGHT © INTEL CORPORATION, 1995 January 1994 Order Number: 241267-003

### Intel386<sup>™</sup> DX Microprocessor High-Performance 32-Bit CHMOS Microprocessor with Integrated Memory Management (PQFP Supplement)

| <b>CONTENTS</b> PAGE                  | CONTENTS PAGE                        |

|---------------------------------------|--------------------------------------|

| 1.0 PIN ASSIGNMENT                    | 3.0 D.C./A.C. SPECIFICATIONS 12      |

| 1.1 Pin Description Table5            | 3.1 D.C. Specifications              |

| 1.2 Float Pin Description7            | 3.2 A.C. Specifications              |

| 2.0 MECHANICAL DATA                   | 3.2.1 A.C. Spec Definitions 13       |

| 2.1 Package Physical Dimensions 8     | 3.2.2 A.C. Specification Tables 14   |

| 2.2 Package Thermal Specifications 11 | 3.2.3 A.C. Test Loads                |

|                                       | 3.2.4 A.C. Timing Waveforms 20       |

|                                       | 3.2.5 Typical Output Valid Delays 22 |

|                                       | 3.2.6 Typical Output Valid Delays 22 |

|                                       | 3.2.7 Typical Output Valid Delays 23 |

|                                       | 3.2.8 Typical Output Rise Times 23   |

This document should be used in conjunction with the Intel386™ DX Microprocessor data sheet (order number 231630-011, October 1993).

#### 1.0 PIN ASSIGNMENT

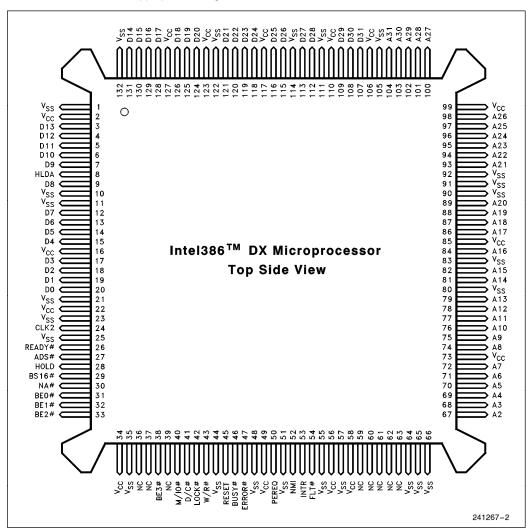

The Intel386 DX pinout as viewed from the top side of the component is shown by Figure 1-1.

$V_{CC}$  and GND connections must be made to multiple  $V_{CC}$  and  $V_{SS}$  (GND) pins. Each  $V_{CC}$  and  $V_{SS}$  must be connected to the appropriate voltage level.

Intel386TM DX PQFP MICROPROCESSOR

The circuit board should include V<sub>CC</sub> and GND planes for power distribution and all V<sub>CC</sub> and V<sub>SS</sub> pins must be connected to the appropriate plane.

NOTE:

Pins identified as "N.C." should remain completely unconnected.

Figure 1-1. Intel386™ DX PQFP Pinout—View from Top Side

| Add | ress | Da  | ata | Contro  |    | N/C | V <sub>SS</sub> | V <sub>CC</sub> |

|-----|------|-----|-----|---------|----|-----|-----------------|-----------------|

| A2  | 67   | D0  | 20  | ADS#    | 27 | 36  | 1               | 2               |

| A3  | 68   | D1  | 19  | BE0#    | 31 | 37  | 10              | 16              |

| A4  | 69   | D2  | 18  | BE1#    | 32 | 39  | 11              | 22              |

| A5  | 70   | D3  | 17  | BE2#    | 33 | 59  | 21              | 34              |

| A6  | 71   | D4  | 15  | BE3#    | 38 | 60  | 23              | 49              |

| A7  | 72   | D5  | 14  | BS16#   | 29 | 61  | 25              | 56              |

| A8  | 74   | D6  | 13  | BUSY#   | 46 | 62  | 35              | 58              |

| A9  | 75   | D7  | 12  | CLK2    | 24 | 63  | 44              | 73              |

| A10 | 76   | D8  | 9   | D/C#    | 41 |     | 48              | 85              |

| A11 | 77   | D9  | 7   | ERROR # | 47 |     | 51              | 99              |

| A12 | 78   | D10 | 6   | FLT#    | 54 |     | 55              | 106             |

| A13 | 79   | D11 | 5   | HLDA    | 8  |     | 57              | 110             |

| A14 | 81   | D12 | 4   | HOLD    | 28 |     | 64              | 117             |

| A15 | 82   | D13 | 3   | INTR    | 53 |     | 65              | 123             |

| A16 | 84   | D14 | 131 | LOCK#   | 42 |     | 66              | 127             |

| A17 | 86   | D15 | 130 | M/IO#   | 40 |     | 80              |                 |

| A18 | 87   | D16 | 129 | NA#     | 30 |     | 83              |                 |

| A19 | 88   | D17 | 128 | NMI     | 52 |     | 90              |                 |

| A20 | 89   | D18 | 126 | PEREQ   | 50 |     | 91              |                 |

| A21 | 93   | D19 | 125 | READY#  | 26 |     | 92              |                 |

| A22 | 94   | D20 | 124 | RESET   | 45 |     | 105             |                 |

| A23 | 95   | D21 | 121 | W/R#    | 43 |     | 111             |                 |

| A24 | 96   | D22 | 120 |         |    |     | 114             |                 |

| A25 | 97   | D23 | 119 |         |    |     | 122             |                 |

| A26 | 98   | D24 | 118 |         |    |     | 132             |                 |

| A27 | 100  | D25 | 116 |         |    |     |                 |                 |

| A28 | 101  | D26 | 115 |         |    |     |                 |                 |

| A29 | 102  | D27 | 113 |         |    |     |                 |                 |

| A30 | 103  | D28 | 112 |         |    |     |                 |                 |

| A31 | 104  | D29 | 109 |         |    |     |                 |                 |

|     |      | D30 | 108 |         |    |     |                 |                 |

|     |      | D31 | 107 |         |    |     |                 |                 |

Table 1-1. Intel386™ DX PQFP Pinout—Functional Grouping

# intel

#### 1.1 Pin Description Table

The following table lists a brief description of each pin on the Intel386 DX. The following definitions are used in these descriptions:

- # The named signal is active LOW.

- I Input signal.

- O Output signal.

- I/O Input and Output signal.

- No electrical connection.

| Symbol                          | Туре | Name and Function                                                                                                                                                                                 |

|---------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK2                            | I    | CLK2 provides the fundamental timing for the Intel386 DX.                                                                                                                                         |

| D <sub>31</sub> -D <sub>0</sub> | 1/0  | <b>DATA BUS</b> inputs data during memory, I/O and interrupt acknowledge read cycles and outputs data during memory and I/O write cycles.                                                         |

| A <sub>31</sub> -A <sub>2</sub> | 0    | ADDRESS BUS outputs physical memory or port I/O addresses.                                                                                                                                        |

| BE0#-BE3#                       | 0    | <b>BYTE ENABLES</b> indicate which data bytes of the data bus take part in a bus cycle.                                                                                                           |

| W/R#                            | 0    | <b>WRITE/READ</b> is a bus cycle definition pin that distinguishes write cycles from read cycles.                                                                                                 |

| D/C#                            | 0    | <b>DATA/CONTROL</b> is a bus cycle definition pin that distinguishes data cycles, either memory or I/O, from control cycles which are: interrupt acknowledge, halt, and instruction fetching.     |

| M/IO#                           | 0    | <b>MEMORY I/O</b> is a bus cycle definition pin that distinguishes memory cycles from input/output cycles.                                                                                        |

| LOCK#                           | 0    | <b>BUS LOCK</b> is a bus cycle definition pin that indicates that other system bus masters are denied access to the system bus while it is active.                                                |

| ADS#                            | 0    | <b>ADDRESS STATUS</b> indicates that a valid bus cycle definition and address (W/R#, D/C#, M/IO#, BE0#, BE1#, BE2#, BE3# and $A_{31}$ -A <sub>2</sub> ) are being driven at the Intel386 DX pins. |

| NA#                             | I    | NEXT ADDRESS is used to request address pipelining.                                                                                                                                               |

| READY#                          | I    | BUS READY terminates the bus cycle.                                                                                                                                                               |

| BS16#                           | I    | BUS SIZE 16 input allows direct connection of 32-bit and 16-bit data buses.                                                                                                                       |

| HOLD                            | I    | <b>BUS HOLD REQUEST</b> input allows another bus master to request control of the local bus.                                                                                                      |

| Symbol          | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| HLDA            | 0    | <b>BUS HOLD ACKNOWLEDGE</b> output indicates that the Intel386 DX has surrendered control of its local bus to another bus master.                                                                                                                                                                                                                 |  |  |  |  |  |

| BUSY#           | I    | BUSY signals a busy condition from a processor extension.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| ERROR#          | I    | ERROR signals an error condition from a processor extension.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| PEREQ           | I    | <b>PROCESSOR EXTENSION REQUEST</b> indicates that the processor extension has data to be transferred by the Intel386 DX.                                                                                                                                                                                                                          |  |  |  |  |  |

| FLT#            | I    | <b>FLOAT</b> is an input which forces all bidirectional and output signals, including HLDA, to the tri-state condition. This allows the electrically isolated 386 DX PQFP to use On-Circuit Emulation (ONCE) directly on the motherboard. The FLT# pin has an internal pull-up resistor; if the FLT# pin is not used, it should not be connected. |  |  |  |  |  |

| INTR            | I    | <b>INTERRUPT REQUEST</b> is a maskable input that signals the Intel386 DX to suspend execution of the current program and execute an interrupt acknowledge function.                                                                                                                                                                              |  |  |  |  |  |

| NMI             | I    | <b>NON-MASKABLE INTERRUPT REQUEST</b> is a non-maskable input that signals the Intel386 DX to suspend execution of the current program and execute an interrupt acknowledge function.                                                                                                                                                             |  |  |  |  |  |

| RESET           | I    | <b>RESET</b> suspends any operation in progress and places the Intel386 DX in a known reset state. See <b>Interrupt Signals</b> for additional information.                                                                                                                                                                                       |  |  |  |  |  |

| N/C             | _    | <b>NO CONNECT</b> should always remain unconnected. Connection of a N/C pin may cause the processor to malfunction or be incompatible with future steppings of the Intel386 DX.                                                                                                                                                                   |  |  |  |  |  |

| V <sub>CC</sub> | I    | SYSTEM POWER provides the +5V nominal D.C. supply input.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| V <sub>SS</sub> | I    | <b>SYSTEM GROUND</b> provides 0V connection from which all inputs and outputs are measured.                                                                                                                                                                                                                                                       |  |  |  |  |  |

#### 1.1 Pin Description Table (Continued)

#### Intel386TM DX PQFP MICROPROCESSOR

#### 1.2 Float Pin Description

Activating the FLT# input floats all Intel386 DX bidirectional and output signals, including HLDA. Asserting FLT# isolates the Intel386 DX microprocessor from the surrounding circuitry.

Packaged in a surface mount PQFP, it cannot be removed from the motherboard when In-Circuit Emulation (ICE) is needed. The FLT# input allows the Intel386 CPU to be electrically isolated from the surrounding circuitry. This allows connection of an emulator to the processor without removing it from the PCB. This method of emulation is referred to as ON-Circuit Emulation (ONCE).

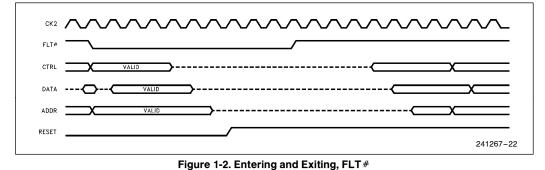

#### ENTERING AND EXITING FLOAT

$\mathsf{FLT}\#$  is an asynchronous, active-low input. It is recognized on the rising edge of CLK2. When recog-

nized, it aborts the current bus cycle and floats the outputs of the processor (Figure 1-2). FLT# must be held low for a minimum of 16 CLK2 cycles. Reset should be asserted and held asserted until after FLT# is deasserted. This will ensure that the Intel386 DX CPU will exit float in a valid state.

Asserting the FLT# input unconditionally aborts the current bus cycle and forces the processor into the FLOAT mode, and is therefore not guaranteed to enter FLOAT in a valid state. After deactivating FLT#, the processor is not guaranteed to exit FLOAT mode in a valid state. This is not a problem as the FLT# pin is meant to be used only during ONCE. After exiting FLOAT, the processor must be reset to return it to a valid state. Reset should be asserted before FLT# is deasserted. This will ensure that the processor will exit float in a valid state.

$\mathsf{FLT}\#$  has an internal pull-up resistor, and if it is not used it should be unconnected.

Preliminary

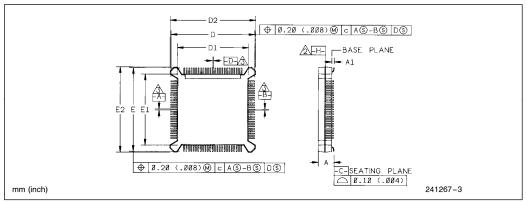

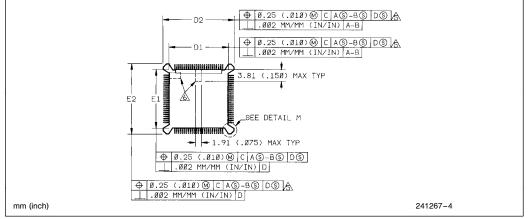

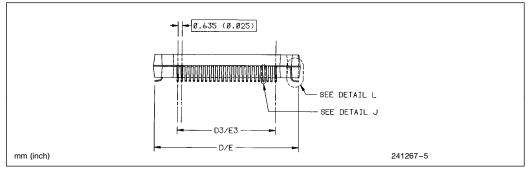

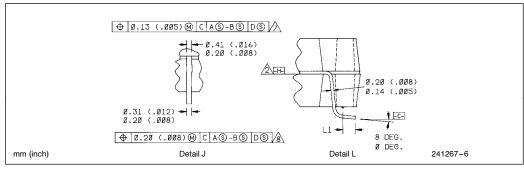

#### 2.0 MECHANICAL DATA

#### 2.1 Package Dimensions

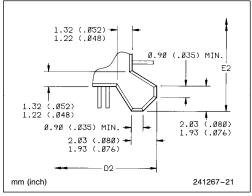

The Intel386 DX is available in a 132 lead plastic quad flat pack (PQFP) package. Table 2.1 and Figures 2.1-2.5 show the physical dimensions of this package.

| Symbol | Description             | In    | ch        | mm    |       |  |  |

|--------|-------------------------|-------|-----------|-------|-------|--|--|

| Cymbol |                         | Min   | Max       | Min   | Max   |  |  |

| A      | Package Height          | 0.160 | 0.170     | 4.06  | 4.32  |  |  |

| A1     | Standoff                | 0.020 | 0.030     | 0.51  | 0.76  |  |  |

| D, E   | Terminal Dimension      | 1.075 | 1.085     | 27.31 | 27.56 |  |  |

| D1, E1 | Package Body            | 0.947 | 0.953     | 24.05 | 24.21 |  |  |

| D2, E2 | Bumper Distance         | 1.097 | 1.103     | 27.86 | 28.02 |  |  |

| D3, E3 | Lead Dimension          | 0.800 | 0.800 REF |       | 2 REF |  |  |

| L1     | Foot Length             | 0.020 | 0.030     | 0.51  | 0.76  |  |  |

| Issue  | IWS Preliminary 1/15/87 |       |           |       |       |  |  |

#### Table 2.1. Intel Case Outline Dimensions for 132 Lead Plastic Quad Flat Pack 0.025 Inch Pitch

#### Symbol List

| Letter or Symbol | Description of Dimensions                                            |

|------------------|----------------------------------------------------------------------|

| А                | Package Height: Distance from Seating Plane to Highest Point of Body |

| A1               | Standoff: Distance from Seating Plane to Base Plane                  |

| D/E              | Overall Package Dimension: Lead Tip to Lead Tip                      |

| D1/E1            | Plastic Body Dimension                                               |

| D2/E2            | Bumper Distance                                                      |

| D3/E3            | Footprint                                                            |

| L1               | Foot Length                                                          |

#### NOTES:

1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

2. Datum plane H located at the mold parting line and coincident with the bottom of the lead where lead exits plastic body.

3. Datums A B and D to be determined where center leads exit plastic body at datum plane H.

4. Controlling Dimension, Inch.

5. Dimensions D1, D2, E1, and E2 are measured at the mold parting line and do not include mold protrusion. Allowable mold protrusion is 0.18 mm (0.007 in) per side. 6. Pin 1 identifier is located within one of the two zones indicated.

#### Intel386™ DX PQFP MICROPROCESSOR

Figure 2.2. Molded Details

Figure 2.3. Terminal Details

### intel

Figure 2.4. Typical Lead

Figure 2.5. Detail M

#### Intel386TM DX PQFP MICROPROCESSOR

#### 2.2 Package Thermal Specifications

The Intel386 DX Microprocessor is specified for operation when case temperature is within the range of  $0^{\circ}C-100^{\circ}C$ . The case temperature may be measured in any environment, to determine whether the Intel386 DX Microprocessor is within specified operating range. The case temperature should be measured at the center of the top surface.

The ambient temperature is guaranteed as long as T<sub>c</sub> is not violated. The ambient temperature can be calculated from the  $\theta_{jc}$  and  $\theta_{ja}$  from the following equations:

$$\begin{split} T_{j} &= T_{c} + P^{*}\theta_{jc} \\ T_{a} &= T_{j} - P^{*}\theta_{ja} \\ T_{c} &= T_{a} + P^{*}[\theta_{ja} - \theta_{jc}] \end{split}$$

Values for  $\theta_{ja}$  and  $\theta_{jc}$  are given in Table 2.2 for the 100 lead fine pitch.  $\theta_{ja}$  is given at various airflows. Table 2.3 shows the maximum T<sub>a</sub> allowable (without exceeding T<sub>c</sub>) at various airflows.

| Package          |     | $\theta_{ja}$ versus Airflow - ft/min (m/sec) |               |               |               |               |                |  |

|------------------|-----|-----------------------------------------------|---------------|---------------|---------------|---------------|----------------|--|

|                  | θjc | 0<br>(0)                                      | 200<br>(1.01) | 400<br>(2.03) | 600<br>(3.04) | 800<br>(4.06) | 1000<br>(5.07) |  |

| 132 Lead<br>PQFP | 9.0 | 31.0                                          | 24.5          | 21.5          | 19.0          | 17.0          | 16.0           |  |

#### Table 2.2. Thermal Resistances (°C/Watt) $\theta_{ic}$ and $\theta_{ia}$

#### Table 2.3. Maximum T<sub>a</sub> at various airflows

|          |           | T <sub>A</sub> (°C) versus Airflow - ft/min (m/sec) |               |               |               |               |                |  |  |

|----------|-----------|-----------------------------------------------------|---------------|---------------|---------------|---------------|----------------|--|--|

| Package  | Frequency | 0<br>(0)                                            | 200<br>(1.01) | 400<br>(2.03) | 600<br>(3.04) | 800<br>(4.06) | 1000<br>(5.07) |  |  |

| 132 Lead | 20 MHz    | 71                                                  | 79            | 83            | 87            | 89            | 90             |  |  |

| PQFP     | 25 MHz    | 65                                                  | 75            | 80            | 84            | 87            | 89             |  |  |

|          | 33 MHz    | 60                                                  | 72            | 78            | 82            | 85            | 87             |  |  |

#### NOTE:

The numbers in Table 2.3 were calculated using worst case  $I_{CC}$  at  $T_C = 100^{\circ}C$  with the outputs unloaded.

#### 3.0 D.C./A.C. SPECIFICATIONS

#### Table 3-1. Maximum Ratings

| Parameter                          | Intel386™ DX<br>20, 25, 33 MHz<br>Maximum Rating |

|------------------------------------|--------------------------------------------------|

| Storage Temperature                | -65°C to +150°C                                  |

| Case Temperature Under Bias        | -65°C to +110°C                                  |

| Supply Voltage with Respect to VSS | -0.5V to +6.5V                                   |

| Voltage on Other Pins              | $-0.5V$ to $V_{\mbox{CC}}$ $+$ $0.5V$            |

Table 3-1 is a stress rating only, and functional operation at the maximums is not guaranteed. Functional operating conditions are given in **3.1 D.C. Specifications** and **3.2 A.C. Specifications**.

Extended exposure to the Maximum Ratings may affect device reliability. Furthermore, although the Intel386 DX contains protective circuitry to resist damage from static electric discharge, always take precautions to avoid high static voltages or electric fields.

#### 3.1 D.C. Specifications

Functional Operating Range:  $V_{CC} = 5V \pm 5\%$ ;  $T_{CASE} = 0^{\circ}C$  to  $\pm 100^{\circ}C$

| Symbol           | Parameter 33 MHz<br>Parameter 33 MHz                                                                                                                                                |                              |                                  |                | nit Test<br>Conditions           |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------|----------------|----------------------------------|--|

|                  |                                                                                                                                                                                     | Min                          | Max                              |                |                                  |  |

| VIL              | Input Low Voltage                                                                                                                                                                   | -0.3                         | 0.8                              | V              | (Note 1)                         |  |

| VIH              | Input High Voltage                                                                                                                                                                  | 2.0                          | $V_{CC} + 0.3$                   | V              |                                  |  |

| VILC             | CLK2 Input Low Voltage                                                                                                                                                              | -0.3                         | 0.8                              | V              | (Note 1)                         |  |

| V <sub>IHC</sub> | CLK2 Input High Voltage<br>20 MHz<br>25 MHz and 33 MHz                                                                                                                              | V <sub>CC</sub> - 0.8<br>3.7 | $V_{CC}$ + 0.3<br>$V_{CC}$ + 0.3 | V<br>V         |                                  |  |

| V <sub>OL</sub>  | Output Low Voltage<br>I <sub>OL</sub> = 4 mA: A2–A31, D0–D31<br>I <sub>OL</sub> = 5 mA: BE0#–BE3#, W/R#,<br>D/C#, M/IO#, LOCK#, ADS#, HLDA                                          |                              | 0.45<br>0.45                     | V<br>V         |                                  |  |

| V <sub>OH</sub>  | Output High Voltage<br>I <sub>OH</sub> = 1 mA: A2-A31, D0-D31<br>I <sub>OH</sub> = 0.9 mA: BE0#-BE3#, W/R#,<br>D/C#, M/IO#, LOCK#, ADS#, HLDA                                       | 2.4<br>2.4                   |                                  | v<br>v         |                                  |  |

| ILI              | Input Leakage Current<br>(For All Pins except BS16#, PEREQ, BUSY#,<br>and ERROR#)                                                                                                   |                              | ±15                              | μA             | $0V \leq V_{IN} \leq V_{CC}$     |  |

| IIH              | Input Leakage Current<br>(PEREQ Pin)                                                                                                                                                |                              | 200                              | μΑ             | $V_{IH} = 2.4V$ (Note 2)         |  |

| IIL              | Input Leakage Current<br>(BS16#, BUSY#, and ERROR# Pins)                                                                                                                            |                              | -400                             | μΑ             | V <sub>IL</sub> = 0.45 (Note 3)  |  |

| I <sub>LO</sub>  | Output Leakage Current                                                                                                                                                              |                              | ±15                              | μA             | $0.45V \leq V_{OUT} \leq V_{CC}$ |  |

| Icc              | Supply Current<br>CLK2 = 40 MHz: with 20 MHz Intel386 <sup>™</sup> DX<br>CLK2 = 50 MHz: with 25 MHz Intel386 <sup>™</sup> DX<br>CLK2 = 66 MHz: with 33 MHz Intel386 <sup>™</sup> DX |                              | 260<br>320<br>390                | mA<br>mA<br>mA | $I_{CC}$ Typ. = 240 mA           |  |

| C <sub>IN</sub>  | Input or I/O Capacitance                                                                                                                                                            |                              | 10                               | pF             |                                  |  |

| COUT             | Output Capacitance                                                                                                                                                                  |                              | 12                               | pF             | $F_{C} = 1 \text{ MHz}$          |  |

| C <sub>CLK</sub> | CLK2 Capacitance                                                                                                                                                                    |                              | 20                               | pF             | $F_{C} = 1 MHz$                  |  |

#### Table 3-2. Intel386™ DX D.C. Characteristics

NOTES:

1. The min value, -0.3, is not 100% tested.

2. PEREQ input has an internal pulldown resistor.

3. BS16#, BUSY# and ERROR# inputs each have an internal pullup resistor.

4. CHMOS IV Technology.

12

#### 3.2 A.C. SPECIFICATIONS

#### 3.2.1 A.C. Spec Definitions

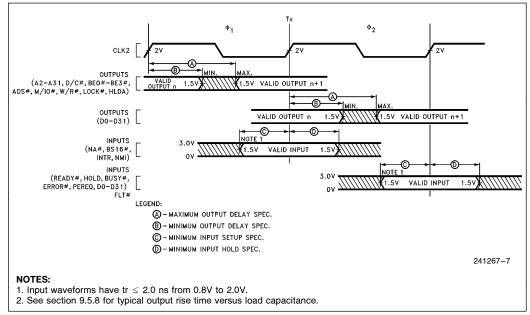

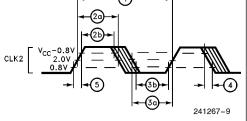

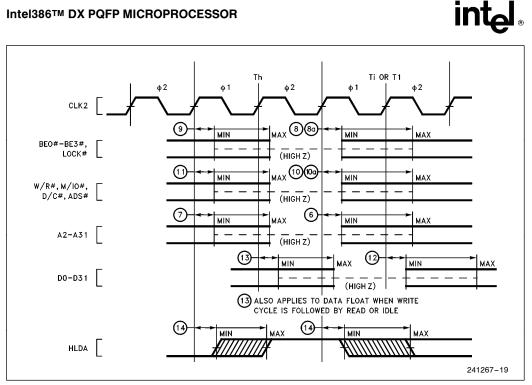

The A.C. specifications, given in Tables 3-3, 3-4, and 3-5, consist of output delays, input setup requirements and input hold requirements. All A.C. specifications are relative to the CLK2 rising edge crossing the 2.0V level.

A.C. spec measurement is defined by Figure 3-1. Inputs must be driven to the voltage levels indicated by Figure 3-1 when A.C. specifications are measured. Intel386 DX output delays are specified with minimum and maximum limits, measured as shown.

#### Intel386TM DX PQFP MICROPROCESSOR

The minimum Intel386 DX delay times are hold times provided to external circuitry. Intel386 DX input setup and hold times are specified as minimums, defining the smallest acceptable sampling window. Within the sampling window, a synchronous input signal must be stable for correct Intel386 DX operation.

Outputs NA#, W/R#, D/C#, M/IO#, LOCK#, BE0#-BE3#, A2-A31 and HLDA only change at the beginning of phase one. D0-D31 (write cycles) only change at the beginning of phase two. The READY#, HOLD, BUSY#, ERROR#, PEREQ and D0-D31 (read cycles) inputs are sampled at the beginning of phase one. The NA#, BS16#, INTR and NMI inputs are sampled at the beginning of phase two.

Figure 3-1. Drive Levels and Measurement Points for A.C. Specifications

#### Intel386<sup>TM</sup> DX PQFP MICROPROCESSOR

#### 3.2.2 A.C. SPECIFICATION TABLES

Functional Operating Range: V\_{CC} = 5V  $\pm 5\%;\, T_{CASE}$  = 0°C to  $+\,100^\circ C$

| Symbol | Parameter                           |      | VHz<br>6™ DX | Unit | Ref.<br>Fig. | Notes                            |

|--------|-------------------------------------|------|--------------|------|--------------|----------------------------------|

|        |                                     | Min  | Max          | 1    | i ig.        |                                  |

|        | Operating Frequency                 | 8    | 33.3         | MHz  |              | Half of CLK2 Frequency           |

| t1     | CLK2 Period                         | 15.0 | 62.5         | ns   | 3-3          |                                  |

| t2a    | CLK2 High Time                      | 6.25 |              | ns   | 3-3          | at 2V                            |

| t2b    | CLK2 High Time                      | 4.5  |              | ns   | 3-3          | at 3.7V                          |

| t3a    | CLK2 Low Time                       | 6.25 |              | ns   | 3-3          | at 2V                            |

| t3b    | CLK2 Low Time                       | 4.5  |              | ns   | 3-3          | at 0.8V                          |

| t4     | CLK2 Fall Time                      |      | 4            | ns   | 3-3          | 3.7V to 0.8V (Note 3)            |

| t5     | CLK2 Rise Time                      |      | 4            | ns   | 3-3          | 0.8V to 3.7V (Note 3)            |

| t6     | A2-A31 Valid Delay                  | 4    | 15           | ns   | 3-5          | C <sub>L</sub> = 50 pF           |

| t7     | A2-A31 Float Delay                  | 4    | 20           | ns   | 3-6          | (Note 1)                         |

| t8     | BE0#-BE3#, LOCK# Valid Delay        | 4    | 15           | ns   | 3-5          | C <sub>L</sub> = 50 pF           |

| t9     | BE0#-BE3#, LOCK# Float Delay        | 4    | 20           | ns   | 3-6          | (Note 1)                         |

| t10    | W/R#, M/IO#, D/C#, Valid Delay      | 4    | 15           | ns   | 3-5          | $C_L = 50 \text{ pF}$            |

| t10a   | ADS# Valid Delay                    | 4    | 14.5         | ns   | 3-5          | C <sub>L</sub> = 50 pF           |

| t11    | W/R#, M/IO#, D/C#, ADS# Float Delay | 4    | 20           | ns   | 3-6          | (Note 1)                         |

| t12    | D0-D31 Write Data Valid Delay       | 7    | 24           | ns   | 3-5a         | C <sub>L</sub> = 50 pF, (Note 4) |

| t12a   | D0-D31 Write Data Hold Time         | 2    |              |      | 3-5b         | $C_L = 50 \text{ pF}$            |

| t13    | D0-D31 Float Delay                  | 4    | 17           | ns   | 3-6          | (Note 1)                         |

| t14    | HLDA Valid Delay                    | 4    | 20           | ns   | 3-6          | C <sub>L</sub> = 50 pF           |

| t15    | NA # Setup Time                     | 5    |              | ns   | 3-4          |                                  |

| t16    | NA# Hold Time                       | 2    |              | ns   | 3-4          |                                  |

| t17    | BS16# Setup Time                    | 5    |              | ns   | 3-4          |                                  |

| t18    | BS16# Hold Time                     | 2    |              | ns   | 3-4          |                                  |

| t19    | READY # Setup Time                  | 7    |              | ns   | 3-4          |                                  |

| t20    | READY # Hold Time                   | 4    |              | ns   | 3-4          |                                  |

#### Table 3-3. 33 MHz Intel386™ DX A.C. Characteristics

#### 3.2.2 A.C. SPECIFICATION TABLES (Continued)

Functional Operating Range: V\_{CC} = 5V  $\pm 5\%;$  T\_{CASE} = 0°C to  $+\,100^\circ\text{C}$

| Symbol | Parameter                                |     | MHz<br>6™ DX | Unit | Ref.<br>Fig. | Notes    |

|--------|------------------------------------------|-----|--------------|------|--------------|----------|

|        |                                          | Min | Max          |      |              |          |

| t21    | D0-D31 Read Setup Time                   | 5   |              | ns   | 3-4          |          |

| t22    | D0-D31 Read Hold Time                    | 3   |              | ns   | 3-4          |          |

| t23    | HOLD Setup Time                          | 11  |              | ns   | 3-4          |          |

| t24    | HOLD Hold Time                           | 2   |              | ns   | 3-4          |          |

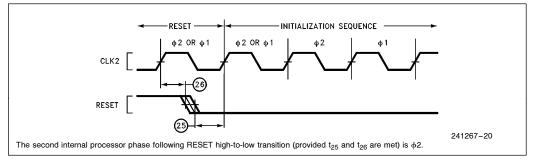

| t25    | RESET Setup Time                         | 5   |              | ns   | 3-7          |          |

| t26    | RESET Hold Time                          | 2   |              | ns   | 3-7          |          |

| t27    | NMI, INTR Setup Time                     | 5   |              | ns   | 3-4          | (Note 2) |

| t28    | NMI, INTR Hold Time                      | 5   |              | ns   | 3-4          | (Note 2) |

| t29    | PEREQ, ERROR #, FLT #, BUSY # Setup Time | 5   |              | ns   | 3-4          | (Note 2) |

| t30    | PEREQ, ERROR #, FLT #, BUSY # Hold Time  | 4   |              | ns   | 3-4          | (Note 2) |

#### Table 3-3. 33 MHz Intel386™ DX A.C. Characteristics (Continued)

#### NOTES:

1. Float condition occurs when maximum output current becomes less than  $I_{LO}$  in magnitude. Float delay is not 100%

tested. 2. These inputs are allowed to be asynchronous to CLK2. The setup and hold specifications are given for testing purposes, to assure recognition within a specific CLK2 period.

Rise and fall times are not tested.

Min. time not 100% tested.

#### Intel386<sup>TM</sup> DX PQFP MICROPROCESSOR

#### 3.2.2 A.C. SPECIFICATION TABLES (Continued)

Functional Operating Range:  $V_{CC} = 5V \pm 5\%$ ;  $T_{CASE} = 0^{\circ}C$  to  $+100^{\circ}C$

| Symbol | Parameter                           | 25 MHz<br>Intel386™ DX |     | Unit | Ref.<br>Fig. | Notes                  |  |

|--------|-------------------------------------|------------------------|-----|------|--------------|------------------------|--|

|        |                                     | Min                    | Max |      | 1 19.        |                        |  |

|        | Operating Frequency                 | 4                      | 25  | MHz  |              | Half of CLK2 Frequency |  |

| t1     | CLK2 Period                         | 20                     | 125 | ns   | 3-3          |                        |  |

| t2a    | CLK2 High Time                      | 7                      |     | ns   | 3-3          | at 2V                  |  |

| t2b    | CLK2 High Time                      | 4                      |     | ns   | 3-3          | at 3.7V                |  |

| t3a    | CLK2 Low Time                       | 7                      |     | ns   | 3-3          | at 2V                  |  |

| t3b    | CLK2 Low Time                       | 5                      |     | ns   | 3-3          | at 0.8V                |  |

| t4     | CLK2 Fall Time                      |                        | 7   | ns   | 3-3          | 3.7V to 0.8V           |  |

| t5     | CLK2 Rise Time                      |                        | 7   | ns   | 3-3          | 0.8V to 3.7V           |  |

| t6     | A2-A31 Valid Delay                  | 4                      | 21  | ns   | 3-5          | $C_L = 50  pF$         |  |

| t7     | A2-A31 Float Delay                  | 4                      | 30  | ns   | 3-6          | (Note 1)               |  |

| t8     | BE0#-BE3# Valid Delay               | 4                      | 24  | ns   | 3-5          | $C_L = 50 \text{ pF}$  |  |

| t8a    | LOCK # Valid Delay                  | 4                      | 21  | ns   | 3-5          | $C_L = 50 \text{ pF}$  |  |

| t9     | BE0#-BE3#, LOCK# Float Delay        | 4                      | 30  | ns   | 3-6          | (Note 1)               |  |

| t10    | W/R#, M/IO#, D/C#, ADS# Valid Delay | 4                      | 21  | ns   | 3-5          | $C_L = 50  pF$         |  |

| t11    | W/R#, M/IO#, D/C#, ADS# Float Delay | 4                      | 30  | ns   | 3-6          | (Note 1)               |  |

| t12    | D0-D31 Write Data Valid Delay       | 7                      | 27  | ns   | 3-5a         | $C_L = 50 \text{ pF}$  |  |

| t12a   | D0-D31 Write Data Hold Time         | 2                      |     |      | 3-5b         | $C_L = 50 \text{ pF}$  |  |

| t13    | D0-D31 Float Delay                  | 4                      | 22  | ns   | 3-6          | (Note 1)               |  |

| t14    | HLDA Valid Delay                    | 4                      | 22  | ns   | 3-6          | $C_L = 50  pF$         |  |

| t15    | NA # Setup Time                     | 7                      |     | ns   | 3-4          |                        |  |

| t16    | NA# Hold Time                       | 3                      |     | ns   | 3-4          |                        |  |

| t17    | BS16# Setup Time                    | 7                      |     | ns   | 3-4          |                        |  |

| t18    | BS16# Hold Time                     | 3                      |     | ns   | 3-4          |                        |  |

| t19    | READY# Setup Time                   | 9                      |     | ns   | 3-4          |                        |  |

| t20    | READY# Hold Time                    | 4                      |     | ns   | 3-4          |                        |  |

#### Table 3-4. 25 MHz Intel386™ DX A.C. Characteristics

#### 3.2.2 A.C. SPECIFICATION TABLES (Continued)

Functional Operating Range: V\_{CC} = 5V  $\pm 5\%;$  T\_{CASE} = 0°C to  $+\,100^\circ\text{C}$

| Symbol | Parameter                                | 25 MHz<br>Intel386™ DX |     | Unit | Ref.<br>Fig. | Notes        |

|--------|------------------------------------------|------------------------|-----|------|--------------|--------------|

|        |                                          |                        | Max |      |              |              |

| t21    | D0-D31 Read Setup Time                   | 7                      |     | ns   | 3-4          |              |

| t22    | D0-D31 Read Hold Time                    | 5                      |     | ns   | 3-4          |              |

| t23    | HOLD Setup Time                          | 15                     |     | ns   | 3-4          |              |

| t24    | HOLD Hold Time                           | 3                      |     | ns   | 3-4          |              |

| t25    | RESET Setup Time                         | 10                     |     | ns   | 3-7          |              |

| t26    | RESET Hold Time                          | 3                      |     | ns   | 3-7          |              |

| t27    | NMI, INTR Setup Time                     | 6                      |     | ns   | 3-4          | (Note 2)     |

| t28    | NMI, INTR Hold Time                      | 6                      |     | ns   | 3-4          | (Note 2)     |

| t29    | PEREQ, ERROR #, FLT #, BUSY # Setup Time | 6                      |     | ns   | 3-4          | (Note 2)     |

| t30    | PEREQ, ERROR #, FLT #, BUSY # Hold Time  | 5                      |     | ns   | 3-4          | (Notes 2, 3) |

#### Table 3-4. 25 MHz Intel386™ DX A.C. Characteristics (Continued)

#### NOTES:

2. These inputs are allowed to be asynchronous to CLK2. The setup and hold specifications are given for testing purposes, to assure recognition within a specific CLK2 period.

3. Symbol 1. Float condition occurs when maximum output current becomes less than  $I_{LO}$  in magnitude. Float delay is not 100%

| 3. |                         | Symbol | Parameter                               | Min |

|----|-------------------------|--------|-----------------------------------------|-----|

|    | $T_{C} = 0^{\circ}C$    | t30    | PEREQ, ERROR #, FLT #, BUSY # Hold Time | 4   |

|    | $T_{C} = +100^{\circ}C$ | t30    | PEREQ, ERROR #, FLT #, BUSY # Hold Time | 5   |

#### Intel386<sup>TM</sup> DX PQFP MICROPROCESSOR

#### 3.2.2 A.C. SPECIFICATION TABLES (Continued)

Functional Operating Range: V<sub>CC</sub> = 5V  $\pm$ 5%; T<sub>CASE</sub> = 0°C to  $\pm$ 100°C

| Symbol          | Parameter                              | 20 MHz<br>Intel386™ DX |     | Unit | Ref. | Notes                              |  |

|-----------------|----------------------------------------|------------------------|-----|------|------|------------------------------------|--|

| •               |                                        | Min                    | Max | 1    | Fig. |                                    |  |

|                 | Operating Frequency                    | 4                      | 20  | MHz  |      | Half of CLK2<br>Frequency          |  |

| t <sub>1</sub>  | CLK2 Period                            | 25                     | 125 | ns   | 3-3  |                                    |  |

| t <sub>2a</sub> | CLK2 High Time                         | 8                      |     | ns   | 3-3  | at 2V                              |  |

| t <sub>2b</sub> | CLK2 High Time                         | 5                      |     | ns   | 3-3  | at (V <sub>CC</sub> - 0.8V)        |  |

| t <sub>3a</sub> | CLK2 Low Time                          | 8                      |     | ns   | 3-3  | at 2V                              |  |

| t <sub>3b</sub> | CLK2 Low Time                          | 6                      |     | ns   | 3-3  | at 0.8V                            |  |

| t <sub>4</sub>  | CLK2 Fall Time                         |                        | 8   | ns   | 3-3  | (V <sub>CC</sub> $-$ 0.8V) to 0.8V |  |

| t <sub>5</sub>  | CLK2 Rise Time                         |                        | 8   | ns   | 3-3  | 0.8V to (V <sub>CC</sub> $-$ 0.8V) |  |

| t <sub>6</sub>  | A2-A31 Valid Delay                     | 4                      | 30  | ns   | 3-5  | C <sub>L</sub> = 120 pF            |  |

| t <sub>7</sub>  | A2-A31 Float Delay                     | 4                      | 32  | ns   | 3-6  | (Note 1)                           |  |

| t <sub>8</sub>  | BE0#-BE3#, LOCK#<br>Valid Delay        | 4                      | 30  | ns   | 3-5  | $C_L = 75  pF$                     |  |

| t <sub>9</sub>  | BE0#-BE3#, LOCK#<br>Float Delay        | 4                      | 32  | ns   | 3-6  | (Note 1)                           |  |

| t <sub>10</sub> | W/R#, M/IO#, D/C#,<br>ADS# Valid Delay | 6                      | 28  | ns   | 3-5  | $C_L = 75  pF$                     |  |

| t <sub>11</sub> | W/R#, M/IO#, D/C#,<br>ADS# Float Delay | 6                      | 30  | ns   | 3-6  | (Note 1)                           |  |

| t <sub>12</sub> | D0-D31 Write Data<br>Valid Delay       | 4                      | 38  | ns   | 3-5c | $C_L = 120  pF$                    |  |

| t <sub>13</sub> | D0-D31 Float Delay                     | 4                      | 27  | ns   | 3-6  | (Note 1)                           |  |

| t <sub>14</sub> | HLDA Valid Delay                       | 6                      | 28  | ns   | 3-6  | C <sub>L</sub> = 75 pF             |  |

| t <sub>15</sub> | NA# Setup Time                         | 9                      |     | ns   | 3-4  |                                    |  |

| t <sub>16</sub> | NA# Hold Time                          | 14                     |     | ns   | 3-4  |                                    |  |

| t <sub>17</sub> | BS16# Setup Time                       | 13                     |     | ns   | 3-4  |                                    |  |

| t <sub>18</sub> | BS16# Hold Time                        | 21                     |     | ns   | 3-4  |                                    |  |

| t <sub>19</sub> | READY # Setup Time                     | 12                     |     | ns   | 3-4  |                                    |  |

| t <sub>20</sub> | READY # Hold Time                      | 4                      |     | ns   | 3-4  |                                    |  |

| t <sub>21</sub> | D0-D31 Read<br>Setup Time              | 11                     |     | ns   | 3-4  |                                    |  |

| t <sub>22</sub> | D0-D31 Read<br>Hold Time               | 6                      |     | ns   | 3-4  |                                    |  |

| t <sub>23</sub> | HOLD Setup Time                        | 17                     |     | ns   | 3-4  |                                    |  |

| t <sub>24</sub> | HOLD Hold Time                         | 5                      |     | ns   | 3-4  |                                    |  |

| t <sub>25</sub> | RESET Setup Time                       | 12                     |     | ns   | 3-7  |                                    |  |

#### Table 3-5. 20 MHz Intel386™ DX A.C. Characteristics

#### 3.2.2 A.C. SPECIFICATION TABLES (Continued)

Functional Operating Range:  $V_{CC} = 5V \pm 5\%$ ;  $T_{CASE} = 0^{\circ}C$  to  $+100^{\circ}C$

| Symbol          | Parameter                                   | 20 MHz<br>Intel386™ DX |     | Unit | Ref.<br>Fig. | Notes    |

|-----------------|---------------------------------------------|------------------------|-----|------|--------------|----------|

|                 |                                             | Min                    | Max |      | g.           |          |

| t <sub>26</sub> | RESET Hold Time                             | 4                      |     | ns   | 3-7          |          |

| t <sub>27</sub> | NMI, INTR Setup Time                        | 16                     |     | ns   | 3-4          | (Note 2) |

| t <sub>28</sub> | NMI, INTR Hold Time                         | 16                     |     | ns   | 3-4          | (Note 2) |

| t <sub>29</sub> | PEREQ, ERROR #, FLT #,<br>BUSY # Setup Time | 14                     |     | ns   | 3-4          | (Note 2) |

| t <sub>30</sub> | PEREQ, ERROR #, FLT #,<br>BUSY # Hold Time  | 5                      |     | ns   | 3-4          | (Note 2) |

#### Table 3-5. 20 MHz Intel386™ DX A.C. Characteristics (Continued)

#### NOTES:

1. Float condition occurs when maximum output current becomes less than ILO in magnitude. Float delay is not 100% tested.

2. These inputs are allowed to be asynchronous to CLK2. The setup and hold specifications are given for testing purposes, to assure recognition within a specific CLK2 period.

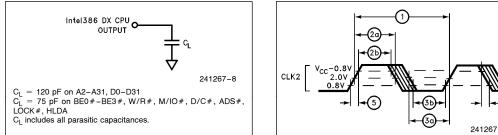

#### 3.2.3 A.C. TEST LOADS

3.2.4 A.C. TIMING WAVEFORMS

Figure 3-3. CLK2 Timing

Figure 3-4. Input Setup and Hold Timing

## int<sub>el</sub>.

Figure 3-5c. Write Data Valid Delay Timing (20 MHz)

VALID n

D0-D31

VALID n+1

241267-14

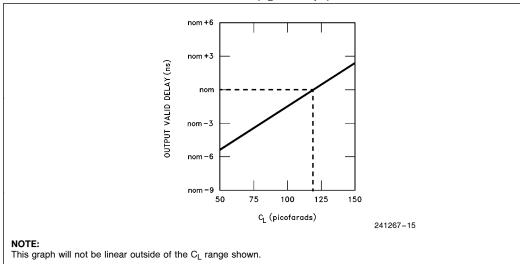

### 3.2.5 TYPICAL OUTPUT VALID DELAY VERSUS LOAD CAPACITANCE AT MAXIMUM OPERATING TEMPERATURE (CL = 120 pF)

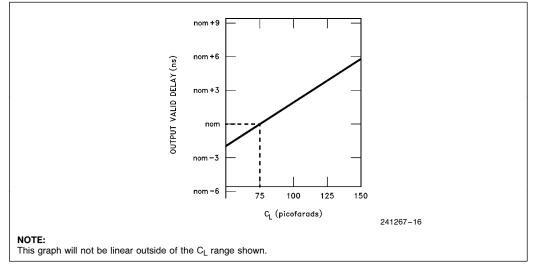

### 3.2.6 TYPICAL OUTPUT VALID DELAY VERSUS LOAD CAPACITANCE AT MAXIMUM OPERATING TEMPERATURE (C\_L = 75 pF)

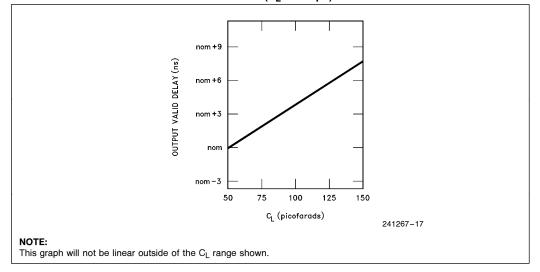

### 3.2.7 TYPICAL OUTPUT VALID DELAY VERSUS LOAD CAPACITANCE AT MAXIMUM OPERATING TEMPERATURE (CL $\,=\,$ 50 pF)

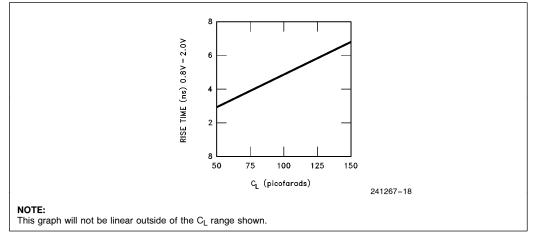

#### 3.2.8 TYPICAL OUTPUT RISE TIME VERSUS LOAD CAPACITANCE AT MAXIMUM OPERATING TEMPERATURE

Figure 3-6. Output Float Delay and HLDA Valid Delay Timing

Figure 3-7. RESET Setup and Hold Timing, and Internal Phase