# Applications Note Guide for Adapting Intel and AMD Designed Motherboards for the IBM 6x86MX Microprocessor

# Introduction

The IBM 6x86MX<sup>TM</sup> microprocessor<sup>1</sup> is plug compatible with existing motherboards for the Intel Pentium® processor<sup>2</sup> with MMX technology<sup>3</sup> and the AMD K6<sup>TM</sup> processor<sup>4</sup> with MMX technology. This document describes the pin and functional differences between these three processors and outlines the steps necessary to run the IBM 6x86MX processor in boards which were designed for the other processors.

In some cases, the IBM 6x86MX processor<sup>5</sup> requires changes to the BIOS, power regulator and CPU cooling solution to work efficiently in these boards. For these items please consult the following applications notes:

- #40250 and #40251: IBM 6x86MX Microprocessor BIOS Writer's Guide

- #40253: Thermal Solutions for the IBM 6x86MX Microprocessor

- #40255: Voltage Regulators for the IBM 6x86MX Microprocessor

It is important to understand the areas of similarity between these processors. All three are available in a PGA package which plugs into Socket 7. Most I/O pins perform the same function for the three processors. Internally the processors are similar. The physical bus structure, paging operation and architectural registers are all compatible. The instruction set is compatible with the exception of a few instructions that are described later in this document. All three processors support the x86 and MMX instruction sets. The remainder of this document describes the pin and functional differences between these processors.

# Pin Differences

- Intel Corporation, 1995.

- 3. Pentium Processor Family Developer's Manual. Intel Corporation, 1997

- 4. AMD-K6 MMX Processor Data Sheet. Advanced Micro Devices, 1997

- 5. *IBM 6x86 Microprocessor Databook*. IBM Microelectronics, 1997

Authors: Baozhen Li and Jack Smith While the IBM 6x86MX processor and the Intel P55C processor use the 296-pin PGA package, the AMD K6 processor has an additional 25 pins to fully utilize the 321-pin capacity of Socket 7. The 25 new pins on the AMD K6 processor are grouped as follows:

14 for Vss, 2 for Vcc2, 4 for Vcc3, 4 as NC, and 1 called KEY.

The 25 extra pins on the K6 processor are for power (20 pins), mechanical guidance (1 pin) and no-connects (4 pins). The pin named "KEY" is not an electrically active pin, its function is to mechanically guide the chip when being plugged in the socket. Overall, the impact of these new pins is minimal on adapting the IBM 6x86MX CPU on system boards designed for the AMD K6 processor. Therefore, the following discussion concentrates on the differences among the IBM 6x86MX processor, Intel P55C and AMD K6 on the 296-pin basis.

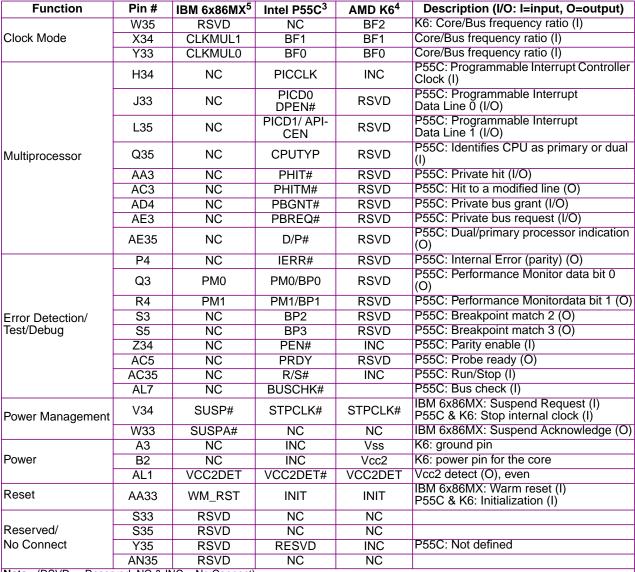

The pin differences are divided into five subgroups: clock mode selection, multiprocessor support, processor initialization, breakpoint/performance monitoring and power management. Table 1 lists the pin differences.

<sup>1.</sup> The IBM 6x86MX microprocessor was designed by Cyrix Corp., and manufactured by IBM Microelectronics

<sup>6</sup>x86 and 6x86MX are trademarks of Cyrix Corporation 2. Intel Pentium Processor Family Developer's Manual. Volume 3:

Architecture and Programming Manual.

Note: (RSVD = Reserved; NC & INC = No Connect)

# Table 1: Pin differences among the IBM 6x86MX, Intel P55C and AMD K6 microprocessors Clock Mode Select for core-to-bus frequency control. Table 2 lists

The IBM 6x86MX processor uses two pins (Y33 and X34 for signals CLKMUL0 and CLKMUL1) to control the clock mode, which is the same as Intel P55C processor, although Intel uses the signal names BF0 and BF1. Both the IBM 6x86MX processor and Intel P55C processor implement these two pins in a similar way, the only difference is that 6x86MX processor supports 3.5x clock mode while Intel P55C reserves this selection. On the other hand, AMD's K6 has one additional pin (W35, the signal is called BF2) for clock mode control. On all three processors, the clock mode inputs are sampled at RESET

for core-to-bus frequency control. Table 2 lists the truth table for the core-to-bus frequency ratio selections. From the clock mode control point of view, virtually no change is needed to plug an the IBM 6x86MX processor in a system designed for Intel P55C. Care needs to be taken when plugging the IBM 6x86MX processor into a board designed for an AMD K6 processor to ensure that pin W35 (reserved on the IBM 6x86MX processor) floats. When pin W35 is set to 1 on the AMD K6 processor, the clock mode selection matches the IBM 6x86MX processor (as shown in Table 2). When pin W35 is set to 0 on the AMD K6, the following combinations of X34 and Y33 generate

core-to-bus frequency ratios of 4.0, 4.5, 5.0 and 5.5.

| Pin X34                                                                                             | Pin Y33                                | IBM 6x86MX <sup>5</sup> | Intel P55C <sup>3</sup> | AMD K6 <sup>4</sup>          |

|-----------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------|-------------------------|------------------------------|

| 6x86MX: CLKMUL1<br>P55C: BF1<br>K6: BF1                                                             | 6x86MX:CLKMUL0<br>P55C: BF0<br>K6: BF0 |                         |                         | Pin W35: BF2 for<br>K6 only  |

| 0                                                                                                   | 0                                      | 2.5                     | 2.5                     | W35 = 1, 2.5<br>W35 = 0, 4.5 |

| 0                                                                                                   | 1                                      | 3                       | 3                       | W35 = 1, 3<br>W35 = 0, 5     |

| 1                                                                                                   | 0                                      | 2                       | 2                       | W35 = 1, 2<br>W35 = 0, 4     |

| 1                                                                                                   | 1                                      | 3                       | Reserved                | W35 = 1, 3.5<br>W35 = 0, 5.5 |

| <b>Note:</b> 0 means the pin is driven logically low, and 1 means the pin is driven logically high. |                                        |                         |                         |                              |

Table 2: Clock mode selection for the IBM 6x86MX, Intel P55C and AMD K6 processors

#### Multiprocessor Support

There are a group of pins on the Intel P55C processor for dual processor implementation. Since the IBM 6x86MX and AMD K6 processors do not support multiprocessor design, these pins are simply No Connects on the IBM 6x86MX processor and reserved on the AMD K6 processor. Therefore, the **IBM 6x86MX processor will not plug and run in a multiprocessor system. Processor Initialization**

The IBM 6x86MX, Intel P55C and AMD K6 microprocessors are initialized in similar ways. RESET is an active high signal for full initialization, and WM\_RST (IBM 6x86MX processor) or INIT (Intel P55C and AMD K6 processors) are active high signals for partial initialization.

The RESET sequence is as follows. At system power up, RESET must remain asserted for at least 1 ms after Vcc and CLK reach their specified AC and DC limits. During normal operation (after power-up), RESET must be asserted 15 CLK cycles to be recognized. Asserting RESET suspends all operations in progress, invalidates internal caches, and clears the write buffers, floating point state, MMX state and all registers. Modified cache lines are not written back. Output signals are driven to their reset value within two CLKs of the rising edge of RESET. The IBM 6x86MX, Intel P55C and AMD K6 microprocessors are similar in that outputs and bi-directional signals common to these chips have the same reset state. The falling edge of RESET determines the mode of operation. Table 3 lists the signals are sampled at that time.

| Signal Name       | Pin  | Operation                                                             | Processor              |

|-------------------|------|-----------------------------------------------------------------------|------------------------|

| FLUSH#            |      | All outputs except TDO, Vcc2DET and bidis float until the next RESET. | AMD K6 <sup>4</sup>    |

| WM_RST<br>or INIT | AA33 |                                                                       | AMD K6                 |

| BRDYC#            | Y3   | Determine the drive strength for certain output signals.              | Intel P55C &<br>AMD K6 |

#### Table 3: Signals sampled at the falling edge of RESET

WM\_RST (IBM 6x86MX processor) and INIT (Intel P55C and AMD K6 processors) perform a partial CPU reset. These signals differ from RESET in that the contents of the on-chip cache, write buffers, configuration registers, floating point and MMX registers remain unchanged. WM\_RST and INIT are implemented through the same pin and are fully compatble.

#### Breakpoints and Performance Monitors Breakpoints

The IBM 6x86MX processor, Intel P55C and AMD K6 microprocessors all allow breakpoints to be programmed through debug registers, but only the Intel P55C processor has output pins (using pins Q3, R4, S3 and S5 for BP0-BP3) to identify when a breakpoint match occurs. The IBM 6x86MX processor and the AMD K6 processor indicate breakpoint matches in software through register DR6. **Performance Monitors**

The IBM 6x86MX processor and the Intel P55C processor use the same pins (Q3 and R4) for performance monitoring, while the AMD K6 processor does not have performance monitor output pins. The IBM 6x86MX processor asserts PM0 and PM1 to indicate at least one overflow or event occurred in the associated Performance Monitor Counter (0-1). The Intel P55C processor does the same thing as the IBM 6x86MX processor except it also uses pins Q3 and R4 to indicate breakpoint matches.

#### **Power Management**

The IBM 6x86MX processor, Intel P55C and AMD K6 all use pin AB34 for signal SMI# as input to force the processor save the CPU sate and enter the defined system management state. They all use pin AG3 for signal SMIACT# as output to indicate that the processor is operating in system management mode. All three can stop the internal clock through pin V33. The IBM 6x86MX processor calls the signal for pin V33 as SUSP#, while the Intel P55C and AMD K6 processors name this pin as STPCLK#. Asserting this pin causes the processor to stop execution at the next instruction boundary and then stop the internal clock. The difference to implement this pin is that the IBM 6x86MX processor requires the BIOS to enable SUSP# by setting an internal configuration bit (CCR2 bit 7). In addition, the IBM 6x86MX processor has pin W33 (SUSPA#) as output to indicate that the processor has entered low power suspend mode. The Intel P55C and AMD K6 processors do not have the SUSPA# output signal.

## Behavioral Differences Bus State Machine

There is one difference between the bus state machines for these processors. For any two consecutive non-pipelined (NA# negated) bus cycles, the Intel P55C and AMD K6 processors have an idle cycle between the last data transfer of the first cycle and the ADS# for the second cycle. Referring to the state diagram in the *Intel Pentium Processor Family*  *Developer's Manual*<sup>3</sup> on page 6-11 for the Intel P55C, the processor moves from state "T2" to state "T1" and then to state "T1". Likewise, the state diagram for the AMD K6 processor in the *AMD-K6*

*MMX Processor Data Sheet*<sup>4</sup> on page 6-3 shows that it moves from state "Data" to state "Idle" to state "Addr". In the same situation, the IBM 6x86MX processor does not insert an idle cycle. The IBM 6x86MX processor moves from state "T2" to state "T1" for all cycles except a cache inquiry hit on modified data (HITM# asserted). The net effect, under the conditions described above, is that the IBM 6x86MX processor initiates bus cycles at different rates than the Intel P55C and the AMD K6 processors, so the system chipset must be able to operate under different rates of bus initiation. **Misaligned Accesses**

These processors define misaligned transfers differently. The three processors define a misaligned transfer as a non-cacheable memory cycle or an I/O cycle that crosses a specified address boundary. All three processors indicate a misaligned transfer by asserting SCYC at the start of the bus cycle. The difference is that the IBM 6x86MX processor calls the transfer misaligned **only** if the data crosses an 8-byte boundary. Meanwhile, the Intel P55C and AMD K6 processors call the transfer misaligned if 2byte or 4-byte transfers cross a 4-byte boundary or 8-byte transfers cross an 8-byte boundary.

This means that the IBM 6x86MX processor requires only one bus cycle (with appropriate byte enables active) for transfers of 2-bytes or 4-bytes that cross a 4-byte boundary while the Intel P55C and AMD K6 processors require two bus cycles to transfer the same information. This difference results in lower bus activity for the IBM 6x86MX processor under these conditions.

#### **INVD** Instruction

When the Intel P55C and AMD K6 processors execute INVD, they invalidate the internal cache. This occurs even if the cache contains modified data, which may cause data coherency problems. **The IBM 6x86MX processor executes INVD identical to the WBINVD instruction**, writing all modified cache data to external memory prior to invalidating the internal cache.

#### System Management Mode (SMM)

All three processors support SMM and support the same hardware protocol, where the SMI# pin is an asynchronous falling edge-triggered hardware interrupt and SMIACT# is an output acknowledge signal

driven active by the processor during SMM mode. They exit SMM via the RSM instruction. The differences (discussed below) are **resolved in software by changing the BIOS and SMM routine** whenever the IBM 6x86MX processor replaces the other two processors.

On the IBM 6x86MX processor, the SMI# and SMI-ACT# pins must be enabled in BIOS before use. The other processors always recognize these pins. To enable these pins on the IBM 6x86MX processor, the BIOS sets a special configuration bit (CCR1 bit 1) in the IBM 6x86MX processor. In addition, the IBM 6x86MX processor requires BIOS to set up configuration registers (CCR1 bit 7, CCR5 bit 5, ARR3, RCR3) to define the SMM base address and size of SMM memory space.

The IBM 6x86MX processor offers nine instructions for SMM which are not supported by the other processors: SMINT, RDSHR, WRSHR, SVDC, RSDC, SVLDT, RSLDT, SVTS, and RSTS. The SMINT instruction is a software interrupt which provides an alternative to using the hardware interrupt to enter SMM mode. RDSHR and WRSHR relocate the SMM header to a place other than the top of SMM memory (SMM base address + FFFFh). SVDC, RSDC, SVLDT, RSLDT, SVTS and RSTS are instructions which may be added to the SMM handler to save and restore the entire CPU state. This is useful for BIOS writers because the contents of the SMM header differs among these processors and this provides a simple way to save the entire IBM 6x86MX CPU state prior to servicing the interrupt.

The IBM 6x86MX processor offers two types of SMM hardware protocols: <u>SL-Compatible Mode</u> and <u>Cyrix Enhanced Mode</u>. The type is selected by writing a configuration bit (CCR6 bit 0) in the 6x86MX processor. The default is SL-Compatible Mode which is similar in operation to the other processors. In SL-Compatible Mode, the SMI#-SMI-

ACT# pins behave as described earlier in this section. In Cyrix Enhanced Mode, the SMI# signal is level-sensitive and SMIACT# no longer indicates that the CPU is in SMM mode. In Cyrix Enhanced Mode, SMIACT# is asserted during each SMM memory bus cycle and de-asserted for all other cycles. Cyrix Enhanced SMM provides new features, including cacheability of SMM memory and support for nested SMIs.

In summary, when adapting systems to use the 6x86MX processor the BIOS must set up configuration registers to enable SMM operation, understand the organization of the SMM header and determine the initial register settings upon entering SMM. The latter two items may require modification to the SMM service routine.

## **CPUID Instruction**

All three processors support the CPUID instruction but each processor returns a different vendor ID string when CPUID is executed. The vendor ID string for the IBM 6x86MX processor is "CyrixInstead". All three processors enable the CPUID instruction at power-up. In addition, the IBM 6x86MX processor can disable CPUID execution after power-up by writing a configuration bit (CCR4 bit 7).

# Model Specific Registers

All three processors support Model Specific Registers, although they differ in which features are supported. To use MSRs, the MSR address is loaded into the ECX register and an instruction (RDMSR or WRMSR) is executed to transfer 64 bits of data between the selected MSR and EDX:EAX. The table below shows the MSRs supported by each processor.

|                                                               | MOD            | Processor Support                            |                        |                              |

|---------------------------------------------------------------|----------------|----------------------------------------------|------------------------|------------------------------|

| Model Specific Register                                       | MSR<br>Address | IBM<br>6x86MX <sup>5</sup>                   | AMD<br>K6 <sup>4</sup> | Intel<br>P55C <sup>2,3</sup> |

| Machine Check Address Register (MCAR)                         | 00h            | No                                           | Yes                    | Yes                          |

| Machine Check Type Register (MCTR)                            | 01h            | No                                           | Yes                    | Yes                          |

| TR1 (parity reversal register)                                | 02h            | No                                           | No                     | Yes                          |

| Scratch Pad RAM (cache line data)                             | 03h            | Yes                                          | No                     | No                           |

| Scratch Pad RAM (cache line address)                          | 04h            | Yes                                          | No                     | No                           |

| Scratch Pad RAM (cache line control) or TR3 (cache test data) | 05h            | Yes<br>Scratch Pad RAM<br>TR3 access via MOV | No                     | Yes<br>TR3                   |

| TR4 (cache test tag)                                          | 06h            | No<br>TR4 access via MOV                     | No                     | Yes                          |

#### **Table 4: Model Specific Registers**

| TR5 (cache test control)                     | 07h       | No<br>TR5 access via MOV   | No  | Yes |

|----------------------------------------------|-----------|----------------------------|-----|-----|

| TR6 (TLB test linear address)                | 08h       | No<br>TR6 access via MOV   | No  | Yes |

| TR7 (TLB test control & phys addr 31-12)     | 09h       | No<br>TR7 access via MOV   | No  | Yes |

| TR9 (BTB test tag)                           | 0Bh       | No                         | No  | Yes |

| TR10 (BTB test target)                       | 0Ch       | No                         | No  | Yes |

| TR11 (BTB test control)                      | 0Dh       | No                         | No  | Yes |

| TR12 (core feature disable)                  | 0Eh       | No                         | Yes | Yes |

| Time Stamp Counter                           | 10h       | Yes                        | Yes | Yes |

| Counter Event Selection and Control Register | 11h       | Yes                        | No  | Yes |

| Performance Counter #0                       | 12h       | Yes                        | No  | Yes |

| Performance Counter #1                       | 13h       | Yes                        | No  | Yes |

| Extended Feature Enable Register (EFER)      | C0000080h | No                         | Yes | No  |

| SYSCALL Target Address Register (STAR)       | C0000081h | No                         | Yes | No  |

| Write Handling Control Register (WHCR)       | C0000082h | No<br>Write Alloc via CCR5 | Yes | No  |

Table 4: Model Specific Registers

Note that the IBM 6x86MX processor is the only processor that supports Scratch Pad RAM, otherwise known as "cache line locking". This feature allows a set of lines in the L1 cache to be defined as private cpu memory to store critical data or code. Locked lines do not go through cache coherency protocol so they are not subject to snooping, invalidate, writeback, flush or replacement.

All three processors support the Time Stamp Counter at MSR 10h. The IBM 6x86MX and Intel P55C processors also support the RDTSC instruction to access this same data. The AMD K6 processor does not support Performance Monitor Counters (MSR 11-13 or the RDPMC instruction) which the IBM 6x86MX and Intel P55C processors use to monitor internal core events.

To test the L1 cache, the Intel P55C processor supports TR3-TR5 at MSR addresses 05h-07h. The IBM 6x86MX processor supports TR3-TR5 in a similar manner using the MOV instruction. The AMD K6 processor does not support TR3-TR5.

The Translation Lookaside Buffer is tested using TR6-TR7 on the Intel P55C and the IBM 6x86MX processors. The Intel P55C processor implements these registers at MSR addresses 08h-09h. The IBM 6x86MX processor supports TR6-TR7 in a similar manner through the MOV instruction. AMD K6 does not support TR6-TR7.

Both the IBM 6x86MX and AMD K6 processors support the Write Allocate feature. When this feature is enabled the processor allocates a new line in the L1 cache whenever it has a pending memory write cycle and the line does not exist in the cache. This feature is enabled on the IBM 6x86MX processor by writing a configuration bit (CCR5 bit 0). On the AMD K6 processor, this feature is controlled through MSR C0000082h.

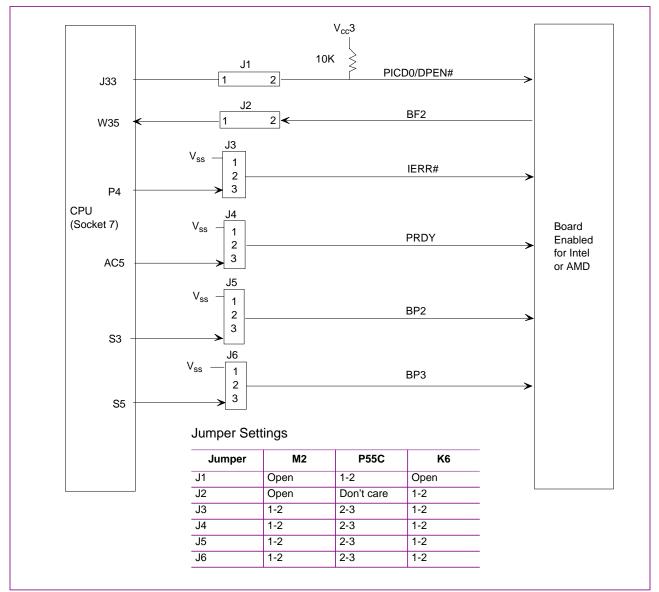

Figure 1. Common Socket Specification

# Conclusion

It is fairly simple to modify Socket 7 boards to support the IBM 6x86MX processor. With a few jumper switches to handle pin differences and BIOS changes to enable the IBM 6x86MX processor features, boards can fully support the IBM 6x86MX processor. There are some behavioral differences between the processors discussed in this application note which software writers and chipset designers must consider as they develop their products.

## References

- 1. *IBM 6x86MX Microprocessor Databook*, IBM Corporation, 1997.

- 2. *Pentium Processor with MMX Technology*. Intel Corporation, 1997.

- 3. *Pentium Processor Family Developer's Manual*, Volume 3: Architecture and Programming Manual. Intel Corporation, 1995.

- 4. *Pentium Processor Family Developer's Manual.* Intel Corporation, 1997.

- 5. *AMD-K6 MMX Processor Data Sheet*. Advanced Micro Devices, 1997.

# IBM ®

© International Business Machines Corporation 1997.

Printed in the United States of America. All rights reserved.

**IBM Microelectronics Division**

1580 Route 52

Hopewell Junction, NY 12533-6531

IBM, the IBM logo and O/S2 are registered trademarks of International Business Machines Corporation.

IBM Microelectronics is a trademark of IBM Corp. 6x86, 6x86L and 6x86MX are trademarks of Cyrix Corporation. MMX is a trademark of Intel Corporation. UNIX is a registered trademark in the United States and other countries licensed exclusively through X/Open Company Limited. Windows, Windows NT and Windows 95 are trademarks or registered trademarks of Microsoft Corporation. All other product and company names are trademarks/registered trademarks of their respective holders.

All information contained in this document is subject to change without notice. The information contained herein does not affect IBM's product specifications or warranties. All information contained in this document was obtained in specific environments and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS AND NO WARRANTIES OF ANY KIND EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT. In no event will IBM be liable to you or to any third parties for any damages arising directly or indirectly from any use of the information contained in this document.

For more information contact your IBM Microelectronics Sales Representative

Or visit our website at http://www.chips.ibm.com