# Cyrix<sup>®</sup> M II<sup>™</sup>

# M II -433 (100/300MHz) Addendum

April 23, 1999 5:23

Addendums and other updates for this manual can be obtained from Cyrix Web site: www.cyrix.com.

# **REVISION HISTORY**

| Date    | Version | Revision                                                          |

|---------|---------|-------------------------------------------------------------------|

| 4/23/99 | 0.1     | Initial Version C:\!!!devices\MII\Addendum\MII-433 100_300.ADD.fm |

**M** II<sup>™</sup> **PROCESSOR** Enhanced Sixth-Generation CPU Compatible with MMX<sup>™</sup> Technology

#### M II - 433 (100/300 MHz) Addendum

# 1.0 ELECTRICAL SPECIFICATIONS

#### 1.1 Electrical Connections

This section provides information on electrical connections, absolute maximum ratings, recommended operating conditions, DC characteristics, and AC characteristics. All voltage values in Electrical Specifications are measured with respect to  $V_{SS}$  unless otherwise noted.

The M II CPU operates using two power supply voltages—one for the I/O (3.3 V) and one for the core (2.2 V).

#### 1.1.1 Power and Ground Connections and Decoupling

Testing and operating the M II CPU requires the use of standard high frequency techniques to reduce parasitic effects. The high clock frequencies used in the M II CPU and its output buffer circuits can cause transient power surges when several output buffers switch output levels simultaneously. These effects can be minimized by filtering the DC power leads with low-inductance decoupling capacitors, using low impedance wiring, and by utilizing all of the V<sub>CC</sub> and GND pins. The M II CPU contains 296 pins with 25 pins connected to  $V_{CC2}$  (2.2 volts), 28 pins connected to  $V_{CC3}$  (3.3 volts), and 53 pins connected to  $V_{SS}$  (ground).

#### 1.1.2 Pull-Up/Pull-Down Resistors

Table 1 lists the input pins that are internally connected to pull-up and pull-down resistors. The pull-up resistors are connected to  $V_{CC}$  and the pull-down resistors are connected to  $V_{SS}$ . When unused, these inputs do not require connection to external pull-up or pull-down resistors. The SUSP# pin is unique in that it is connected to a pull-up resistor only when SUSP# is not asserted.

| Table 1. | Pins Connected to Internal Pull-Up |

|----------|------------------------------------|

|          | and Pull-Down Resistors            |

| SIGNAL   | PIN NO. | RESISTOR                           |

|----------|---------|------------------------------------|

| BRDYC#   | Y3      | 20-kΩ pull-up                      |

| CKMUL0   | Y33     | 20-kΩ pull-up                      |

| CKMUL1   | X34     | 20-k $\Omega$ pull-down (see text) |

| Reserved | AN35    | 20-kΩ pull-down                    |

| VCC2H/L# | AN5     | 20-kΩ pull-down                    |

| CKMUL2   | W35     | 20-kΩ pull-up                      |

| SMI#     | AB34    | 20-kΩ pull-up                      |

| SUSP#    | Y34     | 20-k $\Omega$ pull-up (see text)   |

| TCK      | M34     | 20-kΩ pull-up                      |

| TDI      | N35     | 20-kΩ pull-up                      |

| TMS      | P34     | 20-kΩ pull-up                      |

| TRST#    | Q33     | 20-kΩ pull-up                      |

# 1.1.3 Unused Input Pins

All inputs not used by the system designer and not listed in Table 1 should be connected either to ground or to  $V_{CC}$ . Connect active-high inputs to ground through a 10 k $\Omega$  (± 10%) pull-down resistor and active-low inputs to  $V_{CC}$  through a 10 k $\Omega$  (± 10%) pull-up resistor to prevent possible spurious operation.

### 1.1.4 NC and Reserved Pins

Pins designated NC have no internal connections. Pins designated RESV or RESERVED should be left disconnected. Connecting a reserved pin to a pull-up resistor, pull-down resistor, or an active signal could cause unexpected results and possible circuit malfunctions.

## 1.2 Absolute Maximum Ratings

The following table lists absolute maximum ratings for the M II CPU processors. Stresses beyond those listed under Table 1-2 limits may cause permanent damage to the device. These are stress ratings only and do not imply that operation under any conditions other than those listed under "Recommended Operating Conditions" Table 1-3 (Page 4-3) is possible. Exposure to conditions beyond Table 1-2 may (1) reduce device reliability and (2) result in premature failure even when there is no immediately apparent sign of failure. Prolonged exposure to conditions at or near the absolute maximum ratings may also result in reduced useful life and reliability.

| PARAMETER                             | MIN  | MAX             | UNITS | NOTES                  |

|---------------------------------------|------|-----------------|-------|------------------------|

| Operating Case Temperature            | -65  | 110             | °C    | Power Applied          |

| Storage Temperature                   | -65  | 150             | °C    |                        |

| Supply Voltage, V <sub>CC3</sub>      | -0.5 | 4.0             | V     |                        |

| Supply Voltage, V <sub>CC2</sub>      | -0.5 | 3.3             | V     |                        |

| Voltage On Any Pin                    | -0.5 | $V_{CC3} + 0.5$ | V     | Not to exceed Vcc3 max |

| Input Clamp Current, I <sub>IK</sub>  |      | 10              | mA    | Power Applied          |

| Output Clamp Current, I <sub>OK</sub> |      | 25              | mA    | Power Applied          |

Table 1-2. Absolute Maximum Ratings

1

# **1.3 Recommended Operating Conditions**

Table 1-3 presents the recommended operating conditions for the M II CPU device.

| PARAMETER                                             | MIN   | MAX   | UNITS | NOTES                                |

|-------------------------------------------------------|-------|-------|-------|--------------------------------------|

| T <sub>C</sub> Operating Case Temperature             | 0     | 70    | °C    | Power Applied                        |

| V <sub>CC3</sub> Supply Voltage (3.3 V)               | 3.135 | 3.465 | V     |                                      |

| V <sub>CC2</sub> Supply Voltage (2.2 V)               | 2.1   | 2.3   | V     |                                      |

| V <sub>IH</sub> High-Level Input Voltage (except CLK) | 2.00  | 3.55  | V     |                                      |

| V <sub>IH</sub> CLK High-Level Input Voltage          | 2.0   | 5.5   | V     |                                      |

| V <sub>IL</sub> Low-Level Input Voltage               | -0.3  | 0.8   | V     |                                      |

| I <sub>OH</sub> High-Level Output Current             |       | -1.0  | mA    | V <sub>O</sub> =V <sub>OH(MIN)</sub> |

| IOL Low-Level Output Current                          |       | 5.0   | mA    | V <sub>O</sub> =V <sub>OL(MAX}</sub> |

Table 1-3. Recommended Operating Conditions

DC Characteristics

# 1.4 DC Characteristics

| PARAMETER                                                                                   | MIN | ТҮР | MAX  | UNITS | NOTES                             |

|---------------------------------------------------------------------------------------------|-----|-----|------|-------|-----------------------------------|

| V <sub>OL</sub> Low-Level Output Voltage                                                    |     |     | 0.4  | V     | $I_{OL} = 5 \text{ mA}$           |

| V <sub>OH</sub> High-Level Output Voltage                                                   | 2.4 |     |      | V     | $I_{OH} = -1 \text{ mA}$          |

| I <sub>I</sub> Input Leakage Current<br>For all pins (except those<br>listed in Table 4-1). |     |     | ±15  | μA    | $0 < V_{IN} < V_{CC3}$<br>Note 1  |

| I <sub>IH</sub> Input Leakage Current<br>For all pins with internal<br>pull-downs.          |     |     | 200  | μA    | V <sub>IH</sub> = 2.4 V<br>Note 1 |

| I <sub>IL</sub> Input Leakage Current<br>For all pins with internal pull-ups.               |     |     | -400 | μΑ    | $V_{IL} = 0.45 V$<br>Note 1       |

| C <sub>IN</sub> Input Capacitance                                                           |     |     | 15   | pF    | $f = 1 MHz^*$                     |

| C <sub>OUT</sub> Output Capacitance                                                         |     |     | 20   | pF    | $f = 1 MHz^*$                     |

| C <sub>IO</sub> I/O Capacitance                                                             |     |     | 25   | pF    | $f = 1 MHz^*$                     |

| C <sub>CLK</sub> CLK Capacitance                                                            |     |     | 15   | pF    | $f = 1 MHz^*$                     |

#### Table 1-4. DC Characteristics (at Recommended Operating Conditions) 1 of 2

\*Note: Not 100% tested.

1

Table 1-5. DC Characteristics (at Recommended Operating Conditions) 2 of 2

| PARAMETER                                                                  | ICC2 MAX | ICC3 MAX | UNITS | NOTES         |

|----------------------------------------------------------------------------|----------|----------|-------|---------------|

| I <sub>CC</sub> Active I <sub>CC</sub>                                     |          |          |       | Notes 1, 2    |

| 100/300 MHz                                                                | 6080     | 100      | mA    |               |

| I <sub>CCSM</sub> Active I <sub>CC</sub>                                   |          |          |       | Notes 1, 2, 3 |

| 100/300 MHz                                                                | 57       | 100      | mA    |               |

| I <sub>CCSS</sub> Standby I <sub>CC</sub><br>0 MHz (Suspended/CLK Stopped) | 30       | 50.0     | mA    | Notes 1, 2, 4 |

Notes: 1. These values should be used for power supply design. Maximum I<sub>CC</sub> is determined using the worst-case instruction sequences and functions at maximum Vcc.

2. Frequency (MHz) ratings refer to the internal clock frequency.

3. All inputs at 0.4 or  $V_{CC3}$  - 0.4 (CMOS levels). All inputs held static except clock and all outputs unloaded (static  $I_{OUT} = 0$  mA).

4. All inputs at 0.4 or  $V_{CC3}$  - 0.4 (CMOS levels). All inputs held static and all outputs unloaded (static  $I_{OUT} = 0$  mA).

#### Table 1-6. Power Dissipation

| PARAMETER                                                       | POWER |       | UNITS | NOTES      |

|-----------------------------------------------------------------|-------|-------|-------|------------|

|                                                                 | ТҮР   | MAX   |       |            |

| Active Power Dissipation<br>100/300 MHz                         | 12.0  | 13.7  | W     | Note 1     |

| Suspend Mode Power Dissipation<br>100/300 MHz                   |       | 0.157 | W     | Notes 1, 2 |

| Standby Mode Power Dissipation<br>0 MHz (Suspended/CLK Stopped) |       | 0.070 | W     | Notes 1, 3 |

Notes: 1. Systems must be designed to thermally dissipate the maximum active power dissipation. Maximum power is determined using the worst-case instruction sequences and functions with Vcc2 = 2.2 V and Vcc3 = 3.3 V.

2. All inputs at 0.4 or  $V_{CC3}$  - 0.4 (CMOS levels). All inputs held static except clock and all outputs unloaded (static  $I_{OUT} = 0$  mA).

3. All inputs at 0.4 or  $V_{CC3}$  - 0.4 (CMOS levels). All inputs held static and all outputs unloaded (static  $I_{OUT} = 0$  mA).

**AC** Characteristics

## **1.5** AC Characteristics

Tables 1-7 through 1-12 (Pages 7 through 11) list the AC characteristics including output delays, input setup requirements, input hold requirements and output float delays. These measurements are based on the measurement points identified in Figure 1-1 and Figure 1-2 on page 8. The rising clock edge reference level  $V_{REF}$  and other reference levels are shown in Table 1-7. Input or output signals must cross

these levels during testing.

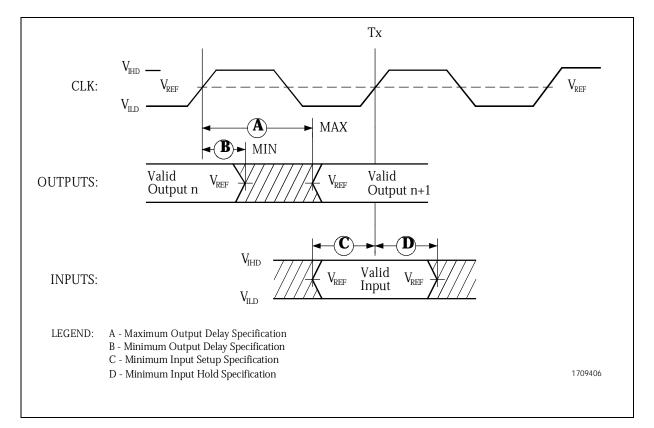

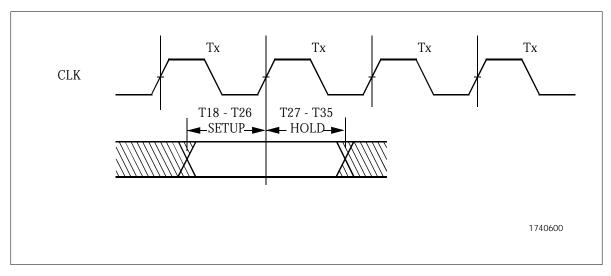

Figure 1-1 shows output delay (A and B) and input setup and hold times (C and D). Input setup and hold times (C and D) are specified minimums, defining the smallest acceptable sampling window a synchronous input signal must be stable for correct operation.

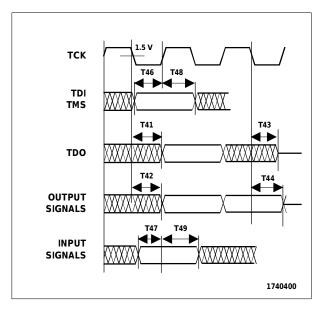

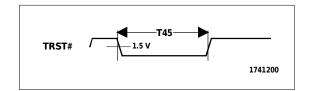

The JTAG AC timing is shown in Table 1-13 (Page 13) supported by Figures 1-6 (Page 13) though 1-8 (Page 14).

Figure 1-1. Drive Level and Measurement Points for Switching Characteristics

| Table 1-7. Drive Level and Measurement<br>Points for Switching Characteristics |  |    |       |  |  |

|--------------------------------------------------------------------------------|--|----|-------|--|--|

|                                                                                |  | VO | LTAGE |  |  |

| SYMBOL           | VOLTAGE<br>(Volts) |

|------------------|--------------------|

| V <sub>REF</sub> | 1.5                |

| V <sub>IHD</sub> | 2.3                |

| V <sub>ILD</sub> | 0                  |

Note: Refer to Figure 4-1.

100-MHz BUS PARAMETER UNITS MIN MAX f CLK Frequency 100 MHz T1 CLK Period 10.5 ns T2 CLK Period Stability ±250 ps Т3 CLK High Time 3.0 ns T4 CLK Low Time 3.0 ns CLK Fall Time T5 0.15 1.5 ns T6 CLK Rise Time 0.15 1.5 ns

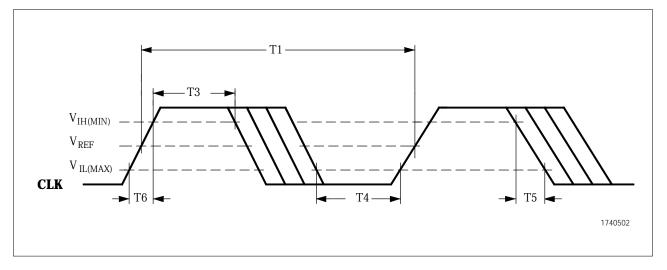

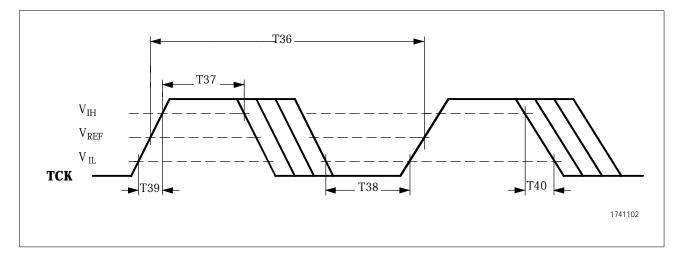

#### Table 1-8. Clock Specifications T<sub>CASE</sub> = 0°C to 70°C, See Figure 4-2

Figure 1-2. CLK Timing and Measurement Points

|      | PARAMETER                                                        |     | 100-MHz BUS<br>$\mathbf{C}_{\mathrm{L}} = \mathbf{O} \ \mathbf{pF}$ |    |  |

|------|------------------------------------------------------------------|-----|---------------------------------------------------------------------|----|--|

|      |                                                                  | MIN | MAX                                                                 |    |  |

| T7a  | A31-A3                                                           | 1.0 | 4.0                                                                 | ns |  |

| T7b  | BE7#-BE0#, CACHE#, D/C#, LOCK#,<br>PCD, PWT, SCYC, SMIACT#, W/R# | 1.0 | 4.0                                                                 | ns |  |

| T7c  | ADS#                                                             | 1.0 | 4.0                                                                 | ns |  |

| T7d  | M/IO#                                                            | 1.0 | 4.0                                                                 | ns |  |

| T8   | ADSC#                                                            | 1.0 | 4.0                                                                 | ns |  |

| T9   | AP                                                               | 1.0 | 5.5                                                                 | ns |  |

| T10  | APCHK#, PCHK#, FERR#                                             | 1.0 | 4.5                                                                 | ns |  |

| T11  | D63-D0, DP7-DP0 (Write)                                          | 1.3 | 4.5                                                                 | ns |  |

| T12a | HIT#                                                             | 1.0 | 4.0                                                                 | ns |  |

| T12b | HITM#                                                            | 1.1 | 4.0                                                                 | ns |  |

| T13a | BREQ                                                             | 1.0 | 4.0                                                                 | ns |  |

| T13b | HLDA                                                             | 1.0 | 4.0                                                                 | ns |  |

| T14  | SUSPA#                                                           | 1.0 | 4.0                                                                 | ns |  |

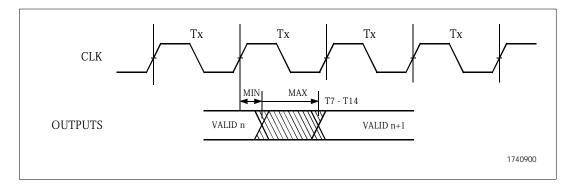

# Table 1-9. Output Valid Delays T<sub>case</sub> = 0°C to 70°C, See Figure 4-3

Figure 1-3. Output Valid Delay Timing

AC Characteristics

|     | PARAMETER                                                                         |     | 100-MHz BUS<br>C <sub>L</sub> = 0 pF |    |

|-----|-----------------------------------------------------------------------------------|-----|--------------------------------------|----|

|     |                                                                                   | MIN | MAX                                  |    |

| T15 | A31-A3, ADS#, BE7#-BE0#,<br>CACHE#, D/C#, LOCK#, PCD,<br>PWT, SCYC, SMIACT#, W/R# |     | 7.0                                  | ns |

| T16 | AP                                                                                |     | 7.0                                  | ns |

| T17 | D63-D0, DP7-DP0 (Write)                                                           |     | 7.0                                  | ns |

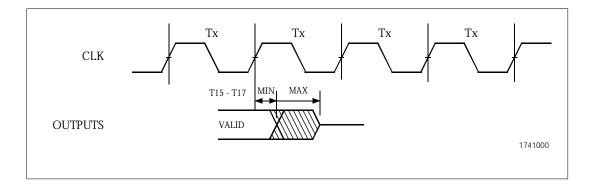

# Table 1-10. Output Float Delays T<sub>case</sub> = 0°C to 70°C, See Figure 4-5

Figure 1-4. Output Float Delay Timing

1

|      | PARAMETER                      | 100-MHz<br>BUS | UNITS |

|------|--------------------------------|----------------|-------|

|      |                                | MIN            |       |

| T18a | A20M#                          | 3.0            | ns    |

| T18b | FLUSH#, IGNNE#, SUSP#          | 1.7            | ns    |

| T19a | AHOLD, BOFF#                   | 3.5            | ns    |

| T19b | HOLD                           | 1.7            | ns    |

| T20  | BRDY#                          | 3.0            | ns    |

| T21  | BRDYC#                         | 3.0            | ns    |

| T22a | A31-A3, BE7#-BE0#              | 3.0            | ns    |

| T22b | AP                             | 1.7            | ns    |

| T22c | D63-D0 (Read), DP7-DP0 (Read)  | 1.7            | ns    |

| T23a | EADS#                          | 3.0            | ns    |

| T23b | INV                            | 1.7            | ns    |

| T24  | INTR, NMI, RESET, SMI#, WM_RST | 1.7            | ns    |

| T25a | EWBE#, NA#, WB/WT#             | 1.7            | ns    |

| T25b | KEN#                           | 3.0            | ns    |

#### Table 1-11. Input Setup Times T<sub>case</sub> = 0°C to 70°C, See Figure 4-5

#### Table 1-12. Input Hold Times T<sub>case</sub> = 0°C to 70°C, See Figure 4-5

| SYMBOL | PARAMETER                      | 100-MHz<br>BUS | UNITS |  |

|--------|--------------------------------|----------------|-------|--|

|        |                                | MIN            |       |  |

| T27    | A20M#, FLUSH#, IGNNE#, SUSP#   | 1.0            | ns    |  |

| T28a   | AHOLD, BOFF#                   | 1.0            | ns    |  |

| T28b   | HOLD                           | 1.5            | ns    |  |

| T29    | BRDY#                          | 1.0            | ns    |  |

| T30    | BRDYC#                         | 1.0            | ns    |  |

| T31a   | A31-A3, AP, BE7#-BE0#,         | 1.0            | ns    |  |

| T31b   | AP                             | 1.0            | ns    |  |

| T31c   | D63-D0 (Read), DP7-DP0 (Read)  | 1.7            | ns    |  |

| T32    | EADS#, INV                     | 1.0            | ns    |  |

| T33    | INTR, NMI, RESET, SMI#, WM_RST | 1.0            | ns    |  |

| T34    | EWBE#, KEN#, NA#, WB/WT#       | 1.0            | ns    |  |

#### PRELIMINARY

Figure 1-5. Input Setup and Hold Timing

| SYMBOL | PARAMETER                    | ALL BUS FR | ALL BUS FREQUENCIES |       | FIGURE |

|--------|------------------------------|------------|---------------------|-------|--------|

|        |                              | MIN        | MAX                 | UNITS | FIGURE |

|        | TCK Frequency (MHz)          |            | 20                  | ns    |        |

| T36    | TCK Period                   | 50         |                     | ns    | 4-6    |

| T37    | TCK High Time                | 25         |                     | ns    | 4-6    |

| T38    | TCK Low Time                 | 25         |                     | ns    | 4-6    |

| T39    | TCK Rise Time                |            | 5                   | ns    | 4-6    |

| T40    | TCK Fall Time                |            | 5                   | ns    | 4-6    |

| T41    | TDO Valid Delay              | 3          | 20                  | ns    | 4-7    |

| T42    | Non-test Outputs Valid Delay | 3          | 20                  | ns    | 4-7    |

| T43    | TDO Float Delay              |            | 25                  | ns    | 4-7    |

| T44    | Non-test Outputs Float Delay |            | 25                  | ns    | 4-7    |

| T45    | TRST# Pulse Width            | 40         |                     | ns    | 4-8    |

| T46    | TDI, TMS Setup Time          | 20         |                     | ns    | 4-7    |

| T47    | Non-test Inputs Setup Time   | 20         |                     | ns    | 4-7    |

| T48    | TDI, TMS Hold Time           | 13         |                     | ns    | 4-7    |

| T49    | Non-test Inputs Hold Time    | 13         |                     | ns    | 4-7    |

Table 1-13. JTAG AC Specifications

Figure 1-6. TCK Timing and Measurement Points

#### PRELIMINARY

Figure 1-7. JTAG Test Timings

Figure 1-8. Test Reset Timing

©1999 Copyright National Semiconductor Corporation. All rights reserved. Printed in the United States of America

Trademark Acknowledgments:

Cyrix is a registered trademark of Cyrix Corporation. 6x86, 6x86MX and M II are trademarks of Cyrix Corporation. MMX is a trademark of Intel Corporation. All other brand or product names are trademarks of their respective companies.

Cyrix Corporation 2703 North Central Expressway Richardson, Texas 75080-2010 United States of America

Cyrix Corporation (Cyrix) reserves the right to make changes in the devices or specifications described herein without notice. Before design-in or order placement, customers are advised to verify that the information is current on which orders or design activities are based. Cyrix warrants its products to conform to current specifications in accordance with Cyrix' standard warranty. Testing is performed to the extent necessary as determined by Cyrix to support this warranty. Unless explicitly specified by customer order requirements, and agreed to in writing by Cyrix, not all device characteristics are necessarily tested. Cyrix assumes no liability, unless specifically agreed to in writing, for customers' product design or infringement of patents or copyrights of third parties arising from the use of Cyrix devices. No license, either express or implied, to Cyrix patents, copyrights, or other intellectual property rights pertaining to any machine or combination of Cyrix devices is hereby granted. Cyrix products are not intended for use in any medical, life saving, or life sustaining system. Information in this document is subject to change without notice.