#### **Preliminary Information**

#### © 1997 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD's Terms and Conditions of Sale for such product.

#### **Trademarks**

AMD, the AMD logo, and the combinations thereof are trademarks of Advanced Micro Devices, Inc.

Am386, Am486, and RISC86 are registered trademarks; K86, AMD-K5, AMD-K6, and the AMD-K6 logo are trademarks of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## **Contents**

| 1 | Introduction                                  | 1    |

|---|-----------------------------------------------|------|

|   | Audience                                      | 1    |

| 2 | CPU Identification Algorithms                 | 3    |

| 3 | AMD-K5 Processor                              | 5    |

|   | BIOS Consideration Checklist                  | 5    |

|   | CPUID                                         | 5    |

|   | CPU Speed Detection                           | 6    |

|   | Model-Specific Registers (MSRs)               | 6    |

|   | Cache Testing                                 | 6    |

|   | SMM Issues                                    | 6    |

|   | AMD-K5 Processor System Management Mode (SMM) | 7    |

|   | Operating Mode and Default Register Values    | 7    |

|   | SMM Initial Register Values                   | 9    |

|   | SMM State-Save Area                           | 9    |

|   | SMM Revision Identifier                       | 12   |

|   | SMM Base Address                              | . 12 |

|   | Auto Halt Restart Slot                        | . 13 |

|   | I/O Trap Dword                                | . 14 |

|   | I/O Trap Restart Slot                         | . 14 |

|   | Exceptions and Interrupts in SMM              | . 16 |

|   | AMD-K5 Processor RESET State                  | . 18 |

|   | Segment Register Attributes                   | . 20 |

|   | State of the AMD-K5 Processor After INIT      | . 20 |

|   | AMD-K5 Processor Test and Debug               | . 21 |

|   | Hardware Configuration Register (HWCR)        | . 22 |

|   | Built-In Self-Test (BIST)                     |      |

|   | Normal BIST                                   |      |

|   | Test Access Port (TAP) BIST                   |      |

|   | Output-Float Test                             | 26   |

21062D/0-April 1997

| Cache and TLB Testing                                                                                                                                                                                                               | 28                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Debug Registers                                                                                                                                                                                                                     | 38                   |

| Branch Tracing                                                                                                                                                                                                                      | 39                   |

| Functional-Redundancy Checking                                                                                                                                                                                                      | 40                   |

| Boundary Scan Architecture Support                                                                                                                                                                                                  | 42<br>42<br>43<br>44 |

| Hardware Debug Tool (HDT)                                                                                                                                                                                                           | 57                   |

| AMD-K5 Processor x86 Architecture Extensions                                                                                                                                                                                        | 57                   |

| Additions to the EFLAGS Register                                                                                                                                                                                                    | 58                   |

| Control Register 4 (CR4) Extensions  Machine-Check Exceptions  4-Mbyte Pages  Global Pages  Virtual-8086 Mode Extensions (VME)  Protected Virtual Interrupt (PVI) Extensions                                                        | 58<br>60<br>60<br>65 |

| Model-Specific Registers (MSRs)  Machine-Check Address Register (MCAR)  Machine-Check Type Register (MCTR)  Time Stamp Counter (TSC)  Array Access Register (AAR)  Hardware Configuration Register (HWCR)  Write Allocate Registers | 80<br>81<br>82       |

| Enable Write Allocate                                                                                                                                                                                                               | 85                   |

| New AMD-K5 Processor Instructions                                                                                                                                                                                                   | 85                   |

| CPUID                                                                                                                                                                                                                               | 86                   |

| CMPXCHG8B                                                                                                                                                                                                                           | 87                   |

| MOV to and from CR4                                                                                                                                                                                                                 | 88                   |

| RDTSC                                                                                                                                                                                                                               | 89                   |

| RDMSR and WRMSR                                                                                                                                                                                                                     | 90                   |

| RSM                                                                                                                                                                                                                                 | 92                   |

| Illegal Instruction (Reserved Opcode)                                                                                                                                                                                               | 93                   |

*iv* Contents

| 6 | AMD-K6™ MMX Processor                            | 95  |

|---|--------------------------------------------------|-----|

|   | BIOS Consideration Checklist                     | 95  |

|   | CPUID                                            | 95  |

|   | CPU Speed Detection                              | 96  |

|   | Model-Specific Registers (MSRs)                  | 96  |

|   | Cache Testing                                    | 96  |

|   | SMM Issues                                       | 96  |

|   | AMD-K6 MMX Processor System Management Mode      | 97  |

|   | Initial Register Values                          | 97  |

|   | SMM State-Save Area                              | 98  |

|   | SMM Revision Identifier                          | 100 |

|   | SMM Base Address                                 | 100 |

|   | Auto Halt Restart                                | 101 |

|   | I/O Trap Dword                                   | 101 |

|   | I/O Trap Restart                                 | 101 |

|   | Exceptions and Interrupts Within SMM             | 101 |

|   | AMD-K6 MMX Processor Reset State                 | 102 |

|   | Segment Register Attributes                      | 103 |

|   | State of the AMD-K6 MMX Processor After INIT     | 104 |

|   | AMD-K6 MMX Processor Cache                       | 104 |

|   | AMD-K6 MMX Processor Test and Debug              | 105 |

|   | Built-In Self-Test (BIST)                        | 106 |

|   | Tri-State Test Mode                              | 106 |

|   | Boundary-Scan Test Access Port (TAP)             |     |

|   | TAP Registers                                    |     |

|   | L1 Cache Inhibit                                 |     |

|   | Purpose                                          |     |

|   | Debug                                            |     |

|   | Debug Registers                                  |     |

|   | AMD-K6 MMX Processor x86 Architecture Extensions |     |

|   | Model-Specific Registers (MSR)                   |     |

|   | Machine-Check Address Register (MCAR)            |     |

|   | Machine-Check Type Register (MCTR)               | 117 |

|   | Test Register 12 (TR12)                          | 118 |

Contents v

#### Preliminary Information

AMD K86<sup>™</sup> Family BIOS and Software Tools Developers Guide

21062D/0-April 1997

|       | Time Stamp Counter (TSC)                | 118 |

|-------|-----------------------------------------|-----|

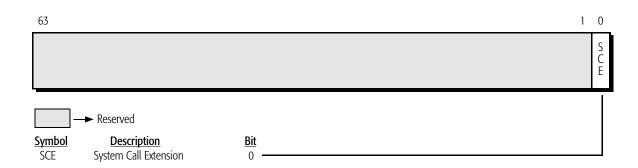

|       | Extended Feature Enable Register (EFER) | 118 |

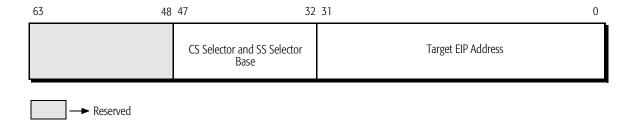

|       | SYSCALL Target Address Register (STAR)  | 118 |

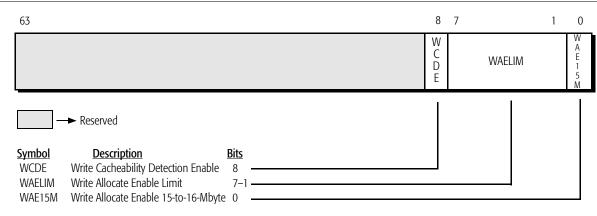

|       | Write Handling Control Register (WHCR)  | 119 |

|       | Machine Check Exception                 | 121 |

|       | New AMD-K6 MMX Processor Instructions   | 122 |

|       | System Call Extensions                  | 122 |

|       | SYSCALL                                 | 123 |

|       | SYSRET                                  | 125 |

|       | Multimedia Extensions (MMX)             | 127 |

| Index |                                         | 120 |

vi Contents

## **List of Figures**

| Figure 1.  | SMM Memory                                                 |

|------------|------------------------------------------------------------|

| Figure 2.  | Hardware Configuration Register (HWCR)23                   |

| Figure 3.  | Array Access Register (AAR)28                              |

| Figure 4.  | Test Formats: Deache Tags for the AMD-K5 Processor         |

| C          | Model 0                                                    |

| Figure 5.  | Test Formats: Deache Tags for the AMD-K5 Processor         |

|            | Model 1 and Greater                                        |

| Figure 6.  | Test Formats: Deache Data for All Models of                |

|            | the AMD-K5 Processor32                                     |

| Figure 7.  | Test Formats: Icache Tags for the AMD-K5 Processor         |

|            | Model 0                                                    |

| Figure 8.  | Test Formats: ICache Tags for the AMD-K5 Processor         |

|            | Model 1 and Greater                                        |

| Figure 9.  | Test Formats: Icache Instructions for the AMD-K5 Processor |

|            | Model 0                                                    |

| Figure 10. | Test Formats: Icache Instructions for the AMD-K5 Processor |

|            | Model 1 and Greater                                        |

| Figure 11. | Test Formats: 4-Kbyte TLB for All Models of                |

|            | the AMD-K5 Processor36                                     |

| Figure 12. | Test Formats: 4-Mbyte TLB for All Models of                |

|            | the AMD-K5 Processor37                                     |

| Figure 13. | Control Register 4 (CR4)                                   |

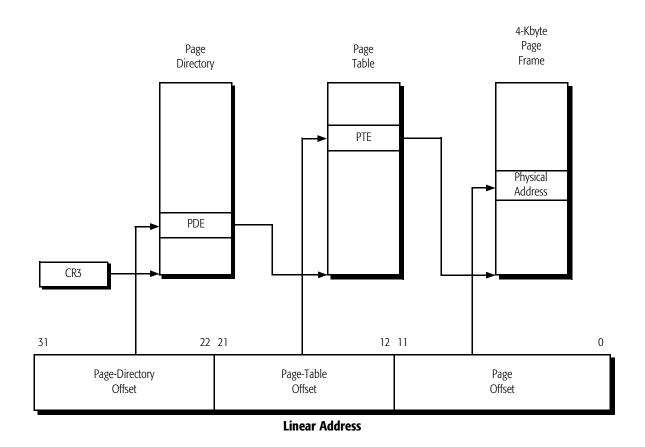

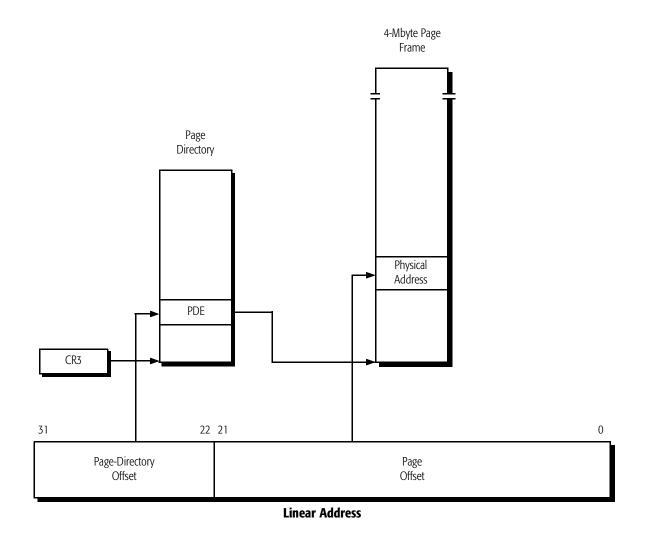

| Figure 14. | 4-Kbyte Paging Mechanism61                                 |

| Figure 15. | 4-Mbyte Paging Mechanism62                                 |

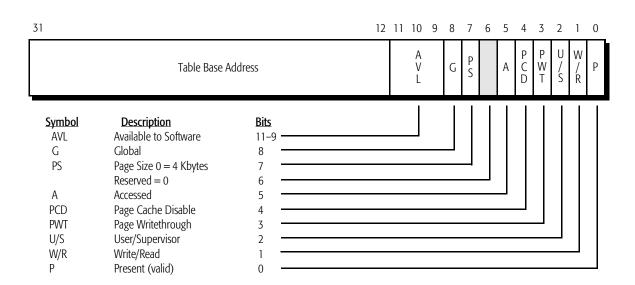

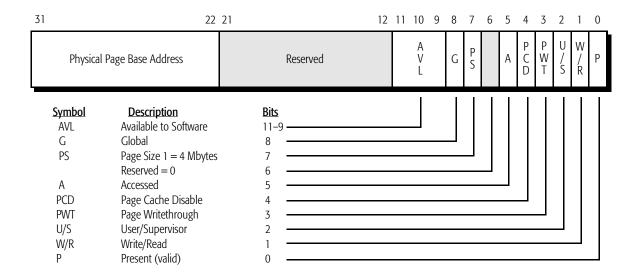

| Figure 16. | Page-Directory Entry (PDE)                                 |

| Figure 17. | Page-Table Entry (PTE)66                                   |

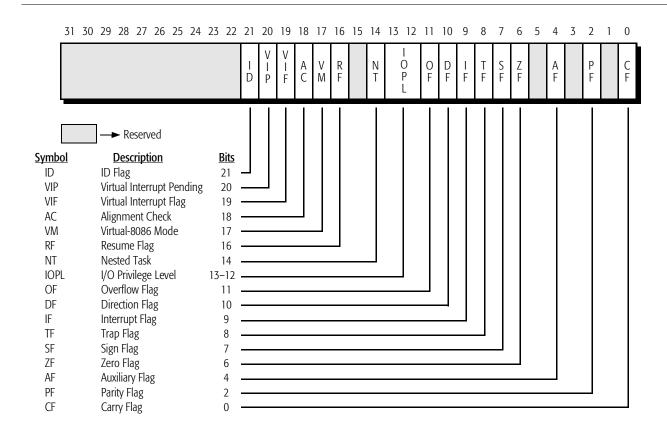

| Figure 18. | EFLAGS Register70                                          |

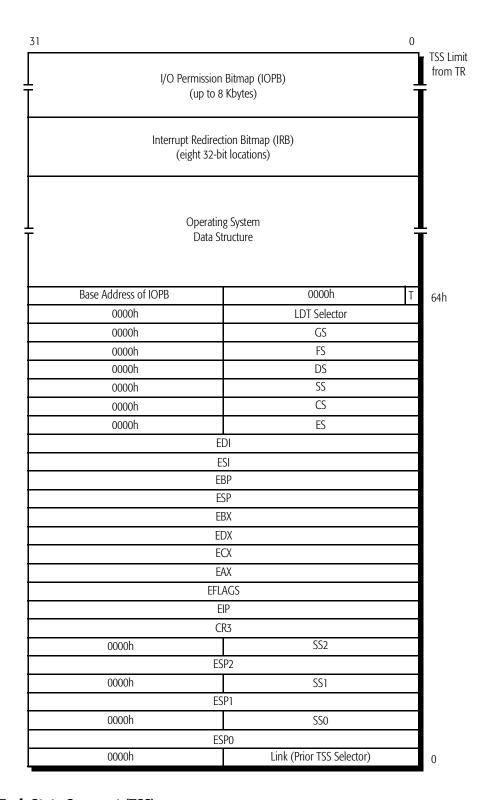

| Figure 19. | Task State Segment (TSS)77                                 |

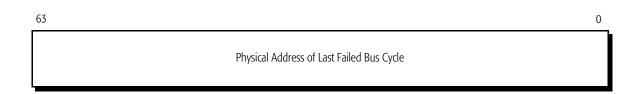

| Figure 20. | Machine-Check Address Register (MCAR) 80                   |

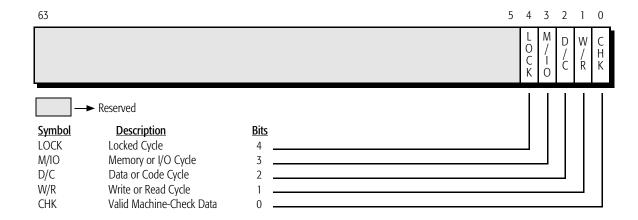

| Figure 21. | Machine-Check Type Register (MCTR)81                       |

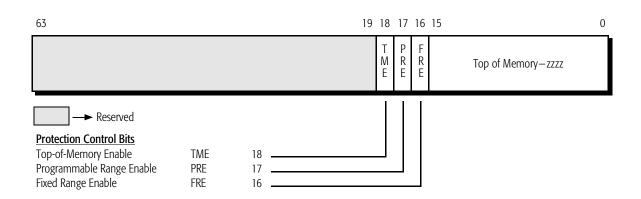

| Figure 22. | Write Allocate Top-of-Memory and Control Register          |

|            | (WATMCR)—MSR 85h                                           |

| Figure 23. | Write Allocate Programmable Memory Range Register          |

|            | (WAPMRR)—MSR 86h84                                         |

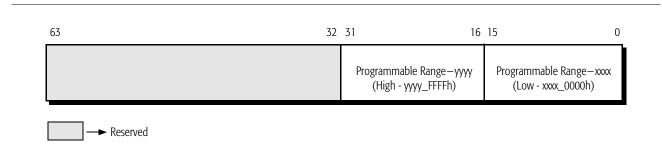

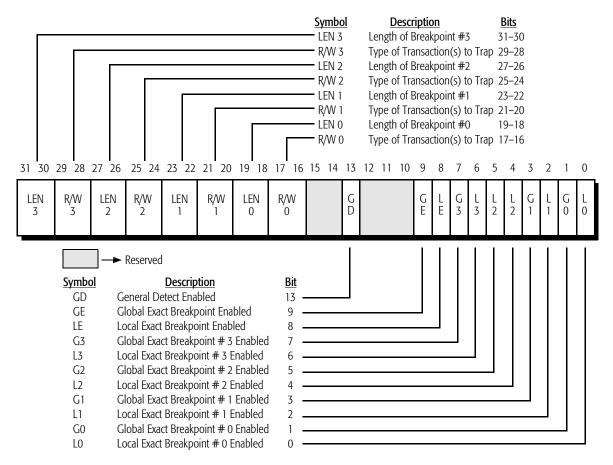

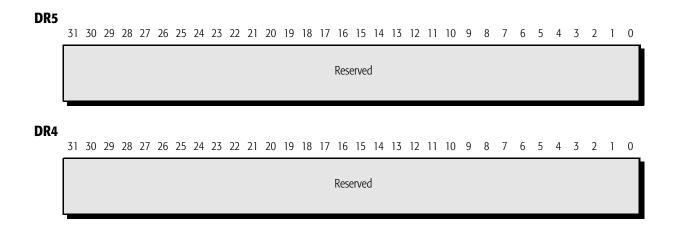

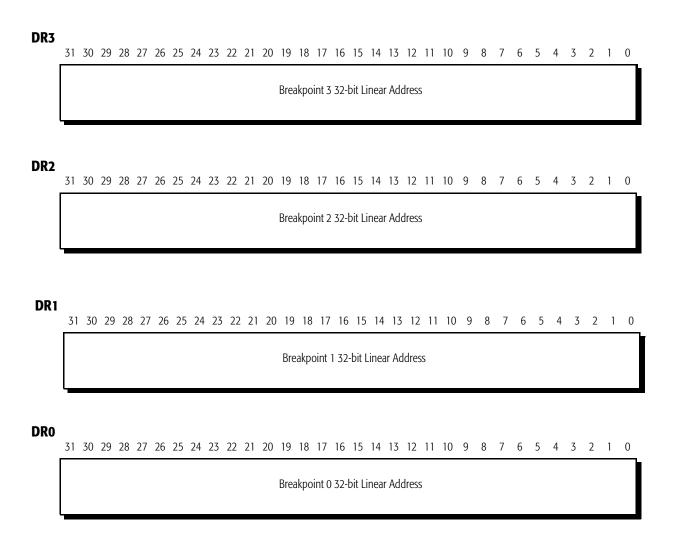

| Figure 24. | Debug Register DR7114                                      |

| Figure 25. | Debug Register DR6115                                      |

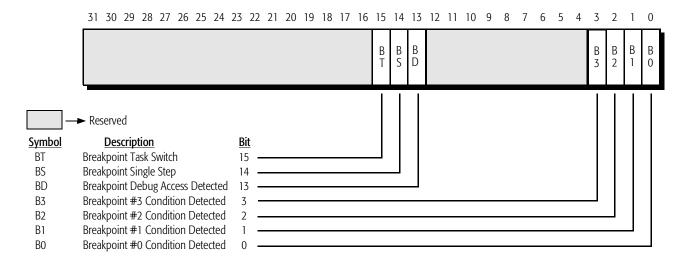

| Figure 26. | Debug Registers DR5 and DR4115                             |

| Figure 27. | Debug Registers DR3, DR2, DR1, and DR0116                  |

List of Figures vii

#### **Preliminary Information**

| Α | M | DД |

|---|---|----|

|---|---|----|

| <i>AMD K86</i> ™ | Famil | v BIOS and | <i>Software</i> | Tools | <b>Developers</b> | Guide |

|------------------|-------|------------|-----------------|-------|-------------------|-------|

|                  |       |            |                 |       |                   |       |

21062D/0-April 1997

| Figure 28. | Extended Feature Enable Register (EFER) | 18 |

|------------|-----------------------------------------|----|

| Figure 29. | SYSCALL Target Address Register (STAR)  | 19 |

| Figure 30. | Write Handling Control Register (WHCR)— |    |

|            | MSR C000 0082h                          | 20 |

viii List of Figures

## **List of Tables**

| Table 1.  | Summary of AMD-K5 Processor CPU IDs and BIOS Boot Strings |

|-----------|-----------------------------------------------------------|

| Table 2.  | Summary of AMD-K6 MMX Processor CPU IDs and               |

| Table 2.  | BIOS Boot Strings                                         |

| Table 3.  | Initial State of Registers in SMM                         |

| Table 4.  | SMM State-Save Area Map                                   |

| Table 5.  | SMM Revision Identifier Fields                            |

| Table 6.  | I/O Trap Dword Fields                                     |

| Table 7.  | I/O Trap Restart Slot                                     |

| Table 8.  | Summary of Interrupts and Exceptions                      |

| Table 9.  | State of the AMD-K5 Processor After RESET18               |

| Table 10. | Segment Register Attribute Fields Initial Values          |

| Table 11. | Hardware Configuration Register (HWCR) Fields23           |

| Table 12. | BIST Error Bit Definition in EAX Register                 |

| Table 13. | Array IDs in Array Pointers29                             |

| Table 14. | Branch-Trace Message Special Bus Cycle Fields39           |

| Table 15. | AMD-K5 Processor Device Identification Register45         |

| Table 16. | Public TAP Instructions46                                 |

| Table 17. | Control Bit Definitions49                                 |

| Table 18. | Boundary Scan Register Bit Definitions49                  |

| Table 19. | Control Register 4 (CR4) Fields                           |

| Table 20. | Page-Directory Entry (PDE) Fields64                       |

| Table 21. | Page-Table Entry (PTE) Fields                             |

| Table 22. | Virtual-Interrupt Additions to EFLAGS Register71          |

| Table 23. | Instructions that Modify the IF or VIF Flags—Real Mode 71 |

| Table 24. | Instructions that Modify the IF or VIF Flags—Protected    |

|           | Mode                                                      |

| Table 25. | Instructions that Modify the IF or VIF Flags—Virtual-8086 |

|           | Mode                                                      |

| Table 26. | Instructions that Modify the IF or VIF Flags—Virtual-8086 |

|           | Mode Interrupt Extensions (VME)74                         |

| Table 27. | Instructions that Modify the IF or VIF Flags—Protected    |

|           | Mode Virtual Interrupt Extensions (PVI)                   |

| Table 28. | Interrupt Behavior and Interrupt-Table Access             |

| Table 29. | Machine-Check Type Register (MCTR) Fields 81              |

| Table 30. | Initial State of Registers in SMM97                       |

| Table 31. | AMD-K6 MMX Processor State-Save Map98                     |

| Table 32. | SMM Revision Identifier                                   |

| Table 33. | AMD-K6 MMX Processor I/O Trap Dword Configuration 101     |

| Table 34. | State of the AMD-K6 MMX Processor After RESET 102         |

| Table 35. | Data Returned by the CPUID Instruction                    |

| Table 36. | Boundary Scan Register Bit Definitions                    |

| Table 37. | AMD-K6 MMX Processor Device Identification Register 110   |

List of Tables ix

#### **Preliminary Information**

#### AMD K86<sup>™</sup> Family BIOS and Software Tools Developers Guide

21062D/0-April 1997

| Table 38. | Supported TAP Instructions                         | 111 |

|-----------|----------------------------------------------------|-----|

| Table 39. | DR7 LEN and RW Definitions                         | 114 |

| Table 40. | Extended Feature Enable Register (EFER) Definition | 118 |

| Table 41. | SYSCALL Target Address Register (STAR) Definition  | 119 |

| Table 42. | MMX Instructions and Descriptions                  | 127 |

x List of Tables

## **Revision History**

| Date                                                                                                                                                                                                                                                              | Rev                                | Description     |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|--|--|--|--|

| Sept 1996                                                                                                                                                                                                                                                         | Α                                  | Initial Release |  |  |  |  |

| Mar 1997 B Added write allocation information for K86 family of processors. See "Write Allocate Regist page 82 for information about the AMD-K5 processor and "Write Handling Control Registe (WHCR)" on page 119 for information about the AMD-K6 MMX processor. |                                    |                 |  |  |  |  |

| Mar 1997 B Added Test and Debug section for the AMD-K6 MMX processor. See "AMD-K6™ MMX Processor Test and Debug" on page 105 for more information.                                                                                                                |                                    |                 |  |  |  |  |

| Mar 1997                                                                                                                                                                                                                                                          | ar 1997 C Reorganized entire guide |                 |  |  |  |  |

| Apr 1997 D Changed BIOS boot string for the AMD-K6 MMX processor in Table 2, "Summary of MMX Processor CPU IDs and BIOS Boot Strings," on page 4.                                                                                                                 |                                    |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                   |                                    |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                   |                                    |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                   |                                    |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                   |                                    |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                   |                                    |                 |  |  |  |  |

Revision History xi

21062D/0-April 1997

xii Revision History

1

## Introduction

This document highlights the BIOS and software modifications required to fully support the  $K86^{\text{TM}}$  family of processors, which includes the AMD- $K5^{\text{TM}}$  processor and the AMD- $K6^{\text{TM}}$  MMX processor.

There can be more than one way to implement the functionality detailed in this document, and the information provided is for demonstration purposes.

#### **Audience**

It is assumed that the reader possesses the proper knowledge of the K86 processors, the x86 architecture, and programming requirements to understand the information presented in this document.

Introduction 1

21062D/0-April 1997

2 Introduction

2

# CPU Identification Algorithms

The CPUID instruction provides complete information about the processor (vendor, type, name, etc.) and its capabilities (features). After detecting the processor and its capabilities, software can be accurately tuned to the system for maximum performance and benefit to users. For example, game software can test the performance level available from a particular processor by detecting the type or speed of the processor. If the performance level is high enough, the software can enable additional capabilities or more advanced algorithms. Another example involves testing for the presence of multimedia extensions (MMX) on the processor. If the software finds this feature present when it checks the feature bits, it can utilize these more powerful extensions for better performance on new multimedia software.

For more detailed information refer to the *AMD Processor Recognition Application Note*, order# #20734, located at http://www.amd.com

Tables 1 and 2 outline the family codes and model codes for the AMD K86 processors. Table 1 shows the CPU speed, the 'P-Rating', and the recommended BIOS boot-string associated with each AMD-K5 processor.

Table 2 shows the recommended BIOS boot-string for the AMD-K6 MMX processor. This recommended boot-string is 'AMD-K6/XXX'. The value for XXX is determined by

calculating the core frequency of the processor. Use the Time Stamp Counter (TSC) to 'clock' a timed operation and compare the result to the Real Time Clock (RTC) to determine the operating frequency.

**Note:** Tables 1 and 2 contain information intended to prepare the infrastructure for potential future products. These products may or may not be announced, but BIOS software should be prepared to support these options.

Table 1. Summary of AMD-K5™ Processor CPU IDs and BIOS Boot Strings

| Instruction<br>Family Code | Model<br>Code | CPU Speed<br>(MHz) | CPU Bus<br>Speed<br>(MHz) | Recommended<br>BIOS Boot-String | CPUID Functions 8000_0002, 3, 4<br>Return Values |

|----------------------------|---------------|--------------------|---------------------------|---------------------------------|--------------------------------------------------|

|                            |               | 75                 | 50                        | AMD-K5-PR75                     | undefined                                        |

|                            | 0             | 90                 | 60                        | AMD-K5-PR90                     | undefined                                        |

|                            |               | 100                | 66                        | AMD-K5-PR100                    | undefined                                        |

| 5                          | 1             | 90                 | 60                        | AMD-K5-PR120                    | AMD-K5(tm) Processor                             |

| (AMD-K5 Processor)         | '             | 100                | 66                        | AMD-K5-PR133                    | AMD-K5(tm) Processor                             |

|                            | 2             | 105                | 60                        | AMD-K5-PR150                    | AMD-K5(tm) Processor                             |

|                            |               | 116.7              | 66                        | AMD-K5-PR166                    | AMD-K5(tm) Processor                             |

|                            | 3             | 133                | 66                        | AMD-K5-PR200                    | AMD-K5(tm) Processor                             |

Table 2. Summary of AMD-K6™ MMX Processor CPU IDs and BIOS Boot Strings

| Instruction<br>Family Code | Model<br>Code | CPU<br>Speed<br>(MHz) | CPU Bus<br>Speed<br>(MHz) | Recommended BIOS Boot-String Display |

|----------------------------|---------------|-----------------------|---------------------------|--------------------------------------|

| 5                          | 6             | TBD                   | 60                        | AMD-K6/XXX                           |

| (AMD-K6 MMX Processor)     | 0             | TBD                   | 66                        | AMD-K6/XXX                           |

3

## AMD-K5<sup>TM</sup> Processor

The AMD-K5 processor is socket 7-compatible and software-compatible with Pentium. Compatible in this sense means the devices are pin-for-pin compatible and that the same software can be executed on both processors with no software modifications.

The BIOS for the AMD-K5 processor requires minimal changes to fully support the AMD-K5 processor family.

#### **BIOS Consideration Checklist**

#### **CPUID**

- Use the CPUID instruction to properly identify the AMD-K5 processor.

- Determine the processor type, stepping and features using functions 0000\_0001h and 8000\_0001h of the CPUID instruction.

- Boot-up display: The processor name is retrieved using CPUID extended functions 8000\_0002h, 8000\_0003h, and 8000\_0004h. See "CPU Identification Algorithms" on page 3 for more information.

21062D/0-April 1997

#### **CPU Speed Detection**

- Use speed detection algorithms that do not rely on repetitive instruction sequences.

- Use the Time Stamp Counter (TSC) to 'clock' a timed operation and compare the result to the Real Time Clock (RTC) to determine the operating frequency. See the example of frequency-determination assembler code available on the AMD website at http://www.amd.com.

- Display the P-Rating shown in Table 1, "Summary of AMD-K5<sup>TM</sup> Processor CPU IDs and BIOS Boot Strings," on page 4.

#### **Model-Specific Registers (MSRs)**

- Access only MSRs implemented in the AMD-K5 processor.

- Program the write allocate registers—Hardware Configuration Register (HWCR), Write Allocate Top-of-Memory and Control Register (WATMCR), and Write Programmable Memory Range (WAPMRR). See "Write Allocate Registers" on page 82 and the Implementation of Write Allocate in the K86<sup>TM</sup> Processors Application Note, order# 21326 for more information.

#### **Cache Testing**

■ Perform cache testing on the AMD-K5 processor using the Array Access Register MSR. See "Array Access Register (AAR)" on page 28 for more information.

#### **SMM Issues**

- The System Management Mode (SMM) functionality of the AMD-K5 processor is identical to Pentium.

- Implement the AMD-K5 processor SMM state-save area in the same manner as Pentium except for the IDT Base and possibly Pentium-reserved areas. See "AMD-K5<sup>™</sup> Processor System Management Mode (SMM)" on page 7 for more information.

## AMD-K5™ Processor System Management Mode (SMM)

System Management Mode (SMM) is an alternate operating mode entered by way of a system management interrupt (SMI) and handled by an interrupt service routine. SMM is designed for system control activities such as power management. These activities appear transparent to conventional operating systems like DOS and Windows. SMM is primarily targeted for use by the Basic Input Output System (BIOS) and specialized low-level device drivers. The code and data for SMM are stored in the SMM memory area, which is isolated from main memory.

The processor enters SMM by the system logic's assertion of the  $\overline{SMI}$  interrupt and the processor's acknowledgment by the assertion of  $\overline{SMIACT}$ . At this point the processor saves its state into the SMM memory state-save area and jumps to the SMM service routine. The processor returns from SMM when it executes the RSM (resume) instruction from within the SMM service routine. Subsequently, the processor restores its state from the SMM save area, de-asserts  $\overline{SMIACT}$ , and resumes execution with the instruction following the point where it entered SMM.

The following sections summarize the SMM state-save area, entry into and exit from SMM, exceptions and interrupts in SMM, memory allocation and addressing in SMM, and the  $\overline{\text{SMI}}$  and  $\overline{\text{SMIACT}}$  signals.

#### **Operating Mode and Default Register Values**

The software environment within SMM has the following characteristics:

- Addressing and operation in Real mode

- 4-Gbyte segment limits

- Default 16-bit operand, address, and stack sizes, although instruction prefixes can override these defaults

- Control transfers that do not override the default operand size truncate the EIP to 16 bits

- Far jumps or calls cannot transfer control to a segment with a base address requiring more than 20 bits, as in Real mode segment-base addressing

- A20M is masked

- Interrupt vectors use the Real-mode interrupt vector table

- The IF flag in EFLAGS is cleared (INTR not recognized)

- The TF flag in EFLAGS is cleared

- The NMI and INIT interrupts are disabled

- Debug register DR7 is cleared (debug traps disabled)

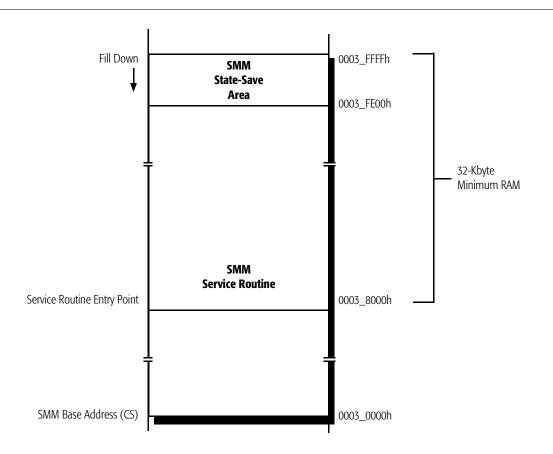

Figure 1 shows the default map of the SMM memory area. It consists of a 64-Kbyte area, between 0003\_0000h and 0003\_FFFFh, of which the top 32 Kbytes (0003\_8000h to 0003\_FFFFh) must be populated with RAM. The default code-segment (CS) base address for the area—called the SMM base address—is at 0003\_0000h. The top 512 bytes (0003\_FE00h to 0003\_FFFFh) contain a fill-down SMM state-save area. The default entry point for the SMM service routine is 0003\_8000h.

Figure 1. SMM Memory

#### **SMM Initial Register Values**

Table 3 shows the initial state of registers when entering SMM.

Table 3. Initial State of Registers in SMM

| Dominton                  | Initial Contents                                                            |            |          |  |

|---------------------------|-----------------------------------------------------------------------------|------------|----------|--|

| Register                  | Selector                                                                    | Base       | Limit    |  |

| CS                        | 3000h                                                                       | 0003_0000h | 4 Gbytes |  |

| DS                        | 0000h                                                                       | 0000_0000h | 4 Gbytes |  |

| ES                        | 0000h                                                                       | 0000_0000h | 4 Gbytes |  |

| FS                        | 0000h                                                                       | 0000_0000h | 4 Gbytes |  |

| GS                        | 0000h                                                                       | 0000_0000h | 4 Gbytes |  |

| SS                        | 0000h                                                                       | 0000_0000h | 4 Gbytes |  |

| General-Purpose Registers | Unmodified                                                                  |            | ·        |  |

| EFLAGS                    | 0000_0002h                                                                  |            |          |  |

| EIP                       | 0000_8000h                                                                  |            |          |  |

| CRO                       | Bits 0, 2, 3, and 31 cleared (PE, EM, TS, and PG); remainder are unmodified |            |          |  |

| CR4                       | 0000_0000h                                                                  |            |          |  |

| GDTR                      | Unmodified                                                                  |            |          |  |

| LDTR                      |                                                                             | Unmodified |          |  |

| IDTR                      | Unmodified                                                                  |            |          |  |

| TR                        | Unmodified                                                                  |            |          |  |

| DR7                       | 0000_0400h                                                                  |            |          |  |

| DR6                       | Undefined                                                                   |            |          |  |

#### **SMM State-Save Area**

When the processor acknowledges an SMI interrupt by asserting SMIACT, it saves its state in the 512-byte SMM state-save area shown in Table 4. The save begins at the top of the SMM memory area (SMM Base Address + FFFFh) and fills down to SMM base address + FE00h.

Table 4 shows the offsets in the SMM state-save area relative to the SMM base address. The SMM service routine can alter any of the read and write values in the state-save area. The contents of any reserved locations in the state-save area are not necessarily the same between the AMD-K5 processor and Pentium or 486 processors.

21062D/0-April 1997

Table 4. SMM State-Save Area Map

| Offset (Hex) | Contents         |

|--------------|------------------|

| FFFC         | CRO              |

| FFF8         | CR3              |

| FFF4         | EFLAGS           |

| FFF0         | EIP              |

| FFEC         | EDI              |

| FFE8         | ESI              |

| FFE4         | EBP              |

| FFE0         | ESP              |

| FFDC         | EBX              |

| FFD8         | EDX              |

| FFD4         | ECX              |

| FFD0         | EAX              |

| FFCC         | DR6 (FFFF_CFF3h) |

| FFC8         | DR7              |

| FFC4         | TR               |

| FFC0         | LDTR             |

| FFBC         | GS               |

| FFB8         | FS               |

| FFB4         | DS               |

| FFB0         | SS               |

| FFAC         | CS               |

| FFA8         | ES               |

| FFA4         | I/O Trap Dword   |

| FFA0         | reserved         |

| FF9C         | I/O Trap EIP     |

| FF98         | reserved         |

| FF94         | reserved         |

| FF90         | IDT Base         |

| FF8C         | IDT Limit        |

| FF88         | GDT Base         |

| FF84         | GDT Limit        |

| FF80         | TSS Attributes   |

| FF7C         | TSS Base         |

| FF78         | TSS Limit        |

Table 4. SMM State-Save Area Map (continued)

| of the same state-save Area map (continued) |                         |  |

|---------------------------------------------|-------------------------|--|

| Offset (Hex)                                | Contents                |  |

| FF74                                        | LDT Attributes          |  |

| FF70                                        | LDT Base                |  |

| FF6C                                        | LDT Limit               |  |

| FF68                                        | GS Attributes           |  |

| FF64                                        | GS Base                 |  |

| FF60                                        | GS Limit                |  |

| FF5C                                        | FS Attributes           |  |

| FF58                                        | FS Base                 |  |

| FF54                                        | FS Limit                |  |

| FF50                                        | DS Attributes           |  |

| FF4C                                        | DS Base                 |  |

| FF48                                        | DS Limit                |  |

| FF44                                        | SS Attributes           |  |

| FF40                                        | SS Base                 |  |

| FF3C                                        | SS Limit                |  |

| FF38                                        | CS Attributes           |  |

| FF34                                        | CS Base                 |  |

| FF30                                        | CS Limit                |  |

| FF2C                                        | ES Attributes           |  |

| FF28                                        | ES Base                 |  |

| FF24                                        | ES Limit                |  |

| FF20                                        | reserved                |  |

| FF1C                                        | reserved                |  |

| FF18                                        | reserved                |  |

| FF14                                        | CR2                     |  |

| FF10                                        | CR4                     |  |

| FF0C                                        | I/O Restart ESI         |  |

| FF08                                        | I/O Restart ECX         |  |

| FF04                                        | I/O Restart EDI         |  |

| FF02                                        | Halt Restart Slot       |  |

| FF00                                        | I/O Trap Restart Slot   |  |

| FEFC                                        | SMM Revision Identifier |  |

| FEF8                                        | SMM Base Address        |  |

| FE00-FEF4                                   | reserved                |  |

AMD-K5<sup>™</sup> Processor

#### **SMM Revision Identifier**

The SMM revision identifier at offset FEFCh in the SMM state-save area specifies the version of SMM and the extensions available on the processor. The SMM revision identifier fields, shown in Table 5, are as follows:

- Bits 31–18—reserved

- *Bit 17*—SMM base address relocation (always 1 = enabled)

- *Bit 16*—I/O trap restart (always 1 = enabled)

- Bits 15-0—SMM revision level = 0000

**Table 5. SMM Revision Identifier Fields**

| Bits 31-18 | Bit 17              | Bit 16             | Bits 15-0          |

|------------|---------------------|--------------------|--------------------|

| Reserved   | SMM Base Relocation | I/O Trap Extension | SMM Revision Level |

| 0          | 1                   | 1                  | 0000               |

**Note:** The I/O trap restart and the SMM base address relocation functions are always enabled in the AMD-K5 processor and do not need to be specifically enabled.

#### **SMM Base Address**

During RESET, the processor sets the code-segment (CS) base address for the SMM memory area—the SMM base address—to its default, 0003\_0000h. The SMM base address at offset FEF8h in the SMM state-save area can be changed by the SMM service routine to any address aligned to a 32-Kbyte boundary. (Locations not aligned to a 32-Kbyte boundary cause the processor to enter the Shutdown state when executing the RSM instruction.)

In some operating environments it may be desirable to relocate the 64-Kbyte SMM memory area to a high memory area to provide more low memory for legacy software. During system initialization, the base of the 64-Kbyte SMM memory area is relocated by the BIOS. To relocate the SMM base address, the system enters the SMM handler at the default address. This handler changes the SMM base address location in the SMM state-save area, copies the SMM handler to the new location, and exits SMM.

The next time SMM is entered, the processor saves its state at the new base address. This new address is used for every SMM until the SMM base address in the SMM state-save area is changed or a hardware reset occurs.

#### **Auto Halt Restart Slot**

During entry into SMM, the halt restart slot at offset FF02h in the SMM state-save area indicates whether SMM was entered from the Halt state. Before returning from SMM, the halt restart slot can be written to by the SMM service routine to specify whether the return from SMM should take the processor back to the Halt state or to the instruction-execution state specified by the SMM state-save area.

On entry into SMM, the halt restart slot is configured as follows:

- Bits 15–1—Undefined

- *Bit 0*—Point of entry to SMM:

- 1 = entered from Halt state

- 0 = not entered from Halt state

After entry into the SMI handler and before returning from SMM, the halt restart slot can be written using the following definition:

- Bits 15–1—Undefined

- Bit 0—Point of return from SMM

- 1 = return to Halt state

- 0 = return to state specified by SMM state-save area

If the return from SMM takes the processor back to the Halt state, the HLT instruction is not re-executed, but the Halt special bus cycle is driven on the bus after the return.

21062D/0-April 1997

#### I/O Trap Dword

If the assertion of SMI is recognized on the boundary of an I/O instruction, the I/O trap dword at offset FFA4h in the SMM state-save area contains information about the instruction. The fields of the I/O trap dword, shown in Table 6, are configured as follows:

- *Bits 31–16*—I/O port address

- *Bit 15*—I/O string operation (1 = string, 0 = non-string)

- Bits 14–2—reserved

- Bit 1—Valid I/O instruction (1 = valid, 0 = invalid)

- *Bit 0*—Input or output instruction (1 = INx, 0 = OUTx)

Table 6. I/O Trap Dword Fields

| Bits 31-16       | Bit 15               | Bit 14-2 | Bit 1                 | Bit 0           |

|------------------|----------------------|----------|-----------------------|-----------------|

| I/O Port Address | I/O String Operation | Reserved | Valid I/O Instruction | Input or Output |

The I/O trap dword is related to the I/O trap restart slot, described below. Bit 1 of the I/O trap dword (the valid bit) should be tested if the I/O trap restart slot is to be changed.

#### I/O Trap Restart Slot

The I/O trap restart slot at offset FF00h in the SMM state-save area specifies whether the trapped I/O instruction should be re-executed on return from SMM. This slot in the state-save area is called the I/O instruction restart function. Re-executing a trapped I/O instruction is useful, for example, if an I/O write occurs to a disk that is powered down. The system logic monitoring such an access can assert  $\overline{\text{SMI}}$ . Then the SMM service routine can query the system logic, detect a failed I/O write, take action to power-up the I/O device, enable the I/O trap restart slot feature, and return from SMM.

The fields of the I/O trap restart slot are defined as follows:

- Bits 31–16—reserved

- *Bits 15–0*—I/O instruction restart on return from SMM:

0000h = execute the next instruction after the trapped I/O instruction

00FFh = re-execute the trapped I/O instruction

Table 7 shows the format of the I/O trap restart slot.

Table 7. I/O Trap Restart Slot

| 31-16    | 15-0                                                                     |

|----------|--------------------------------------------------------------------------|

|          | I/O Instruction restart on return from SMM:                              |

| Reserved | ■ 0000h = execute the next instruction after the trapped I/O instruction |

|          | ■ 00FFh = re-execute the trapped I/O instruction                         |

The processor initializes the I/O trap restart slot to 0000h upon entry into SMM. If SMM is entered as a result of a trapped I/O instruction, the processor indicates the validity of the I/O instruction by setting or clearing bit 1 of the I/O trap dword at offset FFA4h in the SMM state-save area. The SMM service routine should test bit 1 of the I/O trap dword to determine if a valid I/O instruction was being executed when entering SMM and before writing the I/O trap restart slot. If the I/O instruction is valid, the SMM service routine can safely rewrite the I/O trap restart slot with the value 00FFh, causing the processor to re-execute the trapped I/O instruction when the RSM instruction is executed. If the I/O instruction is invalid, writing the I/O trap restart slot has undefined results.

If a second SMI is asserted and a valid I/O instruction was trapped by the first SMM handler, the CPU services the second SMI prior to re-executing the trapped I/O instruction. The second entry into SMM never has bit 1 of the I/O trap dword set, and the second SMM service routine must not rewrite the I/O trap restart slot.

During a simultaneous SMI I/O instruction trap and debug breakpoint trap, the AMD-K5 processor first responds to the SMI and postpones recognizing the debug exception until after returning from SMM via the RSM instruction. If the debug registers DR3-DR0 are used while in SMM, they must be saved

21062D/0-April 1997

and restored by the SMM handler. The processor automatically saves and restores DR7–DR6. If the I/O trap restart slot in the SMM state-save area contains the value 00FFh when the RSM instruction is executed, the debug trap does not occur until after the I/O instruction is re-executed.

#### **Exceptions and Interrupts in SMM**

When SMM is entered, the processor disables both INTR and NMI interrupts. The processor disables INTR interrupts by clearing the IF flag in the EFLAGS register. To enable INTR interrupts within SMM, the SMM handler must set the IF flag to 1.

Generating an INTR interrupt is a method for unmasking NMI interrupts in SMM. The processor recognizes the assertion of NMI within SMM immediately after the completion of an IRET. The NMI can thus be enabled by using a dummy INTR interrupt. Once NMI is recognized within SMM, NMI recognition remains enabled until SMM is exited, at which point NMI masking is restored to the state it was in before entering SMM.

Because the IF flag is cleared when entering SMM, the HLT instruction should not be executed in SMM without first setting the IF bit to 1. Setting this bit to 1 enables the processor to exit the Halt state by means of an INTR interrupt.

Table 8 summarizes the behavior of all interrupts in SMM.

**Table 8. Summary of Interrupts and Exceptions**

| Priority | Description                                                    | Туре       | Sampling⁵       | Vector <sup>1</sup> | Acknowledgment                                  | Point of Interruptibility                                                        |

|----------|----------------------------------------------------------------|------------|-----------------|---------------------|-------------------------------------------------|----------------------------------------------------------------------------------|

| 1        | INTn instruc-<br>tions and all<br>other software<br>exceptions | exceptions | internal        | 0-255               | none                                            | Entry to service routine                                                         |

| 2        | BUSCHK                                                         | interrupt  | level-sensitive | 18 <sup>2</sup>     | none                                            | Entry to service routine <sup>2</sup>                                            |

| 3        | R/S                                                            | interrupt  | level-sensitive | none                | PRDY                                            | Negation of PRDY                                                                 |

| 4        | FLUSH                                                          | interrupt  | edge-triggered⁴ | none                | FLUSH-Acknowl-<br>edge special<br>bus cycle     | BRDY of FLUSH<br>Acknowledge bus cycle                                           |

| 5        | SMI                                                            | interrupt  | edge-triggered⁴ | SMM <sup>3</sup>    | SMIACT                                          | Entry to SMM service routine <sup>7</sup>                                        |

| 6        | INIT                                                           | interrupt  | edge-triggered⁴ | BIOS                | none                                            | Completion of initialization                                                     |

| 7        | NMI                                                            | interrupt  | edge-triggered⁴ | 2                   | none                                            | NMI interrupts: IRET from service routine. All others: Entry to service routine. |

| 8        | INTR                                                           | interrupt  | level-sensitive | 0-255               | Interrupt acknowl-<br>edge special<br>bus cycle | Entry to service routine                                                         |

| 9        | STPCLK                                                         | interrupt  | level-sensitive | none                | Stop-Grant special bus cycle                    | Negation of STPCLK                                                               |

#### Notes:

- 1. For interrupts with vectors, the processor saves its state prior to accessing the service routine and changing the program flow. Interrupts without vectors do not change program flow; instead, they simply pause program flow for the duration of the interrupt function and return to where they left off.

- 2. If the Machine Check Enable (MCE) bit in CR4 is set to 1.

- 3. The entry point for the SMI interrupt handler is at offset 8000h from the SMM Base Address.

- 4. Only the edge-triggered interrupts are latched when asserted. All interrupts are recognized at the next instruction retirement boundary.

- 5. If a bus cycle is in progress, EWBE must be asserted before the interrupt is recognized.

- 6. For external interrupts (most exceptions, by contrast, are recognized when they occur). External interrupts are recognized at instruction boundaries. When MOV or POP instructions load SS, interruptibility is delayed until after the next instruction, thus allowing both SS and the corresponding SP to load.

- 7. After assertion of SMI, subsequent assertions of SMI are masked to prevent recursive entry into SMM. However, other exceptions or interrupts (except INIT and NMI) are taken in the SMM service routine.

#### **AMD-K5™ Processor RESET State**

The state of all architecture registers and Model-Specific Registers (MSRs) after the AMD-K5 processor has completed its initialization due to the recognition of the assertion of RESET are shown in Table 9.

Table 9. State of the AMD-K5™ Processor After RESET

| Register | RESET State                | Notes |

|----------|----------------------------|-------|

| GDTR     | base:0000_0000 limit:0000h |       |

| IDTR     | base:0000_0000 limit:0000h |       |

| TR       | 0000h                      |       |

| LDTR     | 0000h                      |       |

| EIP      | FFFF_FFF0h                 |       |

| EFLAGS   | 0000_0002h                 |       |

| EAX      | 0000_0000h                 | 1     |

| EBX      | 0000_0000h                 |       |

| ECX      | 0000_0000h                 |       |

| EDX      | 0000_05XXh                 | 2     |

| ESI      | 0000_0000h                 |       |

| EDI      | 0000_0000h                 |       |

| EBP      | 0000_0000h                 |       |

| ESP      | 0000_0000h                 |       |

| CS       | F000h                      |       |

| SS       | 0000h                      |       |

| DS       | 0000h                      |       |

| ES       | 0000h                      |       |

| FS       | 0000h                      |       |

| GS       | 0000h                      |       |

#### Notes:

- 1. The contents of EAX indicate if BIST was successful. If EAX = 0000\_0000h, then BIST was successful. If EAX is non-zero, BIST failed.

- 2. EDX contains the AMD-K5 processor signature, which is comprised of the instruction family, model, and stepping.

- 3. These MSRs are described in "AMD-K5™ Processor x86 Architecture Extensions" on page 57.

- 4. The AMD-K5 processor supports write allocate only on Models 1, 2, and 3, with a Stepping of 4 or greater.

Table 9. State of the AMD-K5™ Processor After RESET (continued)

| Register                       | RESET State               | Notes |

|--------------------------------|---------------------------|-------|

| FPU Stack R7–R0                | 0000_0000_0000_0000_0000h |       |

| FPU Control Word               | 0040h                     |       |

| FPU Status Word                | 0000h                     |       |

| FPU Tag Word                   | 5555h                     |       |

| <b>FPU Instruction Pointer</b> | 0000_0000_0000h           |       |

| FPU Data Pointer               | 0000_0000_0000h           |       |

| FPU Opcode Register            | 000_0000_0000b            |       |

| CR0                            | 6000_0010h                |       |

| CR2                            | 0000_0000h                |       |

| CR3                            | 0000_0000h                |       |

| CR4                            | 0000_0000h                |       |

| DR7                            | 0000_0400h                |       |

| DR6                            | FFFF_0FF0h                |       |

| DR3                            | 0000_0000h                |       |

| DR2                            | 0000_0000h                |       |

| DR1                            | 0000_0000h                |       |

| DRO                            | 0000_0000h                |       |

| MCAR                           | 0000_0000_0000_0000h      |       |

| MCTR                           | 0000_0000_0000_0000h      |       |

| TR12                           | 0000_0000_0000_0000h      |       |

| TSC                            | 0000_0000_0000_0000h      |       |

| AAR                            | 0000_0000_0000_0000h      | 3     |

| HWCR                           | 0000_0000_0000_0000h      | 3     |

| WATMCR                         | 0000_0000_0000_0000h 3,   |       |

| WAPMRR                         | 0000_0000_000F_000Ah      | 3, 4  |

#### Notes

- The contents of EAX indicate if BIST was successful. If EAX = 0000\_0000h, then BIST was successful. If EAX is non-zero, BIST failed.

- 2. EDX contains the AMD-K5 processor signature, which is comprised of the instruction family, model, and stepping.

- 3. These MSRs are described in "AMD-K5™ Processor x86 Architecture Extensions" on page 57.

- 4. The AMD-K5 processor supports write allocate only on Models 1, 2, and 3, with a Stepping of 4 or greater.

#### **Segment Register Attributes**

The selector portion of all segment registers is cleared. The access rights and attribute fields are set up as shown in Table 10.

**Table 10. Segment Register Attribute Fields Initial Values**

| Attribute Field | Value | Description                       |

|-----------------|-------|-----------------------------------|

| G               | 0     | Byte granularity                  |

| D/B             | 0     | 16-bit                            |

| Р               | 1     | Present                           |

| DPL             | 0     | Privilege level                   |

| S               | 1     | Application segment (except LDTR) |

| Туре            | 2     | Data, read-write                  |

The limit fields are set to FFFFh. For CS, the base address is set to FFFF\_0000h; for all others the base address is 0. Note that IDTR and GDTR consist of the just base and limit values, which are initialized to 0 and FFFFh, respectively.

#### State of the AMD-K5™ Processor After INIT

The assertion of INIT causes the processor to empty its pipelines, initialize most of its internal state, and branch to address FFFF\_FFF0h—the same instruction execution starting point used after RESET. Unlike RESET, the processor preserves the contents of its caches, the floating-point state, the SMM base, MSRs, and the CD and NW bits of the CR0 register.

The edge-sensitive interrupts FLUSH and SMI are sampled and preserved during the INIT process and are handled accordingly after the initialization is complete. However, the processor resets any pending NMI interrupt upon sampling INIT asserted.

INIT can be used as an accelerator for 80286 code that requires a reset to exit from Protected mode back to Real mode.

### AMD-K5™ Processor Test and Debug

The AMD-K5 processor has the following modes in which processor and system operation can be tested or debugged:

- Hardware Configuration Register (HWCR) The HWCR is a MSR that contains configuration bits that enable cache, branch tracing, debug, and clock control functions.

- Built-In Self-Test (BIST)—Both normal and test access port (TAP) BIST.

- Output-Float Test—A test mode that causes the AMD-K5 processor to float all of its output and bidirectional signals.

- Cache and TLB Testing—The Array Access Register (AAR) supports writes and reads to any location in the tag and data arrays of the processor's on-chip caches and TLBs.

- *Debug Registers*—Standard 486 debug functions with an I/O-breakpoint extension.

- Branch Tracing—A pair of special bus cycles can be driven immediately after taken branches to specify information about the branch instruction and its target. The Hardware Configuration Register (HWCR) provides support for this and other debug functions.

- Functional Redundancy Checking—Support for real-time testing that uses two processors in a master-checker relationship.

- Test Access Port (TAP) Boundary-Scan Testing—The JTAG test access functions defined by the IEEE Standard Test Access Port and Boundary-Scan Architecture (IEEE 1149.1-1990) specification.

- Hardware Debug Tool (HDT)—The hardware debug tool (HDT), sometimes referred to as the debug port or Probe mode, is a collection of signals, registers, and processor microcode enabled when external debug logic drives R/S Low or loads the AMD-K5 processor's Test Access Port (TAP) instruction register with the USEHDT instruction.

The test-related signals are described in Chapter 5 of the  $AMD-K5^{TM}$  Processor Technical Reference Manual, order# 18524. The signals include the following:

- FLUSH

- FRCMC

- IERR

- INIT

- PRDY

- R/S

- RESET

- TCK

- TDI

- TDO

- TMS

- TRST

The sections that follow provide details on each of the test and debug features.

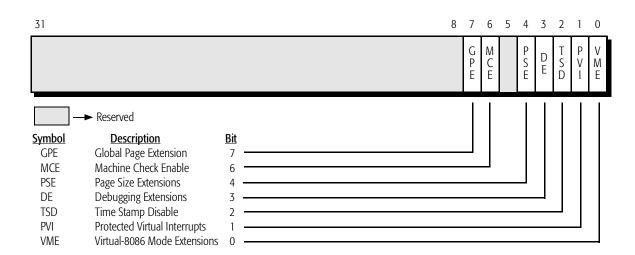

#### **Hardware Configuration Register (HWCR)**

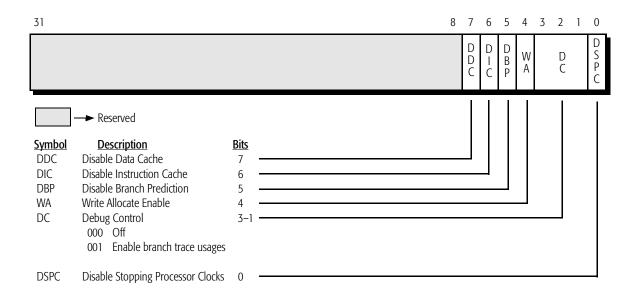

The Hardware Configuration Register (HWCR) is a MSR that contains configuration bits that enable cache, branch tracing, write allocation, debug, and clock control functions. The WRMSR and RDMSR instructions access the HWCR when the ECX register contains the value 83h, as described on page 90. Figure 2 and Table 11 show the format and fields of the HWCR.

Figure 2. Hardware Configuration Register (HWCR)

**Table 11. Hardware Configuration Register (HWCR) Fields**

| Bit           | Mnemonic | Description               | Function                   |  |

|---------------|----------|---------------------------|----------------------------|--|

| 31-8          | -        | -                         | reserved                   |  |

| 7             | DDC      | Disable Data Cache        | Disables data cache        |  |

| '             | DDC      | Disable Data Cacile       | 0 = enabled, 1 = disabled  |  |

| 6             | DIC      | Disable Instruction Cache | Disables instruction cache |  |

| 0             | DIC      | Disable Instruction Cache | 0 = enabled, 1 = disabled  |  |

| г             | DBP      | Disable Branch Prediction | Disables branch prediction |  |

| 5             | DDP      | Disable Branch Prediction | 0 = enabled, 1 = disabled  |  |

| 4             | \A/A*    | Enable Write Allocate     | Enables write allocation   |  |

| 4             | WA*      | Enable Write Allocate     | 0 = disabled, 1 = enabled  |  |

| Note:<br>* Th |          |                           |                            |  |

**Table 11. Hardware Configuration Register (HWCR) Fields (continued)**

| Bit                                                                                                                | Mnemonic | Description                          | Function                                                                         |

|--------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------|----------------------------------------------------------------------------------|

| 3–1                                                                                                                | DC       | Debug Control                        | Debug control bits:                                                              |

|                                                                                                                    |          |                                      | 000 Off (disable HWCR debug control)                                             |

|                                                                                                                    |          |                                      | 001 Enable branch-tracing messages. See "Branch Tracing" on page 39.             |

|                                                                                                                    |          |                                      | 010 reserved                                                                     |

|                                                                                                                    |          |                                      | 011 reserved                                                                     |

|                                                                                                                    |          |                                      | 100 reserved                                                                     |

|                                                                                                                    |          |                                      | 101 reserved                                                                     |

|                                                                                                                    |          |                                      | 110 reserved                                                                     |

|                                                                                                                    |          |                                      | 111 reserved                                                                     |

| 0                                                                                                                  | DSPC     | Disable Stopping<br>Processor Clocks | Disables stopping of internal processor clocks in the Halt and Stop Grant states |

|                                                                                                                    |          |                                      | 0 = enabled, 1 = disabled                                                        |

| Note:  * The AMD-K5 processor supports write allocate only on Models 1, 2, and 3, with a Stepping of 4 or greater. |          |                                      |                                                                                  |

#### **Built-In Self-Test (BIST)**

The processor supports the following types of built-in self-test:

- *Normal BIST*—A built-in self-test mode typically used to test system functions after RESET

- *Test Access Port (TAP) BIST*—A self-test mode started by the TAP instruction, RUNBIST

All internal arrays except the TLB are tested in parallel by hardware. The TLB is tested by microcode. The AMD-K5 processor does not report parity errors on IERR for every cache or TLB access. Instead, the AMD-K5 fully tests its caches during the BIST. EADS should not be asserted during a BIST. The AMD-K5 accesses the physical tag array during BISTs, and these accesses can conflict with inquire cycles.

#### **Normal BIST**

The normal BIST is invoked if INIT is asserted at the falling edge of RESET. The BIST runs tests on the internal hardware that exercise the following resources:

- Instruction cache:

- Linear tag directory

- Instruction array

- Physical tag directory

- Data cache:

- Linear tag directory

- · Data array

- · Physical tag directory

- Entry-point and instruction-decode PLAs

- Microcode ROM

- TLB

The BIST runs a linear feedback shift register (LFSR) signature test on the microcode ROM in parallel with a March C test on the instruction cache, data cache, and physical tags. This is followed by the March C test on the TLB arrays and an LFSR signature test on the PLA, in that order. Upon completion of the PLA test, the processor transfers the test result from an internal Hardware Debug Test (HDT) data register to the EAX register for external access, resets the internal microcode, and begins normal code fetching.

The result of the BIST can be accessed by reading the lower 9 bits of the EAX register. If the EAX register value is 0000\_0000h, the test completed successfully. If the value is not zero, the non-zero bits indicate where the failure occurred, as shown in Table 12. The processor continues with its normal boot process after the BIST is completed, whether the BIST passed or failed.

**Table 12. BIST Error Bit Definition in EAX Register**

| Bit Number |          | Bit Value |

|------------|----------|-----------|

| Bit Number | 0        | 1         |

| 31–9       | No Error | Always 0  |

| 8          | No Error | Data path |

**Bit Value Bit Number** 0 No Error Instruction-cache instructions 7 6 No Error Instruction-cache linear tags 5 No Error Data-cache linear tags No Error **PLA** 4 3 No Error Microcode ROM 2 No Error Data-cache data 1 No Error Instruction cache physical tags 0 No Error Data-cache physical tags

**Table 12. BIST Error Bit Definition in EAX Register (continued)**

# Test Access Port (TAP) BIST

The TAP BIST performs all the functions of the normal BIST, up to and including the PLA signature test, in the exact manner as the normal BIST. However, after the PLA test, the test result is not transferred to the EAX register.

The TAP BIST is started by loading and executing the RUNBIST instruction in the test access port, as described in "Boundary Scan Architecture Support" on page 41. When the RUNBIST instruction is executed, the processor enters into a reset mode that is identical to that entered when the RESET signal is asserted. Upon completion of the TAP BIST, the result remains in the BIST result register for shifting out through the TDO signal. The TRST signal must be asserted, or the TAP instruction must be changed, to exit TAP BIST and return to normal operation.

# **Output-Float Test**

The Output-Float Test mode is entered if FLUSH is asserted before the falling edge of RESET. This causes the processor to place all of its output and bidirectional signals in the high-impedance state. In this isolated state, system board traces and connections can be tested for integrity and driveability. The Output-Float Test mode can only be exited by asserting RESET again.

On the AMD-K5 processor and Pentium, FLUSH is an edge-triggered interrupt. On the 486 processor, however, the signal is a level-sensitive input.

## **Cache and TLB Testing**

The internal cache for the AMD-K5 processor is divided into two caches—a 16-Kbyte, 4-way, set-associative instruction cache and an 8-Kbyte, 4-way, set-associative data cache. Cache and TLB testing is often done by the BIOS or operating system during power-up.

**Note:** The AMD-K6 MMX processor does not contain these features. The AMD-K6 processor contains a built-in self-test for all internal memories.

The individual locations of all SRAM arrays on the AMD-K5 processor are accessible with the RDMSR and WRMSR instructions. To access an array location, set up the Array Access MSR code (82h) in ECX, and the array pointer (see page 28) in EDX. EAX holds the data to be read or written. Tests can be performed on the following arrays:

- *Data Cache*—8-Kbyte, 4-way, set-associative

- Data array

- Linear-tag array

- Physical-tag array

- *Instruction Cache*—16-Kbyte, 4-way, set-associative

- Instruction array

- · Linear-tag array

- Physical-tag array

- Valid-bit array

- Branch-prediction bit array

- 4-Kbyte TLB—128-entry, 4-way, set-associative

- Linear-tag array

- Page array

- 4-Mbyte TLB—4-entry, fully associative

- Linear-tag array

- Page array

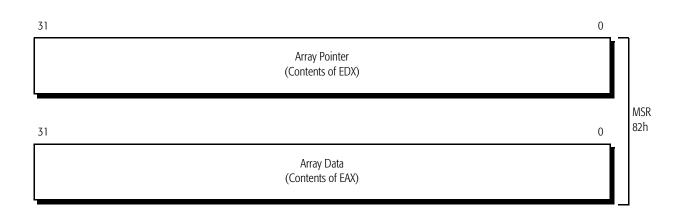

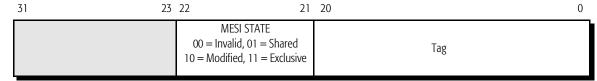

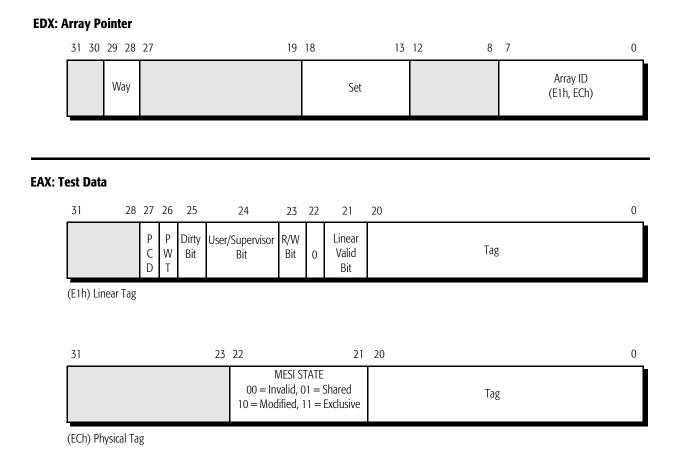

# Array Access Register (AAR)

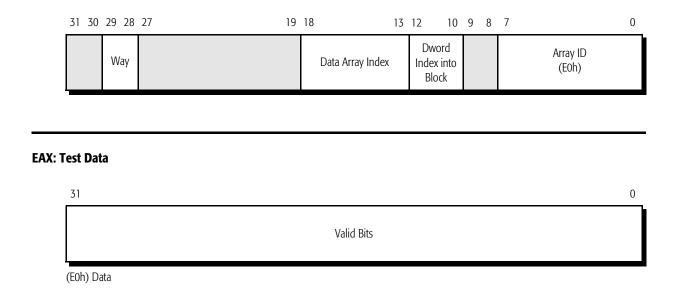

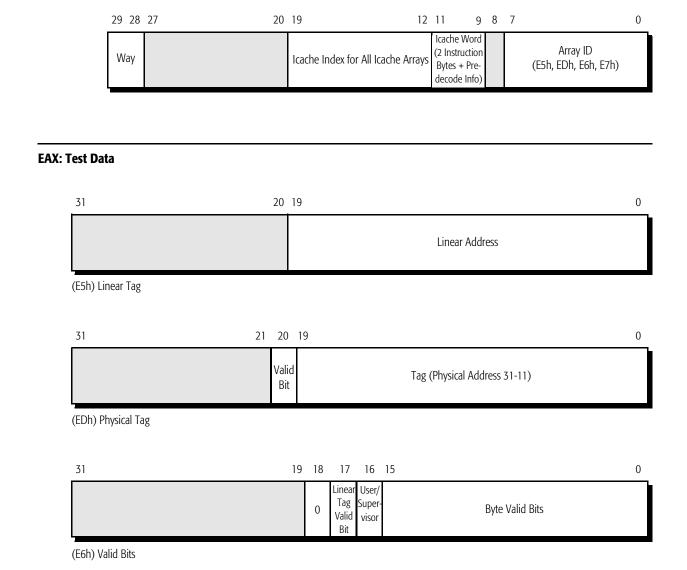

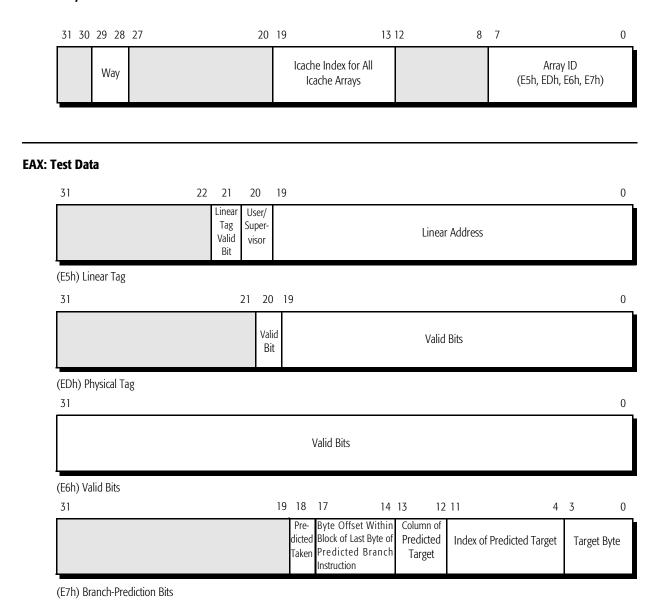

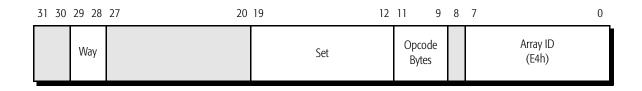

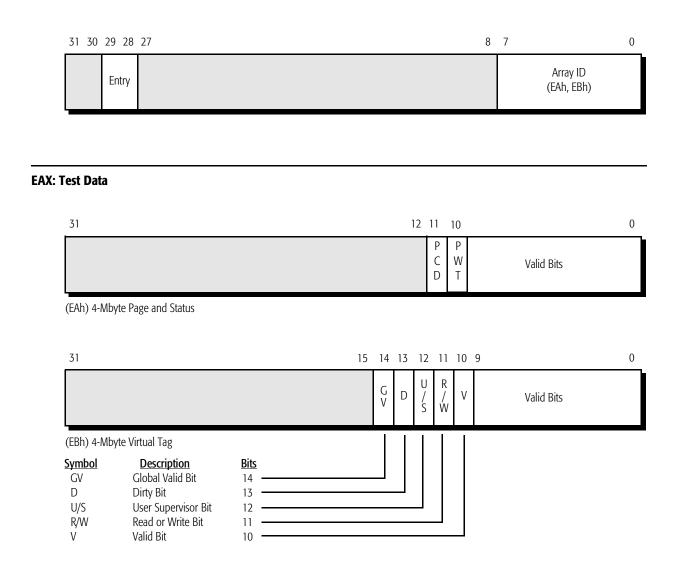

The 64-bit Array Access Register (AAR) is a MSR that contains a 32-bit *array pointer* that identifies the array location to be tested and 32 bits of *array test data* to be read or written. The WRMSR and RDMSR instructions access the AAR when the ECX register contains the value 82h, as described on page 90. Figure 3 shows the format of the AAR.

Figure 3. Array Access Register (AAR)

To read or write an array location, perform the following steps:

- 1. *ECX*—Enter 82h into ECX to access the 64-bit AAR.

- 2. *EDX*—Enter a 32-bit *array pointer* into EDX, as shown in Figures 4 through 12 (top).

- 3. *EAX*—Read or write 32 bits of *array test data* to or from EAX, as shown in Figures 4 through 12 (bottom).

### **Array Pointer**

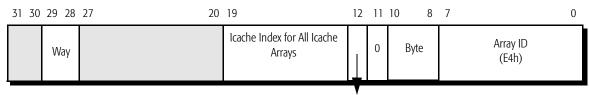

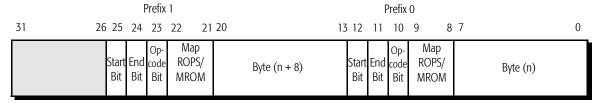

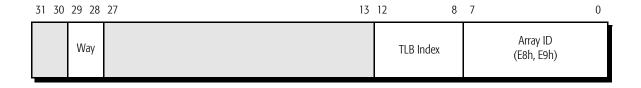

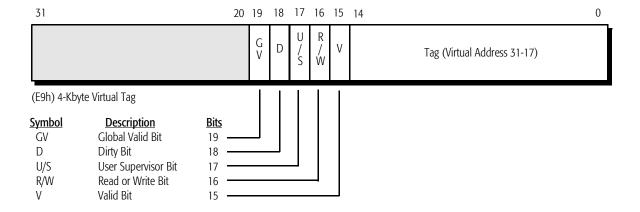

The array pointers entered in EDX (Figures 4 through 12, top) specify particular array locations. For example, in the data- and instruction-cache arrays, the way (or column) and set (or index) in the array pointer specify a cache line in the 4-way, set-associative array. The array pointers for data-cache data and instruction-cache instructions also specify a dword location within that cache line. In the data cache, this dword is 32 bits of data; in the instruction cache, this dword is two instruction bytes plus their associated pre-decode bits. For the 4-Kbyte TLB, the way and set specify one of the 128 TLB entries. In 4-Mbyte TLB, one of only four entries is specified.

Bits 7–0 of every array pointer encode the *array ID*, which identifies the array to be accessed, as shown in Table 13. To simplify multiple accesses to an array, the contents of EDX are retained after the RDMSR instruction executes (EDX is normally cleared after a RDMSR instruction).

**Table 13. Array IDs in Array Pointers**

| Array Pointer<br>Bits 7–0 | Accessed Array                            |

|---------------------------|-------------------------------------------|

| E0h                       | Data Cache: Data                          |

| E1h                       | Data Cache: Linear Tag                    |

| ECh                       | Data Cache: Physical Tag                  |

| E4h                       | Instruction Cache: Instructions           |

| E5h                       | Instruction Cache: Linear Tag             |

| EDh                       | Instruction Cache: Physical Tag           |

| E6h                       | Instruction Cache: Valid Bits             |

| E7h                       | Instruction Cache: Branch-Prediction Bits |

| E8h                       | 4-Kbyte TLB: Page                         |

| E9h                       | 4-Kbyte TLB: Virtual Tag                  |

| EAh                       | 4-Mbyte TLB: Page                         |

| EBh                       | 4-Mbyte TLB: Virtual Tag                  |

## **Array Test Data**

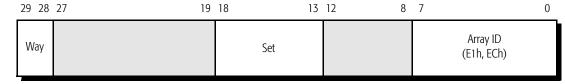

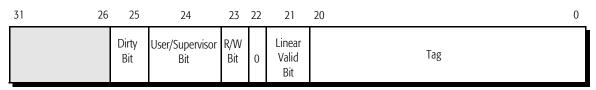

EAX specifies the test data to be read or written with the RDMSR or WRMSR instruction (see Figures 4 through 12). For example, in Figure 4 (top) the array pointer in EDX specifies a way and set within the data-cache linear tag array (E1h in bits 7–0 of the array pointer) or the physical tag array (ECh in bits 7–0 of the array pointer). If the linear tag array (E1h) is accessed, the data read or written includes the tag and the status bits. The details of the valid fields in EAX are proprietary.

21062D/0-April 1997

### **EAX: Test Data**

(E1h) Linear Tag

(ECh) Physical Tag

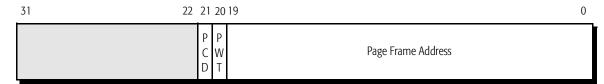

Figure 4. Test Formats: Dcache Tags for the AMD-K5™ Processor Model 0

Figure 5. Test Formats: Dcache Tags for the AMD-K5™ Processor Model 1 and Greater

21062D/0-April 1997

## **EDX: Array Pointer**

Figure 6. Test Formats: Dcache Data for All Models of the AMD-K5™ Processor

## **EDX: Array Pointer**

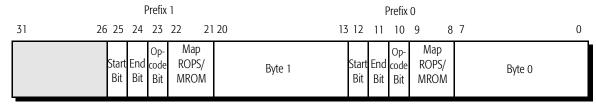

(E7h) Branch-Prediction Bits

31

Figure 7. Test Formats: Icache Tags for the AMD-K5™ Processor Model 0

AMD-K5™ Processor