IBM Single Chip SCSI

Subsystem

Work In Progress. At first, I wandted to describe each

component fully, but there's a bit of mystery [we have a

patent description, not a tech ref]. I decided to put a

significant illustration under each patent so I can put

things in context. LFOOnly the 8556 and 9556 have a "SCSI Subsystem" attached to the local bus. Patents refer to it as a "SCSI Data Flow Controller"

8556 - JALPA SCSI Subsystem

9556 - MONARCH SCSI Subsystem

All other implementations with the 8032, 80C188, and 80C186 use an adapter implementation attached to the Micro Channel bus.

Tribble / Short SCSI adapters "PS/2 Microchannel SCSI Adapter", Console Ver 1.0

Uses Adaptec AIC-6250

8556/9556 "JALPA/MONARCH SCSI Subsystem", Console Ver 1.2

Lacks Adaptec AIC-6250

All SPOCK use "PS/2 Microchannel SCSI Adapter w/Cache" Console Ver 2.2

Old, newer use AIC-6250. Latest uses 84F8324 Line Interface

All Corvette use "PS/2 Microchannel SCSI Dual Bus Adapter" Console Ver 3.1

All versions use Cutlass controller, Malibu bus interface

IBM wandted a reduced cost SCSI based system in the Model 56s. Since the 8556 / 9556 both use 16-bit CPUs, there wouldn't be much sense in dropping a full featured SCSI implementation like a 8032 [Tribble] or a 80C188 [SPOCK].

No observed SCSI cache on a 56, unless it is internal to the SCSI ASIC.

NOTE: Folks, for years, I was unaware IF the on-board SCSI of the 8556 / 9556 were actually local bus -OR- if they were attached to the Micro Channel. They -ARE- local bus.

NOTE: One of these patents describes a "mode pin" on the SCS that allows the system CPU to take over SCSI Controller operations -IF- the system is waiting to execute those functions.

US5353417A Personal computer with bus interface controller coupled directly with local processor and input/output data buses and for anticipating memory control changes on arbitration for bus access

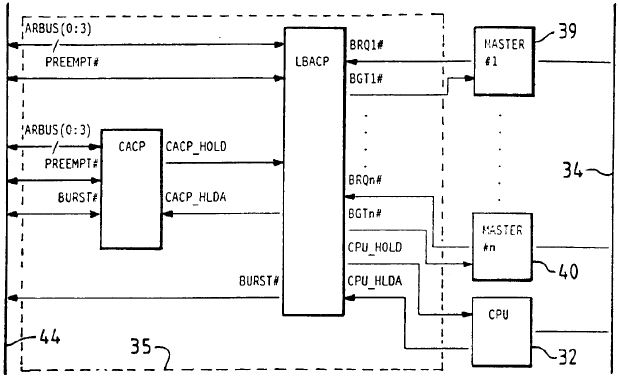

NOTE: The CPU, NPU, SCS, SIMMs, and BIOS ROM hangs off the local bus [also called "High Speed Bus"]. The Local Bus connects to the Bus Interface Controller [BIC], which does protocol translation, DMA controller, memory controller. Local Bus Arbitration Control Point [LBACP] -AND- the Central Arbitration Control Point [CACP] that supports the MCA Bus.

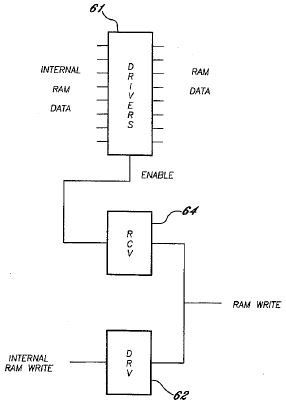

US5586302A Personal computer system having storage controller with memory write control

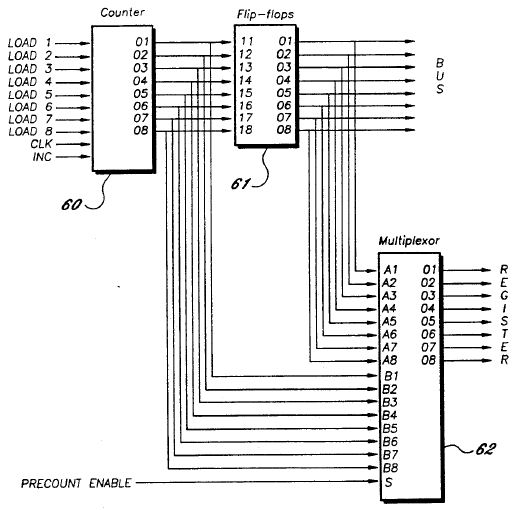

US5371861A Personal computer with small computer system interface (SCSI) data flow storage controller capable of storing and processing multiple command descriptions ("threads")

NOTE: The block diagram for the 8556 "SCSI Data Flow Controller" had no identification except for where there are numbers as call-outs. The blank blocks are probably 63 and 67. One block -MIGHT- be ROM, the other RAM [cache implementation?]

US5287476A Personal computer system with storage controller controlling data transfer

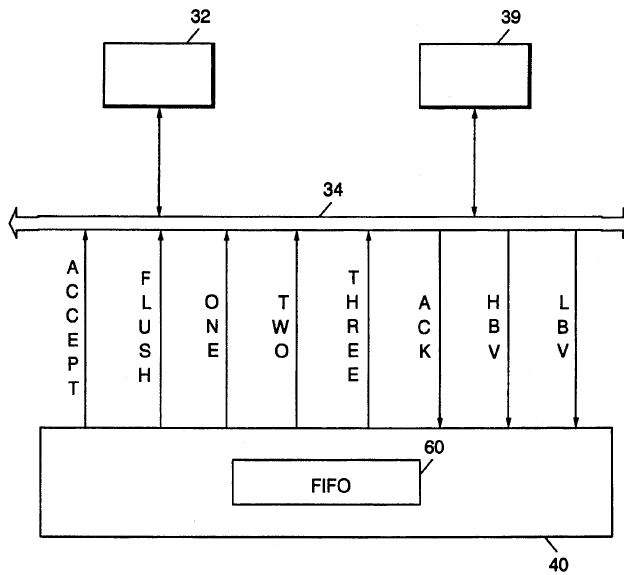

US5550991A Personal computer system having high speed local processor bus and storage controller with FIFO memory coupled directly thereto

EP0518504A1 Personal computer with local bus arbitration.