# National Semiconductor LM1524/LM2524/LM3524 Regulating Pulse Width Modulator

# **General Description**

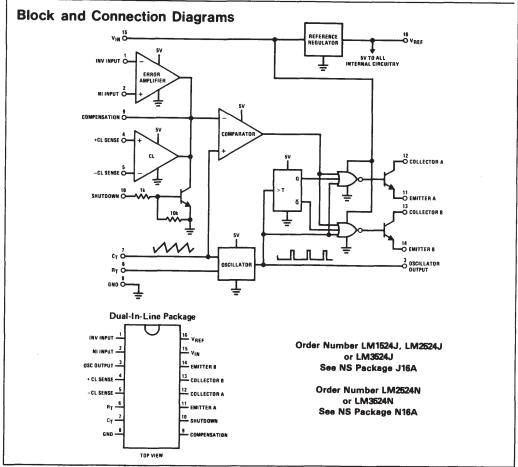

The LM1524 series of regulating pulse width modulators contains all of the control circuitry necessary to implement switching regulators of either polarity, transformer coupled DC to DC converters, transformerless polarity converters and voltage doublers, as well as other power control applications. This device includes a 5V voltage regulator capable of supplying up to 50 mA to external circuitry, a control amplifier, an oscillator, a pulse width modulator, a phase splitting flip-flop, dual alternating output switch transistors, and current limiting and shutdown circuitry. Both the regulator output transistor and each output switch are internally current limited and, to limit junction temperature, an internal thermal shutdown circuit is employed. The LM1524 is rated for operation from  $-55^{\circ}C$  to  $+125^{\circ}C$  and is packaged in a hermetic 16-lead DIP (J). The LM2524 and LM3524 are rated for operation from 0°C to +70°C and are

packaged in either a hermetic 16-lead DIP (J) or a 16-lead molded DIP (N).

#### **Features**

- Complete PWM power control circuitry

- Frequency adjustable to greater than 100 kHz

- 2% frequency stability with temperature

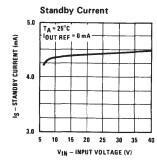

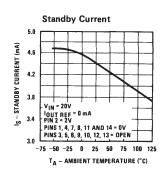

- Total quiescent current less than 10 mA

- Dual alternating output switches for both push-pull or single-ended applications

- Current limit amplifier provides external component protection

- On-chip protection against excessive junction temperature and output current

- 5V, 50 mA linear regulator output available to user

# **Absolute Maximum Ratings**

40V Input Voltage 6V Reference Voltage, Forced 50 mA Reference Output Current Output Current (Each Output) 100 mA Oscillator Charging Current (Pin 6 or 7) 5 mA Internal Power Dissipation (Note 1) 1W Maximum Junction Temperature (J Package) (N Package)

Storage Temperature Range

150°C 125°C -65°C to +150°C 300°C Lead Temperature (Soldering, 10 seconds)

Operating Temperature Range

LM1524 LM2524/LM3524 -55°C to +125°C 0°C to +70°C

## **Electrical Characteristics**

Unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}C$  to +125°C for the LM1524 and 0°C to +70°C for the LM2524 and LM3524,  $V_{IN} = 20V$ , and f = 20 kHz. Typical values other than temperature coefficients, are at  $T_A = 25^{\circ}C$ .

| PARAMETER                                               | CONDITIONS                                      | LM1524/<br>LM2524 |     |     | LM3524 |     |     | UNITS  |

|---------------------------------------------------------|-------------------------------------------------|-------------------|-----|-----|--------|-----|-----|--------|

|                                                         |                                                 | MIN               | TYP | MAX | MIN    | TYP | MAX |        |

| Reference Section                                       |                                                 |                   |     |     |        |     |     |        |

| Output Voltage                                          | İ                                               | 4.8               | 5.0 | 5.2 | 4.6    | 5.0 | 5.4 | ٧      |

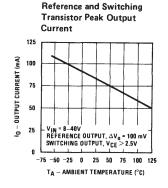

| Line Regulation                                         | V <sub>IN</sub> = 8-40V                         |                   | 10  | 20  |        | 10  | 30  | m∨     |

| Load Regulation                                         | IL = 020 mA                                     |                   | 20  | 50  |        | 20  | 50  | m∨     |

| Ripple Rejection                                        | f = 120 Hz, TA = 25°C                           |                   | 66  |     | ļ ,    | 66  |     | dB     |

| Short-Circuit Output Current                            | VREF = 0, TA = 25°C                             |                   | 100 |     | İ      | 100 |     | mA     |

| Temperature Stability                                   | Over Operating Temperature Range                |                   | 0.3 | 1   |        | 0.3 | 1   | %      |

| Long Term Stability                                     | T <sub>A</sub> = 25°C                           |                   | 20  |     |        | 20  |     | mV/khr |

| Oscillator Section                                      |                                                 |                   |     |     |        |     |     |        |

| Maximum Frequency                                       | $C_T = 0.001 \mu\text{F}, R_T = 2 k\Omega$      |                   | 350 |     |        | 350 |     | kHz    |

| Initial Accuracy                                        | RT and CT constant                              |                   | 5   |     | İ      | 5   |     | %      |

| Frequency Change with Voltage                           | V <sub>IN</sub> = 8-40V, T <sub>A</sub> = 25°C  |                   |     | 1   |        |     | 1   | %      |

| Frequency Change with Temperature                       | Over Operating Temperature Range                |                   |     | 2   | İ      |     | 2   | %      |

| Output Amplitude (Pin 3)                                | TA = 25°C                                       |                   | 3.5 |     | ĺ      | 3.5 |     | v      |

| Output Pulse Width (Pin 3)                              | C <sub>T</sub> = 0.01 μF, T <sub>A</sub> = 25°C |                   | 0.5 |     |        | 0.5 |     | μs     |

| Error Amplifier Section                                 |                                                 |                   |     |     |        |     |     |        |

| Input Offset Voltage                                    | V <sub>CM</sub> = 2.5V                          | 1                 | 0.5 | 5   |        | 2   | 10  | mV     |

| Input Bias Current                                      | V <sub>CM</sub> = 2.5V                          |                   | 2   | 10  |        | 2   | 10  | μΑ     |

| Open Loop Voltage Gain                                  |                                                 | 72                | 80  |     | 60     | 80  |     | dB     |

| Common-Mode Input Voltage Range                         | T <sub>A</sub> = 25°C                           | 1.8               |     | 3.4 | 1.8    |     | 3.4 | \ v    |

| Common-Mode Rejection Ratio                             | T <sub>A</sub> = 25°C                           | l                 | 70  |     |        | 70  |     | dB     |

| Small Signal Bandwidth                                  | A <sub>V</sub> = 0 dB, T <sub>A</sub> = 25°C    |                   | 3   |     |        | 3   | i   | MHz    |

| Output Voltage Swing                                    | T <sub>A</sub> = 25°C                           | 0.5               |     | 3.8 | 0.5    |     | 3.8 | v      |

| Comparator Section                                      |                                                 |                   |     |     |        |     |     |        |

| Maximum Duty Cycle                                      | % Each Output ON                                | 45                | 1   |     | 45     | İ   | i   | 1 %    |

| Input Threshold (Pin 9)                                 | Zero Duty Cycle                                 |                   | 1   |     |        | 1   |     | v      |

| Input Threshold (Pin 9)                                 | Maximum Duty Cycle                              | 1                 | 3.5 |     |        | 3.5 |     | \ \ \  |

| Input Bias Current                                      |                                                 |                   | -1  |     |        | -1  |     | μΑ     |

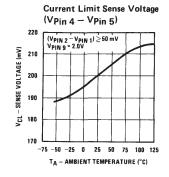

| Current Limiting Section                                |                                                 |                   |     |     |        |     |     |        |

| Sense Voltage                                           | $V_{(Pin 2)} - V_{(Pin 1)} \ge 50 \text{ mV},$  | 190               | 200 | 210 | 180    | 200 | 220 | mV     |

|                                                         | Pin 9 = 2V, T <sub>A</sub> = 25°C               |                   | 0.2 |     |        | 0.2 |     | mV/°C  |

| Sense Voltage T.C.                                      |                                                 | -0.7              | 0.2 | 1   | - 0.7  | 0.2 | 1   |        |

| Common-Mode Voltage                                     |                                                 | -0.7              |     | '   | 0.7    |     | '   |        |

| Output Section (Each Output)  Collector-Emitter Voltage |                                                 | 40                |     |     | 40     |     |     | \      |

|                                                         | V 40V                                           | "                 | 0.1 | 50  |        | 0.1 | 50  | μΑ     |

| Collector Leakage Current                               | V <sub>CE</sub> = 40V                           | 1                 | 1   | 2   |        | 1   | 2   | `\     |

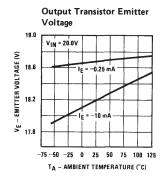

| Saturation Voltage                                      | IC = 50 mA                                      | 17                | 18  | -   | 17     | 18  |     |        |

| Emitter Output Voltage                                  | V <sub>IN</sub> = 20V, I <sub>E</sub> = -250 μA | 1 "               | 0.2 | 1   | "      | 0.2 |     | μ      |

| Rise Time (10% to 90%)                                  | $R_C = 2 k\Omega$ , $T_A = 25^{\circ}C$         | 1                 | 0.2 |     | 1      | 0.1 |     | μ μ    |

| Fall Time (90% to 10%)                                  | $R_C = 2 k\Omega$ , $T_A = 25^{\circ}C$         |                   |     |     |        | 1   | 1.0 | 1      |

| Total Standby Current                                   | V <sub>IN</sub> = 40V, Pins 1, 4, 7, 8, 11      |                   | 5   | 10  |        | 5   | 10  | mA     |

|                                                         | and 14 are grounded, Pin 2 = 2V,                |                   |     |     |        |     |     |        |

|                                                         | All Other Inputs and Outputs Open               |                   |     |     |        | 1   |     |        |

Note 1: For operation at elevated temperatures, devices in the J package must be derated based on a thermal resistance of 100° C/W, junction to ambient, and devices in the N package must be derated based on a thermal resistance of 150° C/W, junction to ambient.

# **Typical Performance Characteristics**

Dissipation (J Package)

10

10

10

1.0

1.0

-75 -<del>5</del>0 -25 0 25 50 75 100 125

TA - AMBIENT TEMPERATURE (°C)

Maximum Average Power

Maximum Average Power Dissipation (N Package)

10

10

10

10

11

10

15

30

45

60

75

T<sub>A</sub> - AMBIENT TEMPERATURE (°C)

# **Functional Description**

## INTERNAL VOLTAGE REGULATOR

The LM3524 has on chip a 5V, 50 mA, short circuit protected voltage regulator. This voltage regulator provides a supply for all internal circuitry of the device and can be used as an external reference.

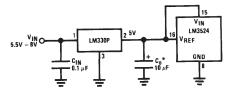

For input voltages of less than 8V the 5V output should be shorted to pin 15,  $V_{IN}$ , which disables the 5V regulator. With these pins shorted the input voltage must be limited to a maximum of 6V. If input voltages of 6–8V are to be used, a pre-regulator, as shown in Figure 1, must be added.

\*Minimum  $C_0$  of 10  $\mu F$  required for stability.

#### FIGURE 1

## OSCILLATOR

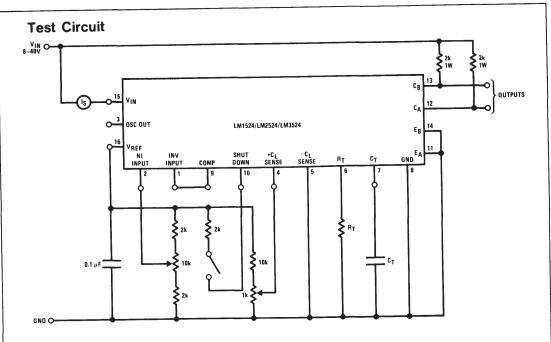

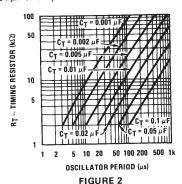

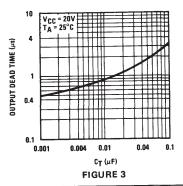

The LM3524 provides a stable on-board oscillator. Its frequency is set by an external resistor, R<sub>T</sub> and capacitor, C<sub>T</sub>. A graph of R<sub>T</sub>, C<sub>T</sub> vs oscillator frequency is shown in *Figure 2*. The oscillator's output provides the signals for triggering an internal flip-flop, which direct the PWM information to the outputs, and a blanking pulse to turn off both outputs during transitions to ensure that cross conduction does not occur. The width of the blanking pulse, or dead time, is controlled by the value of C<sub>T</sub>, as shown in *Figure 3*. The recommended

values of RT are 1.8  $k\Omega$  to 100  $k\Omega,$  and for CT, 0.001  $\mu\text{F}$  to 0.1  $\mu\text{F}$  .

# Functional Description (Continued)

#### **ERROR AMPLIFIER**

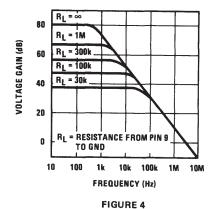

The error amplifier is a differential input, transconductance amplifier. Its gain, nominally 80 dB, is set by either feedback or output loading. This output loading can be done with either purely resistive or a combination of resistive and reactive components. A graph of the amplifier's gain vs output load resistance is shown in Figure 4.

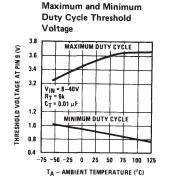

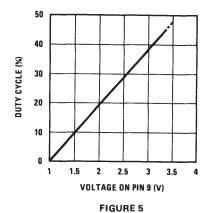

The output of the amplifier, or input to the pulse width modulator, can be overridden easily as its output impedance is very high (Z  $_{0}$   $\simeq$  5 M $\Omega$  ). For this reason a DC voltage can be applied to pin 9 which will override the error amplifier and force a particular duty cycle to the outputs. An example of this could be a non-regulating motor speed control where a variable voltage was applied to pin 9 to control motor speed. A graph of the output duty cycle vs the voltage on pin 9 is shown in Figure 5.

The amplifier's inputs have a common-mode input range of 1.8V-3.4V. The on board regulator is useful for biasing the inputs to within this range.

#### **CURRENT LIMITING**

The function of the current limit amplifier is to override the error amplifier's output and take control of the pulse width. The output duty cycle drops to about 25% when a current limit sense voltage of 200 mV is applied between the +C  $_{\mbox{\scriptsize L}}$  and -C  $_{\mbox{\scriptsize L}}$  terminals. Increasing the sense voltage approximately 5% results in a 0% output duty cycle. Care should be taken to ensure the -0.7V to +1.0V input common-mode range is not exceeded.

# **OUTPUT STAGES**

The outputs of the LM3524 are NPN transistors, capable of a maximum current of 100 mA. These transistors are driven 180° out of phase and have noncommitted open collectors and emitters as shown in Figure 6.

OUTPUT DRIVE INVERTER

10-148

FIGURE 6

# **Typical Applications**

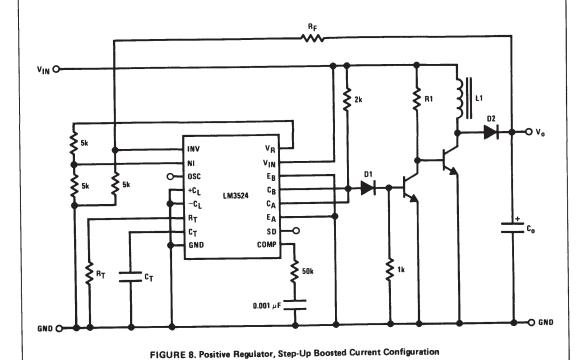

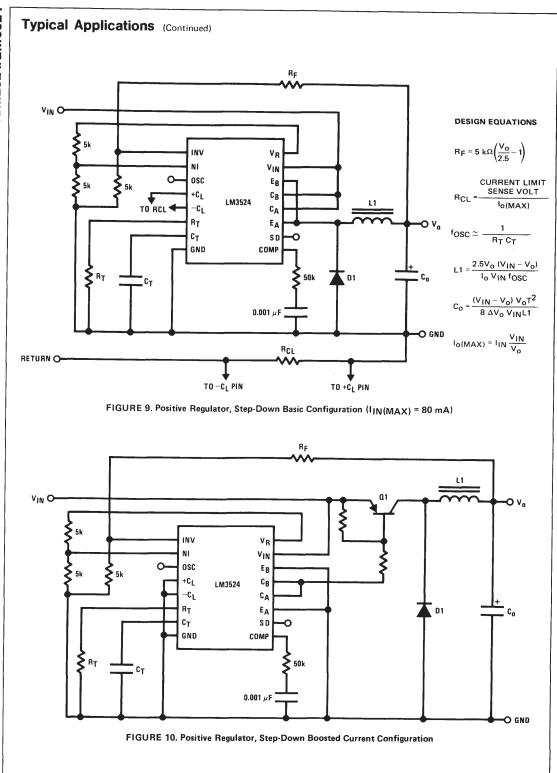

FIGURE 7. Positive Regulator, Step-Up Basic Configuration (I<sub>IN</sub>(MAX) = 80 mA)

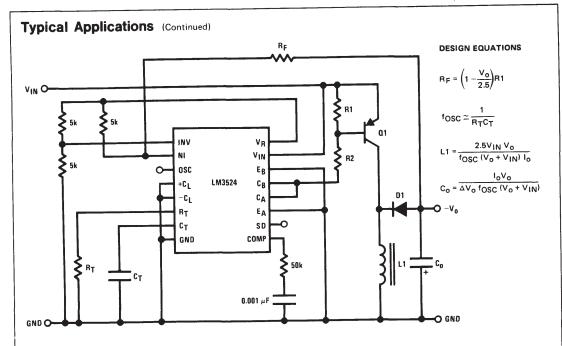

FIGURE 11. Boosted Current Polarity Inverter

# BASIC SWITCHING REGULATOR THEORY AND APPLICATIONS

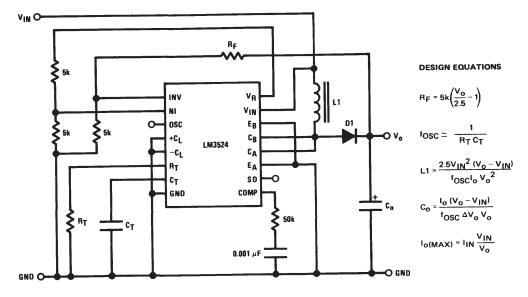

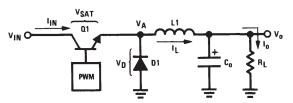

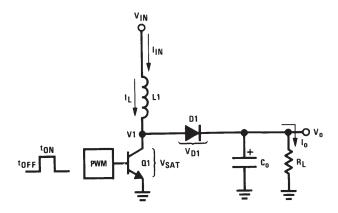

The basic circuit of a step-down switching regulator circuit is shown in *Figure 12*, along with a practical circuit design using the LM3524 in *Figure 15*.

The circuit works as follows: Q1 is used as a switch, which has ON and OFF times controlled by the pulse width modulator. When Q1 is ON, power is drawn from  $V_{IN}$  and supplied to the load through L1;  $V_{A}$  is at approximately  $V_{IN}$ , D1 is reverse biased, and  $C_{O}$  is

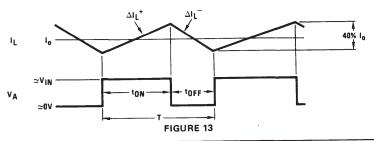

charging. When Q1 turns OFF the inductor L1 will force VA negative to keep the current flowing in it, D1 will start conducting and the load current will flow through D1 and L1. The voltage at VA is smoothed by the L1, C0 filter giving a clean DC output. The current flowing through L1 is equal to the nominal DC load current plus some  $\Delta I_{\rm L}$  which is due to the changing voltage across it. A good rule of thumb is to set  $\Delta I_{\rm LP-P} \simeq 40\%^{-1} O$ .

FIGURE 12. Basic Step-Down Switching Regulator

From the relation V  $_L$  = L  $\frac{d_i}{d_t}$  ,  $\Delta I_L \simeq \frac{V_L T}{L1}$

$$\Delta I_L^+ = \frac{(V_{IN} - V_o) t_{ON}}{L1}$$

;  $\Delta I_L^- = \frac{V_o t_{OFF}}{L1}$

Neglecting VSAT, VD, and settling  $\Delta I_L^+ = \Delta I_L^-$ ;

$$\boxed{V_{O} \simeq V_{IN} \left(\frac{t_{ON}}{t_{OFF} + t_{ON}}\right)} = V_{IN} \left(\frac{t_{ON}}{T}\right);$$

where T = Total Period

The above shows the relation between  $\mathbf{V_{IN}},\,\mathbf{V_{O}}$  and duty cycle.

$$IIN(DC) = IOUT(DC) \left( \frac{tON}{tON + tOFF} \right),$$

as Q1 only conducts during toN.

$$P_{IN} = I_{IN(DC)}V_{IN} = (I_{O(DC)})\left(\frac{t_{ON}}{t_{ON} + t_{OFF}}\right)V_{IN}$$

$$P_0 = I_0 V_0$$

The efficiency,  $\eta$ , of the circuit is:

$$\begin{split} \eta_{MAX} = & \frac{P_{O}}{P_{IN}} = \frac{I_{O}V_{O}}{I_{O}(\underline{t_{ON}})V_{IN} + (\underline{V_{SAT}\ t_{ON} + V_{D1}t_{OFF}})} I_{O} \\ = & \frac{V_{O}}{V_{O} + 1} \text{for } V_{SAT} = V_{D1} = 1V. \end{split}$$

$\eta$ MAX will be further decreased due to switching losses in Q1. For this reason Q1 should be selected to have the maximum possible f<sub>T</sub>, which implies very fast rise and fall times.

### **CALCULATING INDUCTOR L1**

$$t_{ON} \simeq \frac{(\Delta I_L^+) \cdot L_1}{(V_{IN} - V_O)}$$

,  $t_{OFF} = \frac{(\Delta I_L^-) \cdot L_1}{V_O}$

$$t_{ON} + t_{OFF} = T = \frac{(\Delta I_L^+) \cdot L1}{(V_{IN} - V_o)} + \frac{(\Delta I_L^-) \cdot L1}{V_o}$$

$$= \frac{0.4I_oL1}{(V_{IN} - V_o)} + \frac{0.4I_oL1}{V_o}$$

Since

$$\Delta I_L^+ = \Delta I_L^- = 0.4I_0$$

Solving the above for L1

$$L1 = \frac{2.5 \text{ V}_{0}(\text{V}_{IN} - \text{V}_{0})}{\text{I}_{0} \text{V}_{IN} \text{ f}}$$

where: L1 is in Henrys

f is switching frequency in Hz

## CALCULATING OUTPUT FILTER CAPACITOR Co.

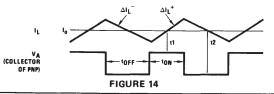

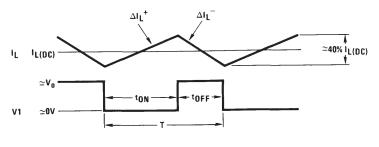

Figure 14 shows L1's current with respect to Q1's tON and tOFF times. This current must flow to the load and  $C_0$ .  $C_0$ 's current will then be the difference between  $I_L$ , and  $I_0$ .

$$Ic_0 = I_L - I_0$$

From Figure 14 it can be seen that current will be flowing into  $C_0$  for the second half of  $t_{ON}$  through the first half of  $t_{OFF}$ , or a time ,  $t_{ON}/2 + t_{OFF}/2$ . The current flowing for this time is  $\Delta I_L/4$ . The resulting  $\Delta V_c$  or  $\Delta V_O$  is described by:

$$\Delta V_{\text{OP-P}} = \frac{1}{C} \cdot \frac{\Delta I_L}{4} \cdot \left(\frac{t_{\text{ON}}}{2} + \frac{t_{\text{OFF}}}{2}\right)$$

$$= \frac{\Delta I_L}{4C} \left(\frac{t_{\text{ON}} + t_{\text{OFF}}}{2}\right)$$

Since

$$\Delta I_L = \frac{V_o(T - t_{ON})}{L1}$$

and  $t_{ON} = \frac{V_oT}{V_{IN}}$

$$\Delta V_{\text{op-p}} = \frac{V_o \left( T - \frac{V_o T}{V_{\text{IN}}} \right)}{4C \text{ L1}} \left( \frac{T}{2} \right) = \frac{(V_{\text{IN}} - V_o) V_o T^2}{8V_{\text{IN}} C_o \text{ L1}} \quad \text{or} \quad$$

$$C_{O} = \frac{(V_{IN} - V_{O})V_{O} T^{2}}{8\Delta V_{O}V_{IN}L1}$$

where: C is in farads, T is switching frequency

$\Delta V_0$  is p-p output ripple

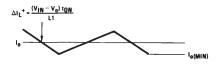

The inductor's current cannot be allowed to fall to zero, as this would cause the inductor to saturate. For this reason some minimum  $I_0$  is required as shown below:

$$I_{O(MIN)} = \frac{(V_{IN} - V_{O}) t_{ON}}{2L1} = \frac{(V_{IN} - V_{O}) V_{O}}{2fV_{IN}L1}$$

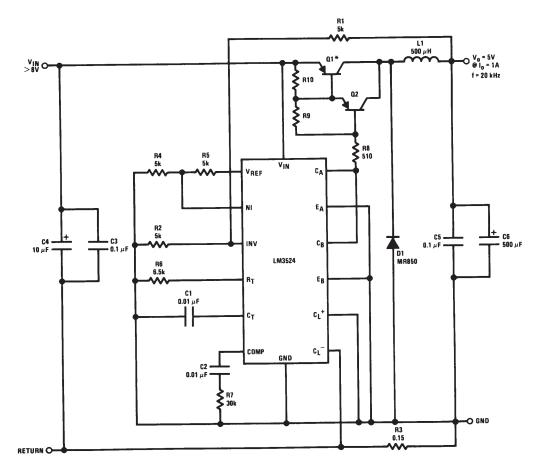

A complete step-down switching regulator schematic, using the LM3524, is illustrated in *Figure 15*. Transistors Q1 and Q2 have been added to boost the output to 1A. The 5V regulator of the LM3524 has been divided in half to bias the error amplifier's non-inverting input to within its common-mode range. Since each output transistor is on for half the period, actually 45%, they have been paralleled to allow longer possible duty cycles, up to 90%. This makes a lower possible input voltage. The output voltage is set by:

$$V_0 = V_{N1} \left( 1 + \frac{R1}{R2} \right),$$

where  $\ensuremath{V_{NI}}$  is the voltage at the error amplifier's non-inverting input.

Resistor R3 sets the current limit to:

$$\frac{200 \text{ mV}}{\text{R3}} = \frac{200 \text{ mV}}{0.15} = 1.3 \text{A}.$$

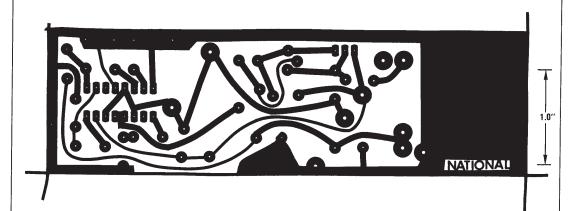

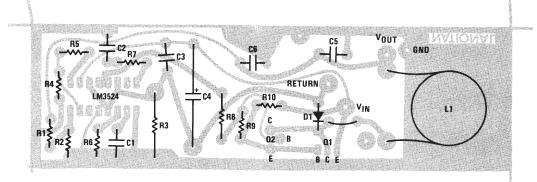

Figure 16 and 17 show a PC board layout and stuffing diagram for the 5V, 1A regulator of Figure 15. The regulator's performance is listed in Table 1.

<sup>\*</sup> Mounted to Staver Heatsink No. V5-1.

FIGURE 15. 5V, 1 Amp Step-Down Switching Regulator

Q1 = BD344 Q2 = 2N5023

L1 = > 40 turns No. 22 wire on Ferroxcube No. K300502 Torroid core.

TABLE I

| PARAMETER                      | CONDITIONS                                          | TYPICAL CHARACTERISTICS |

|--------------------------------|-----------------------------------------------------|-------------------------|

| Output Voltage                 | V <sub>IN</sub> = 10V, I <sub>O</sub> = 1A          | 5V                      |

| Switching Frequency            | V <sub>IN</sub> = 10V, I <sub>O</sub> = 1A          | 20 kHz                  |

| Short Circuit<br>Current Limit | V <sub>IN</sub> = 10V                               | 1.3A                    |

| Load Regulation                | V <sub>IN</sub> = 10V,<br>I <sub>O</sub> = 0.2 - 1A | 3 mV                    |

| Line Regulation                | $\Delta V_{1N} = 10 - 20V,$ $I_0 = 1A$              | 6 mV                    |

| Efficiency                     | V <sub>IN</sub> = 10V, I <sub>O</sub> = 1A          | 80%                     |

| Output Ripple                  | V <sub>IN</sub> = 10V, I <sub>O</sub> = 1A          | 10 mVp-p                |

FIGURE 16. 5V, 1 Amp Switching Regulator, Foil Side

FIGURE 17. Stuffing Diagram, Component Side.

# THE STEP-UP SWITCHING REGULATOR

Figure 18 shows the basic circuit for a step-up switching regulator. In this circuit Q1 is used as a switch to alternately apply  $V_{IN}$  across inductor L1. During the time,  $t_{ON}$ , Q1 is ON and energy is drawn from  $V_{IN}$  and stored in L1;D1 is reverse biased and  $I_{O}$  is supplied from the charge stored in  $C_{O}$ . When Q1 opens,  $t_{OFF}$ , voltage V1 will rise positively to the point where D1 turns

ON. The output current is now supplied through L1,D1 to the load and any charge lost from  $C_0$  during  $t_{ON}$  is replenished. Here also, as in the step-down regulator, the current through L1 has a DC component plus some  $\Delta I_L$ .  $\Delta I_L$  is again selected to be approximately 40% of  $I_L$ . Figure 19 shows the inductor's current in relation to Q1's ON and OFF times.

FIGURE 18. Basic Step-Up Switching Regulator

FIGURE 19

From

$$\Delta I_L = \frac{V_L T}{L}$$

,  $\Delta I_L^+ \simeq \frac{V_{IN} t_{ON}}{L1}$

and

$$\Delta I_L^- \simeq \frac{(V_o - V_{IN})^{\dagger}OFF}{L1}$$

Since  $\Delta I_L^+ = \Delta I_L^-$ ,  $V_{INTON} = V_{OTOFF} - V_{INTOFF}$ ,

and neglecting VSAT and VD1

$$V_0 \simeq V_{IN} \left(1 + \frac{t_{ON}}{t_{OFF}}\right)$$

The above equation shows the relationship between  $V_{\mbox{\scriptsize IN}},\,V_{\mbox{\scriptsize O}}$  and duty cycle.

In calculating input current I<sub>IN(DC)</sub>, which equals the inductor's DC current, assume first 100% efficiency:

PIN = IIN(DC)VIN

$$P_{OUT} = I_0 V_0 = I_0 V_{IN} \left(1 + \frac{t_{ON}}{t_{OFF}}\right)$$

for

$$\eta$$

= 100%, P<sub>OUT</sub> = P<sub>IN</sub>

$$I_0 V_{IN} \left(1 + \frac{t_{ON}}{t_{OFF}}\right) = I_{IN(DC)} V_{IN}$$

$$IIN(DC) = I_0 \left(1 + \frac{t_{ON}}{t_{OFF}}\right)$$

This equation shows that the input, or inductor, current is larger than the output current by the factor (1 +  $t_{ON}/t_{OFF}$ ). Since this factor is the same as the relation between  $V_O$  and  $V_{IN}$ ,  $I_{IN}(DC)$  can also be expressed as:

$$I_{IN(DC)} = I_0 \left( \frac{V_0}{V_{IN}} \right)$$

So far it is assumed  $\eta=100\%$ , where the actual efficiency or  $\eta_{\text{MAX}}$  will be somewhat less due to the saturation voltage of Q1 and forward on voltage of D1. The internal power loss due to these voltages is the average I<sub>L</sub> current flowing, or I<sub>IN</sub>, through either V<sub>SAT</sub> or V<sub>D1</sub>. For V<sub>SAT</sub> = V<sub>D1</sub> = 1V this power loss becomes I<sub>IN</sub>(DC) (1V).  $\eta_{\text{MAX}}$  is then:

$$\eta_{MAX} = \frac{P_o}{P_{IN}} = \frac{V_o I_o}{V_o I_o + I_{IN} (1V)} = \frac{V_o I_o}{V_o I_o + I_o \left(1 + \frac{t_{ON}}{t_{OFF}}\right)}$$

From

$$V_0 = V_{IN} \left(1 + \frac{t_{ON}}{t_{OFF}}\right)$$

$$\eta_{\text{max}} = \frac{V_{1N}}{V_{1N} + 1}$$

This equation assumes only DC losses, however  $\eta_{MAX}$  is further decreased because of the switching time of Q1 and D1.

In calculating the output capacitor  $C_0$  it can be seen that  $C_0$  supplies  $I_0$  during  $t_{ON}$ . The voltage change on  $C_0$  during this time will be some  $\Delta V_C = \Delta V_0$  or the output ripple of the regulator. Calculation of  $C_0$  is:

$$\Delta V_0 = \frac{I_0 t_{ON}}{C_0}$$

or  $C_0 = \frac{I_0 t_{ON}}{\Delta V_0}$

From

$$V_0 = V_{IN} \left( \frac{T}{t_{OFF}} \right)$$

;  $t_{OFF} = \frac{V_{IN}}{V_0} T$

where T =

$$t_{ON} + t_{OFF} = \frac{1}{f}$$

$$t_{ON} = T - \frac{V_{IN}}{V_{O}}T = T\left(\frac{V_{O} - V_{IN}}{V_{O}}\right)$$

therefore:

$$C_{O} = \frac{I_{O}T\left(\frac{V_{O} - V_{IN}}{V_{O}}\right)}{\Delta V_{O}} = \boxed{\frac{I_{O}(V_{O} - V_{IN})}{f\Delta V_{O}V_{O}}}$$

where:  $C_0$  is in farads, f is the switching frequency,  $\Delta V_0$  is the p-p output ripple

Calculation of inductor L1 is as follows:

$$L1 = \frac{V_{IN}t_{ON}}{\Delta I_{L}^{+}}$$

, since during  $t_{ON}$ ,

VIN is applied across L1

$$\Delta I_{Lp \cdot p} = 0.4 I_L = 0.4 I_{IN} = 0.4 I_0 \left( \frac{V_0}{V_{IN}} \right)$$

, therefore:

$$L1 = \frac{V_{IN}t_{ON}}{0.4I_{O}\left(\frac{V_{O}}{V_{IN}}\right)} \text{ and since } t_{ON} = \frac{T(V_{O} - V_{IN})}{V_{O}}$$

$$L1 = \frac{2.5 \text{ V}_{1N}^2 (\text{V}_0 - \text{V}_{1N})}{\text{f I}_0 \text{V}_0^2}$$

where :L1 is in henrys, f is the switching frequency in Hz

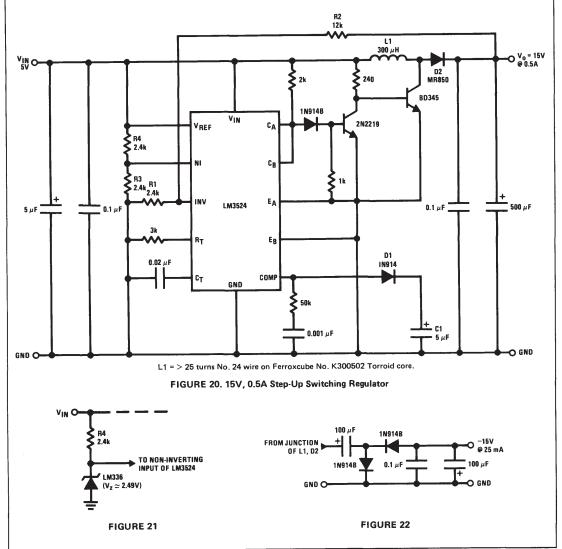

To apply the above theory, a complete step-up switching regulator is shown in Figure 20. Since  $V_{IN}$  is 5V,  $V_{REF}$  is tied to  $V_{IN}$ . The input voltage is divided by 2 to bias the error amplifier's inverting input. The output voltage is:

$$V_{OUT} = \left(1 + \frac{R2}{R1}\right) \cdot V_{INV} = 2.5 \cdot \left(1 + \frac{R2}{R1}\right)$$

The network D1, C1 forms a slow start circuit.

This holds the output of the error amplifier initially low thus reducing the duty-cycle to a minimum. Without the slow start circuit the inductor may saturate at turn-on because it has to supply high peak currents to charge the output capacitor from 0V. It should

also be noted that this circuit has no supply rejection. By adding a reference voltage at the non-inverting input to the error amplifier, see *Figure 21*, the input voltage variations are rejected.

The LM3524 can also be used in inductorless switching regulators. *Figure 22* shows a polarity inverter which if connected to *Figure 20* provides a -15V unregulated output.

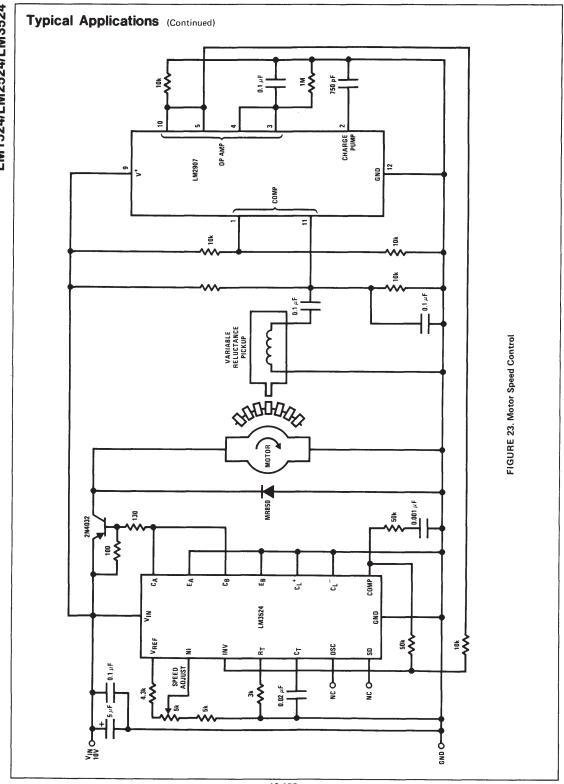

## MOTOR SPEED CONTROL

Figure 23 shows a regulating series DC motor speed control circuit using the LM3524 for the control and drive for the motor and the LM2907 as a speed sensor for the feedback network.