Options Increase For Effective Use Of High Performance Winchesters

by Julie Pingry, Senior Editor

Digital

Design Vol 15 No9 Sept 1985 Pages 62-64,

66, 68, 70

Despite advances in small format Winchesters, high performance computers continue to use 8" and larger disk drives with very high capacities and fast access times. But the specifications of these large format disk drives alone do not assure optimal performance for system disk operations. The choice of interface and controller as well as the development of file and driver software can make the performance of the same drive very different in various systems.

Traditionally bound to the SMD interface, 8”, 10 ½” and 14" Winchesters' performance have challenged standard 10 MHz SMD controllers. To keep disk rotation speed constant with increased bit densities, the data transfer rate to and from the disk must increase. Faster versions of SMD, called HSMD, ESMD or SMD-E, have sped up the same basic interface to 15-24 MHz, or up to 3 Mbit/sec transfer off the disk. Although these rates are adequate for most current drives, two new parallel Intelligent Peripheral Interfaces, IPI-2 and IPI-3, are well on the way to standardization and acceptance by the industry. With a parallel interface, more speed will be possible without stretching the specification or using expensive components.

Even with a well thought-out drive interface and a fast-access disk, systems can find disk I/O a major bottleneck. The proper controller for the system must be chosen; one with fewer frills may require more effort in system software development, but can provide greater raw speed and less bus overhead. Various system applications require different schemes for seeking, caching and disk utilization. A primary requirement is a good operating system interface to the disk. Writing drivers for a particular combination of controller and disks may not be an easy task, but it can make the difference between medium- and high performance from an otherwise well-designed system.

System

Integration

Keys

For disk operations to match demands from high-end systems with internal buses and open system buses dedicated to I/O, data must be efficiently transferred from disk to I/O bus. Multitasking operating systems, multiuser and multiprocessor systems change the type of disk access that is most efficient.

Simple look-ahead caches are useful for single task, single user systems; but the disk segmentation under UNIX, for example, dramatically reduces the cache hit rate. Likewise, interleaving of data on the disk is useful for many systems, but in high performance multitasking configurations, disk access speed may be slowed considerably if the disk and controller cannot perform non-interleaved seeks.

When testing controller/disk combinations, consider the application to which the system will be put. Although this seems obvious, it may not be standard practice. Generic testers, like data sheet specifications, focus only on raw speed. In systems with extensive disk interaction, buffering, caching and seek optimization have a large impact on performance. These features are not nearly as important as pure data transfer speed for systems making less frequent large block requests, single application processors or accelerators.

Another area to consider is whether there may be more than one disk drive attached to the system and controller. If so, overlapped seeks can enhance speed. Command chaining and ordering of seeks further aid multiple drive systems. With current drives at several hundred Mbytes to one Gbyte, multiple data channels could aid access to that quantity of information as well. Both SMD and IPI have dual-port capability built into the specification; although primarily used for fault tolerance, with the appropriate software and architecture, this can also be used for dynamic pathing in very high performance systems.

Writing software drivers is also critical. Controller houses should provide some driver support; customers should devote time and resources to developing appropriate I/O drivers. Despite the time needed to write a good driver, better I/O could affect a system's competitive position once on the market. Testing, controller choice and appropriate software drivers are critical. No matter how good the system's architecture is, slow access to disk data can hide or destroy performance. One choice that must be made early is that of drive and host interface.

Stretching

SMD

Storage Module Drive (SMD) is the traditional device interface choice for high-performance systems. Since its introduction as an interface for Control Data Corp. (Minneapolis, MN) removable disk drives, the specification has been improved to keep pace with available disk drives. In addition to the original 1.2 Mbyte/sec data rate off the disk, a 1.8 Mbyte/sec or 15 MHz version has been available for several years. This change required no modifications in controllers or the specification. Fujitsu (San Jose, CA) has increased speed to 20 MHz or 2.4 Mbytes/sec in its HSMD drive interface. Even at that speed, compatibility was ensured by working with controller houses.

Drives using IBM 3380 technology record

12 million bits/sq. in.,

so data comes off the disk extremely fast. Control Data

has increased the speed

for its SMD-E (extended) interface to as much as 3

Mbytes/sec or 24 MHz to

accommodate these drives. ECL drivers and receivers are

needed for the servo,

read and write clock and read and write data signals to

operate at this speed.

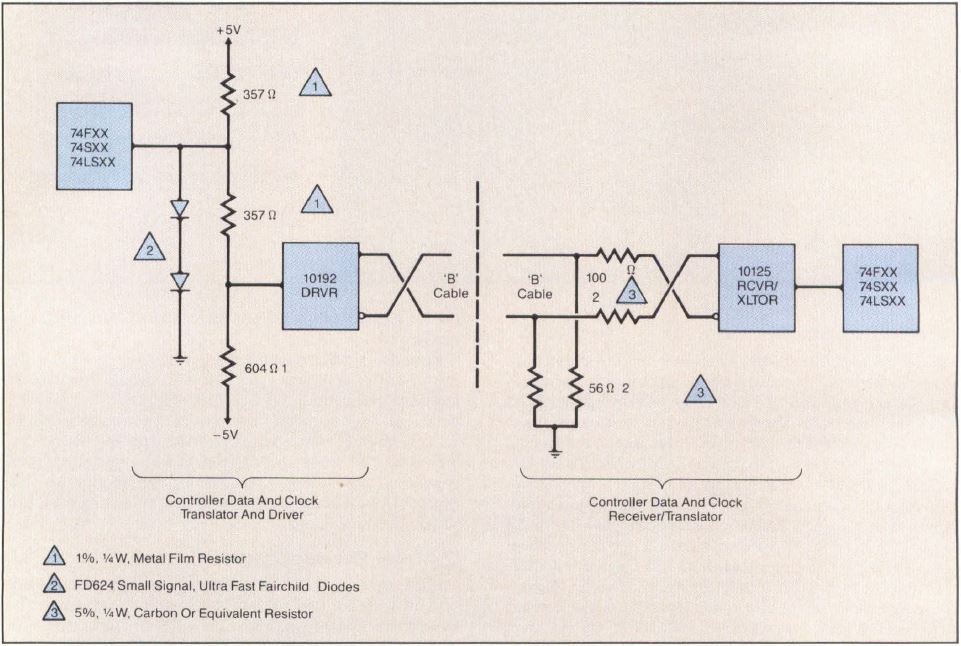

Figure 1 shows the

minimum (passive) TTL to ECL translation circuitry

required

for existing SMD products to be used at 24 MHz speeds.

Figure 1: 24 MHz Transfer Rate on SMD

Figure 1: To achieve 24 MHz data transfer rates, SMD disk

drives need to use ECL drivers and receivers. As published

in the CDC SMD-E specification, this is the minimum

(preferred passive) translator circuitry needed for all

signals on current TTL SMD systems to reach that speed .

SMD was the first standard adopted by the ANSI X319.3 group. The interface is so established that the federal government has adopted it as a FIPS standard. ANSI revisions (included in the government standard) covering ESMD, HSMD and SMD-E improve not only speed but also error handling and diagnostic features. Despite the complexity of SMD, the established manufacturing history for drives and controllers may give it a long life.

Most drives and systems will not need more speed than the 20 or 24 MHz of the extended SMD specifications in the next few years. Furthermore, as Dal Allen of ENDL (Saratoga, CA) points out, few controllers or drivers have been developed from scratch recently, since established standard interfaces have served most of the market. This may make ramp-up lengthy on controllers and silicon for implementing interfaces that have not evolved from an older standard, further prolonging the life of SMD implementations.

Parallel

Development

The IPI interface, designed specifically for high-performance systems with fast disk access, is the natural next-generation interface for systems that have used SMD. In a twist indicative of today's market emphasis on standards, IPI is being defined by an ANSI committee. Many major disk drive, controller, IC and systems manufacturers have had a hand in developing the specifications before any implementations have appeared.

IPI's main advantages are that it is not only a standardized interface, but also a parallel interface, and thus more expandable to future system disk access speed requirements. With 16 parallel lines, speeds as high as 80 MHz or 10 Mbytes/sec are currently defined. In contrast, SMD may have reached its practical limits at 24 MHz. High-performance system houses that do not wish to redesign their controller and interface in the next five years should consider the relative lifespans of SMD and IPI-2 when deciding which to use.

Two IPI interfaces are being specified: IPI-2, a drive-level interface, and IPI-3, an intelligent system interface. The two do not depend on each other; the device-level IPI-2 can function with many host interfaces, and IPI-3 can operate with other device interfaces as well.

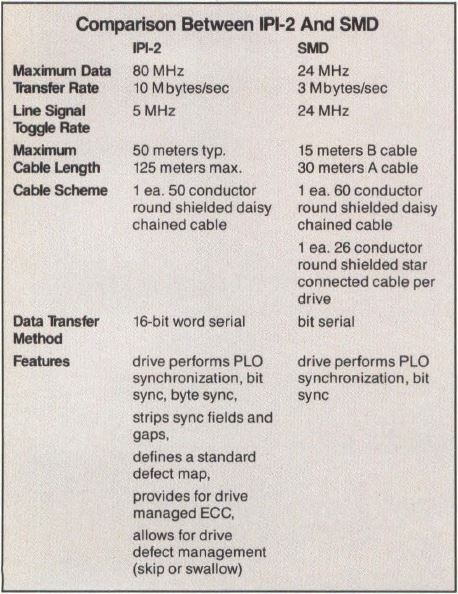

IPI-2 compares directly to SMD, as a

device-specific command

set for disk drives. (One for tape drives is also in

development.) As shown in

Table 1, the

higher-speed IPI also allows longer, less expensive

cabling. The

added drive functions are a fallout of the parallel

interface, and still

require interpretation by the controller. As with SMD, the

drive and controller

must be tightly coupled.

Table 1: Comparison Between IPl-2 And SMD

Table 1: This is how Simulex compares

IPl-2 with SMD. IPl-2 is faster and permits less

expensive, longer cabling to be used. Both are

device-level interfaces, but because IPI-2 is parallel and

the drive requires a serializer/deserializer (Serdes),

more functions can be performed by the drive.

IPI-2 uses two 8-bit data buses with parity and six interface control signals. Device control is through bus control octets on the data buses, with the A bus serving master (controller) to slave (drive) communication and the B bus for slave to master. These bus control octets are the first eight bits put out on bus A, not electrical signals as used in SMD for device control. Four types of bus control octets are used: read, write, command (like the Tag Code on SMD) and response (for disk status reports to the controller). Once these are passed, both A and B buses are used in the same direction to transfer information. Disk data is not buffered off the drive, but sent directly to the controller at disk speed.

To enforce true compatibility between disk drives meeting the IPI-2 standard, a two-chip set is being developed by Simulex (Tustin, CA). Eight drive manufacturers have submitted purchase orders for Simulex's chip designs: Control Data/MPI, Fujitsu, Priam (San Jose, CA), Century Data Systems (Anaheim, CA), Ampex (Cupertino, CA), NEC (Boxborough, MA), Pertee (Chatsworth, CA) and STC (Louisville, CO). Others can place orders, with the understanding that their shipments may be later. The purchase includes chip emulator boards and an SMD adapter board as well as prototypes, software for use with the 8051 microcontroller and rights to the design and database. The emulator boards for each chip and the SMD adapter are to be delivered to the original eight buyers in October; the rest are scheduled for shipment in 1986.

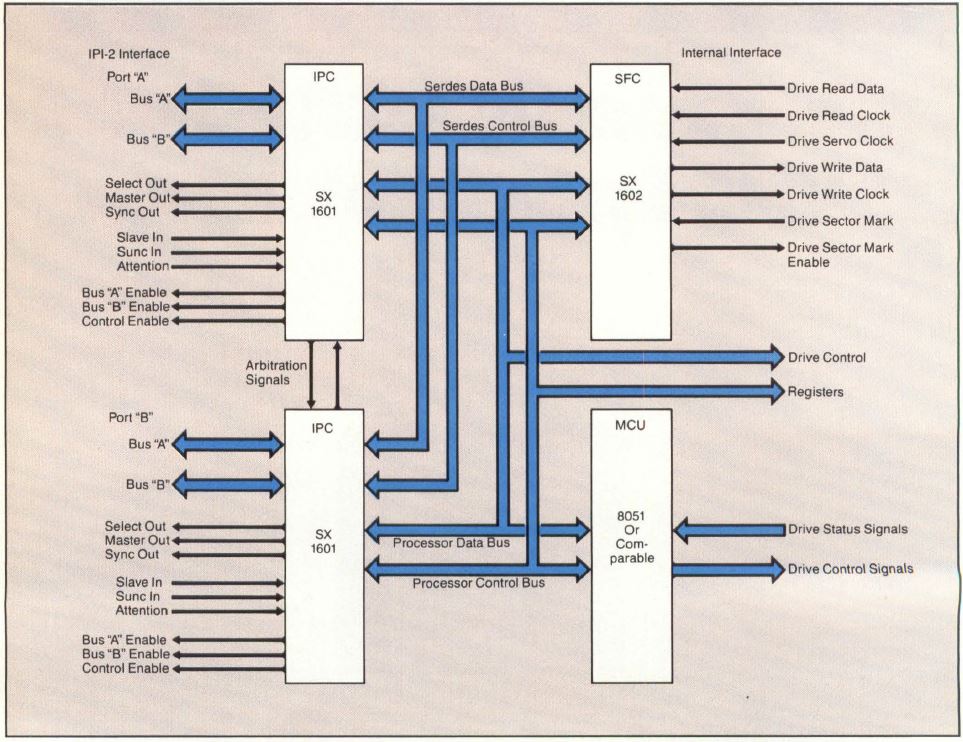

The two chips are the SXl60l Interface

Protocol Circuit

(IPC) and the SX1602 Serdes (serializer-deserializer)

Formatter Circuit (SFC)

(Figure 2); both are

CMOS gate arrays. The IPC interprets bus states, sending

Command or Response bus controls to the drive

microcontroller and Read or Write

controls to the SFC for execution. The interface to the

microcontroller on either

IC is directly timing compatible with the 8051, MC680l or

Z8 and adaptable for

other 8-bit processors. Figure 2 shows a switched

dual-port IPI-2 drive

configuration; systems with the speed and performance that

have driven

development of IPI-2 often demand the reliability of two

ports. Only one IPC is

needed for single-port drives.

Figure 2: SXl60l Interface Protocol

Circuit and SX1602 Serdes Formatter Circuit (SFC)

Figure 2: With two Interface Protocol

Circuits, a Serdes Formatter Circuit and an 8-bit

microcontroller, dual-port IPl-2 can be implemented in

disk drives with minimal trouble. The Simulex chip set

also ensures a subset of compatibility for all IPl-2

drives that use them.

Functions to record, recover and format data on a disk, as well as serializing and deserializing off the interface, are provided by the SFC. It acts as a slave to the microcontroller. Having the Serdes and microcontroller on the disk drive opens up new possibilities for the partitioning of functions. In Table 1, functions such as locating the beginning of field and stripping off sync bytes are performed by the drive, easing demands on the controller and on the timing coordination between drive and controller. The significant task of recording and reading out the drive defect map can also be eased with IPI-2. The drive's native chip set and microprocessor can be used for media verification at manufacture, and once in the system, the controller can command the drive to read out its defect map.

The two-chip IPI-2 interface assures standardization of a subset of IPI-2 functions in eight major manufacturers' drives. Once these drives are out, controllers will likely follow. Bob Morris, manager of development engineering at Simulex, predicts that even though no similar chip set is under development for the controller side, mainframe system houses that want to accommodate 24 MHz drives may produce controllers next year. Control Data has used gate arrays to implement an IPI-2 controller and indicated a willingness to license those. Siemens (Munich, West Germany) is also working on an IPI-2 controller that it may make available on an OEM basis. IPI-2 may be implemented sooner than other new interfaces because it is a drive level interface, not an intelligent interface; this should make writing software drivers easier than for intelligent interfaces like SCSI and IPI-3.

Using

Interface

Intelligence

Although they are more difficult to design, debug and write software for, intelligent disk drive interfaces are becoming popular. Since the system only addresses the device logically, with no need to know the mechanics of the device being used, intelligent interfaces provide device-independence. This translates into a single system interface for many peripherals, as well as easy integration and upgrade. They also offer low cost for single-drive systems by incorporating many functions into the drive and good performance for multiple drive systems by a large repertoire of functions. Like IPI-3, SCSI is an intelligent interface; it is now offered on some high-performance drives.

SCSI is an 8-bit parallel bus that can interface between as many as eight host or slave devices. Several 8” Winchesters are now available with an embedded SCSI interface. Priam's 227 Mbyte 806 and 344 Mbyte 807 models with SCSI are being shipped mainly to CAD, graphics and European system manufacturers. Another example is Amcodyne's (Longmont, CO) fixed/removable Winchesters with SCSI. Fujitsu has developed an SCSI controller for its line of 8" drives; using the 337 Mbyte model, 1.38 Gbytes are available to one controller. NCR's (Colorado Springs, CO) SCSI chip (Digital Design, December 1984, p.80) has made it possible for a large number of firms to offer SCSI products early. Still, SCSI is primarily aimed at cost conscious, not high-performance, applications. The SCSI bus operates at a maximum of 4 Mbytes/sec, and with SMD at 3 Mbytes/sec, the advantages for high-end systems are less than for applications where SCSI replaces ST506 or SASI.

IPI-3 is a similarly intelligent, device-independent peripheral bus. But like IPI-2, it is designed for very high performance. Underlying layers are identical for IPI-2 and IPI-3: electrical and mechanical specifications are called IPI-0; IPI-1 is the bus protocol and state machine. With a maximum speed of over 10 Mbytes/sec, IPI-3 can provide the same isolation from changes in specific peripherals as SCSI for much higher performance systems. IPI-3 also has a richer command set than SCSI. Minicomputer or mainframe manufacturers can design an IPI-3 system interface and plug various peripherals into the subsystem as needed without affecting the system software.

At the IPI Forum, conceived by Dal Allen, industry support for IPI was apparent, and product plans were also unveiled. A range of products from controllers to connectors and chips for both IPI-2 and IPI-3 were discussed. Interphase (Dallas, TX) is developing two controllers for IPI-3. Siemens is designing an IPI-3 host bus adapter for its 7.500 computer. Gould AMI (Santa Clara, CA) has developed a chip for IPI-3 controllers, but there was no commitment to outside availability. A connector for IPI systems from AMP (Harrisburg, PA) was revealed. Perkin-Elmer (Tinton Falls, NJ) expressed its desire for IPI-3 to remove device I/O from the operating system and put it into controllers. Even IBM announced that its future OEM storage products would use an IPI interface.

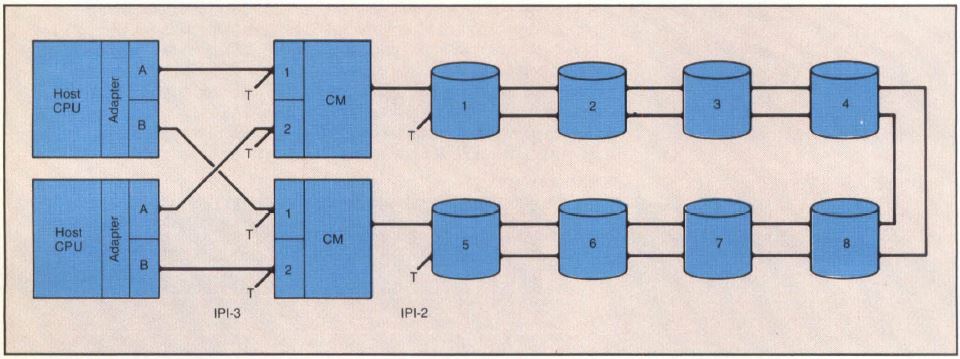

One of the most important announcements

was Control Data/Magnetic

Peripherals Inc.'s controller for IPI-3 to IPI-2

interfacing called CM3 (Figure

3). Planned for release in mid-1986, the

CDC/MPI board will create a working

subset of IPI-3. Initial users may include Honeywell,

Sperry and Control Data.

With such a controller, only a host adapter for the

specific host system needs

to be designed. And even though IPI-2 and IPI-3 do not

depend on each other,

having the same cabling and bus protocol may streamline

I/O subsystems.

Figure 3: Control Data's CM3 Control Module

Figure 3: Control Data's CM3 Control Module is an IPI-2 to

IPI-3 controller to be available mid-1986. This is a

typical system configuration with dual-port drives; 50m

cables can be used on the host side and 15m cables on the

drive side.

At NCC, Hitachi America (San Bruno, CA) demonstrated the SC801 IPI-3 controller. Available in the first half of 1986, the SC801 can handle up to eight Hitachi DK815 8.8" drives. The controller will include multi port capability and may be offered as an OEM product.

The many options available with intelligent interfaces make compatibility across manufacturers virtually unavailable. This is a major drawback for intelligent interfaces. Users of SCSI can attest to the lack of interchangeability. IPI-3 proponents claim that since the interface has not evolved, but has been started from scratch, those problems will not surface. The CDC/MPI Control Module provides the basis for a compatible IPI-3 subset. Dal Allen has also published a document called ENDLFacto that defines a usable working subset; the document is available for $75 by writing to ENDL, 14426 Black Walnut Court, Saratoga, CA 95070.

New intelligent disk drive interfaces will dictate a different partitioning of functions between the disk drive and the controller. Some flexibility may be taken away from the operating system, with so many of the error management, buffering and seek ordering functions removed to the I/O subsystem. Depending on the system objectives, this removal of functions from the OS may be positive or negative.

Drive

Implications

Emerging high-performance interfaces designed for maximum usage of current disk drives will also allow more advanced disk drives and different disk subsystem configurations to penetrate the market. IPI, with the capability to transfer data off disks at up to 80 MHz, can be used with vertically recorded disks. Multiple head disk drives, though a niche market, will also be easier to employ at higher data transfer rates to the system. And with intelligent interfaces, strings of drives can be closely controlled.

Fujitsu's M2350A Parallel Transfer Disk (PTD) is one product that will demand higher data transfer rates. A current subsystem from Storage Concepts (Westminster, CA) uses a proprietary interface to transfer up to 1.86 Mbytes/sec on five channels per M2350A drive, for 9.3 Mbytes/sec total. This speed will be available via IPI as well. The standard allows others to use these PTD drives without designing a proprietary controller and I/O scheme.

Although the technology is not new, vertical recording has not taken hold because controllers and interfaces could not handle data at the speeds they come off these surfaces. Lanx (San Jose, CA) is one of the few companies working with vertical recording that has been able to weather the slim business. Until now, its sales have primarily been standard media, but by next year, IPI drives and controllers that can handle faster data transfer may make vertically recorded media marketable.

Another type of disk drive that has had a limited market is multiple-head drives. Companies like Alpha Data (Chatsworth, CA) are content with a niche market. But large firms including Fujitsu and CDC also make multiple-head drives. To make use of drives such as Alpha Data's Atlas with 54 moving heads, a faster disk transfer is desirable. For applications that require extensive disk use, more heads assures faster access to data. But only if the interface and controller are properly designed to accept data from heads in rapid succession will the extra performance of this type of disk be seen in system applications...

Multiple heads can also be provided to a controller by using more drives in a string. Again, the speed of an IPI interface may be the factor that allows this configuration to be effective in a system. Systems not designed to accept data from more than one head cannot necessarily optimize the capabilities of multiple head configurations, whether on one disk or many.

For the first time in the past few years, choices are opening up for high-end disk I/O systems. The risk of using a new interface may extend the life of current designs by several years. But extended SMD and IPI interfaces are well documented and will accommodate the disk technology already developed. So interface changes are not an isolated issue in system configuration, but also affect range of drives that can be used to their maximum.