# **RS/6000 Scientific and Technical Computing: POWER3 Introduction and Tuning Guide**

Stefan Andersson, Ron Bell, John Hague, Holger Holthoff Peter Mayes, Jun Nakano, Danny Shieh, Jim Tuccillo

**International Technical Support Organization**

http://www.redbooks.ibm.com

SG24-5155-00

International Technical Support Organization

## **RS/6000 Scientific and Technical Computing: POWER3 Introduction and Tuning Guide**

October 1998

#### — Take Note!

Before using this information and the product it supports, be sure to read the general information in Appendix D, "Special Notices" on page 199.

#### First Edition (October 1998)

This edition applies to XL Fortran Version 5.1.1 (5765-C10 and 5765-C11) running under AIX Version 4.3 (5765-C34) on an RS/6000 43P 7043 Model 260 Workstation.

#### – Note

This book is based on a pre-GA version of a product and may not apply when the product becomes generally available. We recommend that you consult the product documentation or follow-on versions of this redbook for more current information.

Comments may be addressed to: IBM Corporation, International Technical Support Organization Dept. JN9B Building 045 Internal Zip 2834 11400 Burnet Road Austin, Texas 78758-3493

When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you.

#### © Copyright International Business Machines Corporation 1998. All rights reserved

Note to U.S Government Users – Documentation related to restricted rights – Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

## Contents

| Figuresix                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Preface.       xiii         The Team That Wrote This Redbook.       xiv         Comments Welcome       xvi                                                                                                                                                                                                                                                                                                                                            |

| Chapter 1. Introduction11.1 RS/6000 Processor Evolution11.1.1 POWER111.1.2 POWER221.1.3 PowerPC31.1.4 POWER331.2 SMP-Based System Views31.2.1 Job Level Parallelism with Single CPU Jobs31.2.2 Automatic Parallelization (Fortran)41.2.3 Compiler Directives41.2.4 Message Passing Interface41.2.5 Using POSIX Threads51.2.6 Combined MPI/Threads Paradigm5                                                                                           |

| Chapter 2. The POWER3 Processor       7         2.1 Processor Overview       7         2.2 POWER3 Execution Core       8         2.3 POWER3 Roadmap       12         2.4 POWER3-Based Systems       13         2.4.1 RS/6000 43P 7043 Model 260       13         2.4.2 IBM RS/6000 SP Nodes       15         2.4.3 DOE ASCI Project       15                                                                                                          |

| Chapter 3. XL Fortran Version 5       17         3.1 SMP Support       17         3.2 Support for POWER3       19         3.3 64-Bit Support       19         3.3.1 Fortran Storage Classes       20         3.3.2 32-Bit Mode       21         3.3.3 32-Bit Mode, Large Address Space Model       22         3.3.4 64-Bit Mode       22         3.3.5 Compiler Defaults and Limits       23         3.3.6 64-bit Integer Arithmetic Support       23 |

| 3.4 Performance Improvements over Previous XL Fortran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 4. Using the SMP Feature of XL Fortran294.1 How to Compile, Link, and Execute294.2 Consideration of Storage Classes in 32-Bit Mode334.3 Conditions for Automatic Parallelization364.4 Automatic Parallelization - Parallelism Analysis384.4.1 Examples of Parallelism Analysis384.4.2 XL Fortran Messages Related to Parallelization444.5 Automatic Parallelization - Cost-Based Analysis454.5.1 Cost-Based Analysis - Single Loops454.5.2 Cost-Based Analysis - Nested Loops464.5.3 How to Affect the Decision of Cost-Based Analysis474.6 Directives504.6.1 PARALLEL DO Compiler Directive514.6.2 PARALLEL SECTIONS Compiler Directive534.6.3 PERMUTATION Compiler Directive544.6.4 SCHEDULE Compiler Directive544.6.5 THREADLOCAL Compiler Directive564.7 NUM_PARTHDS Intrinsic Function564.8 XLSMPOPTS Environment Variable574.9 OpenMP Porting Considerations58 |

| Chapter 5. Performance Libraries655.1 The ESSL Library655.1.1 Benefits of Using ESSL695.1.2 How to Use ESSL705.1.3 Performance Examples of ESSL705.2 MASS735.2.1 How to Use the MASS Library745.2.2 Performance of the MASS Library755.2.3 Further Tuning Possibilities Using Vector MASS77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 6. Message Passing Interface816.1 MPI in an SMP Environment816.2 MPI Communication Rates83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 7. Performance and Tuning Analysis877.1 Relevant Information877.2 CPU Tuning907.2.1 Unrolling907.2.2 Divides937.2.3 Floating Point to Integer Conversion947.2.4 Fractional Part of a Number95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>7.3 Memory Tuning</li> <li>7.3.1 Copy.</li> <li>7.3.2 Multiple Streams.</li> <li>7.3.3 DAXPY.</li> <li>7.3.4 Loads and Stores.</li> <li>7.3.5 Prefetching Individual Cache Lines.</li> <li>7.4 Large Stride.</li> <li>7.4.1 Cache Effects.</li> <li>7.4.2 Translation Lookaside Buffer Effects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95<br>97<br>98<br>101<br>101<br>102<br>102                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Chapter 8. Fortran Tuning Guide for Maximum Megaflops8.1 The Tuning Process8.1.1 Tuning for I/O8.1.2 Locating the Hot Spots (Profiling)8.1.3 Use Pre-tuned Code, Such As ESSL8.1.4 Hand Tune the Code8.2 Recommended Compiler Options8.3 Architecture Independent Hand Tuning Review8.3.1 Basic Coding Practices for Performance8.3.2 Commonly Occurring Examples8.4 Key Aspects of POWER3 (Model 260) Architecture8.4.1 The POWER3 (Model 260) Level 1 Data Cache8.4.2 The POWER3 (Model 260) Level 2 Data Cache8.4.3 The Translation Lookaside Buffer (TLB)8.4.4 The Superscalar Floating Point Units and Peak Megaflops8.5 Tuning for Floating Point Performance on POWER3 (Model 260)8.5.1 Letting the Compiler Do the Tuning8.5.2 Getting and Understanding an Object Code Listing8.5.3 Tuning for the L1 Cache8.5.4 Tuning for the CPU8.6 Some Comments on Parallel Coding for Model 260 | 107<br>108<br>109<br>111<br>112<br>112<br>114<br>115<br>116<br>119<br>123<br>123<br>123<br>126<br>127<br>127<br>129<br>135 |

| Chapter 9. Throughput Measurements         9.1 Copy Program         9.2 User Programs         9.3 Case Study: Matrix Multiplication         9.3.1 The Computational Kernel         9.3.2 Single Processor Implementation of DGEMM         9.3.3 Automatically Parallelized DGEMM         9.3.4 MPI Implementations         Chapter 10. Kernels, Codes, and Benchmarks         10.1 GAMESS         10.2 Oil Reservoir Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 147<br>149<br>150<br>151<br>153<br>156<br>157<br>159<br>159                                                                |

| 10.3 Weather Forecast Code10.4 Computational Fluid Dynamics: FIRE10.5 Crash Worthiness Analysis: RADIOSS10.6 Finite Difference Kernel10.7 Iterative Eigenvalues Solver                                                                                          | 162<br>165<br>167                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Appendix A. Industry Standard BenchmarksA.1 LINPACK BenchmarkA.2 SPEC95A.3 STREAMA.4 NAS NPB 1.0                                                                                                                                                                | 173<br>174<br>174                                                                              |

| Appendix B. Enabling Vector Codes to POWER3         B.1 Data Access         B.2 Data Dependency and Recursive Code         B.3 Vector Length         B.4 Conditional Processing                                                                                 | 177<br>177<br>178                                                                              |

| Appendix C. Threads                                                                                                                                                                                                                                             | 181<br>182<br>183<br>183<br>185<br>185<br>185<br>188<br>191<br>192<br>192<br>193<br>193<br>193 |

| Appendix D. Special Notices                                                                                                                                                                                                                                     | 199                                                                                            |

| Appendix E. Related Publications       2         E.1 International Technical Support Organization Publications       2         E.2 Redbooks on CD-ROMs       2         E.3 Other Publications       2         E.4 Information Available on the Internet       2 | 203<br>203<br>203                                                                              |

| How to Get ITSO Redbooks         2           How IBM Employees Can Get ITSO Redbooks         2                                                                                                                                                                  |                                                                                                |

| How Customers Can Get ITSO Redbooks |     |

|-------------------------------------|-----|

| List of Abbreviations               | 211 |

| Index                               | 213 |

| ITSO Redbook Evaluation             | 221 |

## Figures

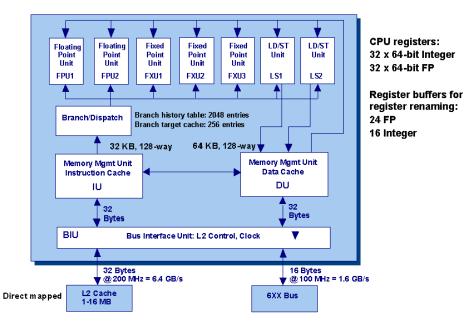

| 1.  | POWER3 Processing Units (Model 260)                                 | 8              |

|-----|---------------------------------------------------------------------|----------------|

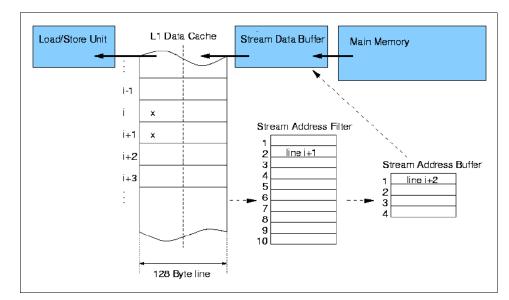

| 2.  | Data Prefetch Overview                                              | 1              |

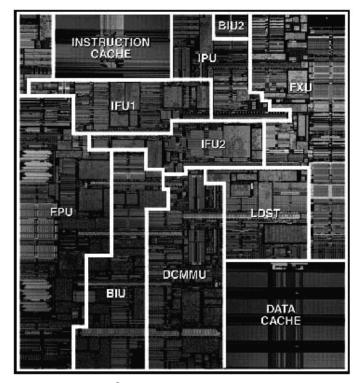

| 3.  | POWER3 Chip Layout: 270 mm <sup>2</sup> Die, 15 Million Transistors | 3              |

| 4.  | Logical View of the Model 2601                                      | 4              |

| 5.  | XL Fortran Version 5 Compiler Architecture 1                        | 8              |

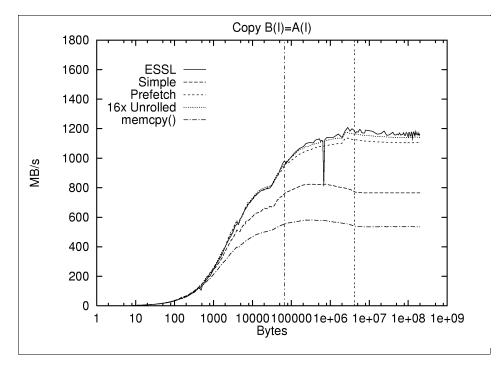

| 6.  | Copy Rates of a Double Precision Array                              | '1             |

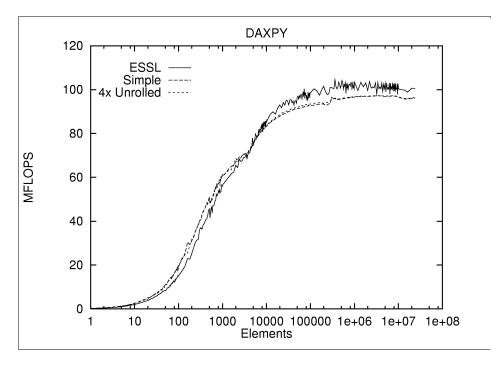

| 7.  | DAXPY Comparison7                                                   | '2             |

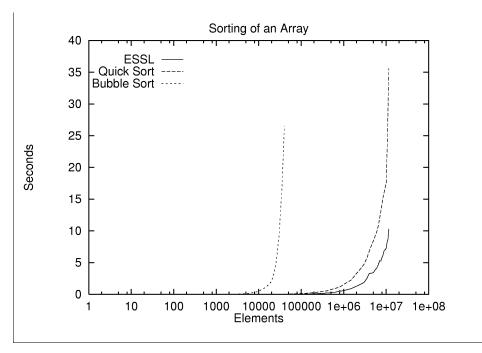

| 8.  | Three Sorting Algorithms                                            | '3             |

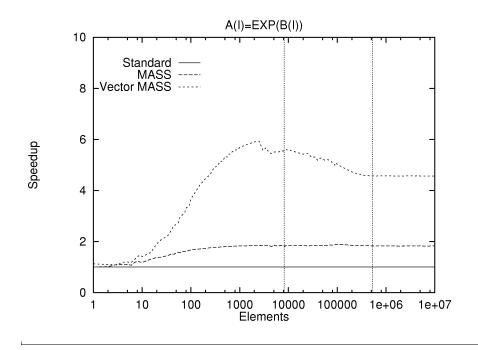

| 9.  | MASS Use of Exp()                                                   | 7              |

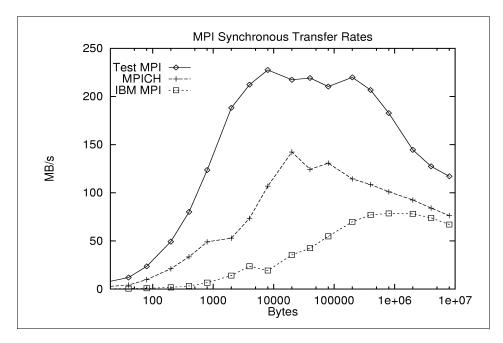

| 10. | MPI Synchronous Transfer Rates                                      | 35             |

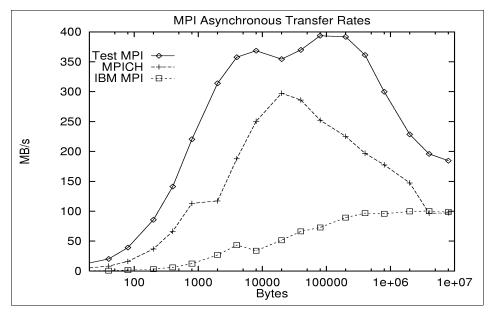

| 11. | MPI Asynchronous Transfer Rates                                     | 35             |

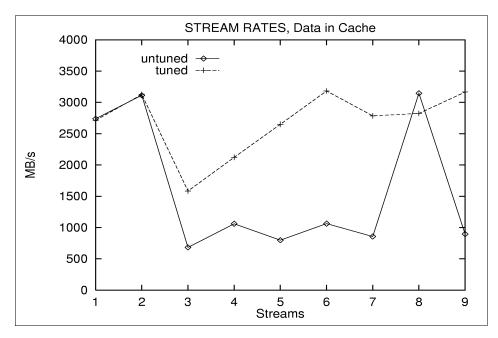

| 12. | Stream Rates for Data in Cache                                      | 93             |

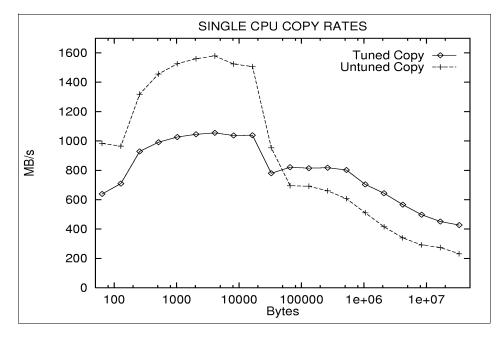

| 13. | Single Processor Copy Rates                                         | 96             |

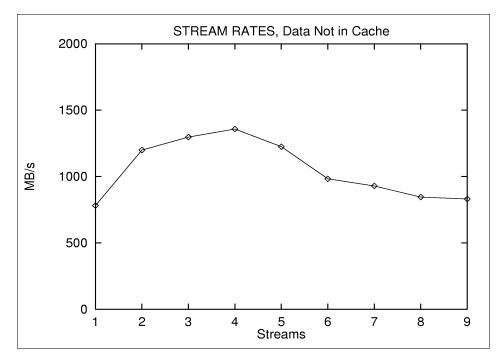

| 14. | Stream Rates for Data Not in Cache                                  | 97             |

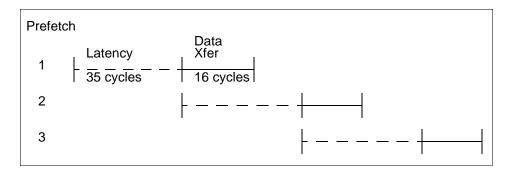

| 15. | Single Stream Prefetch                                              | 98             |

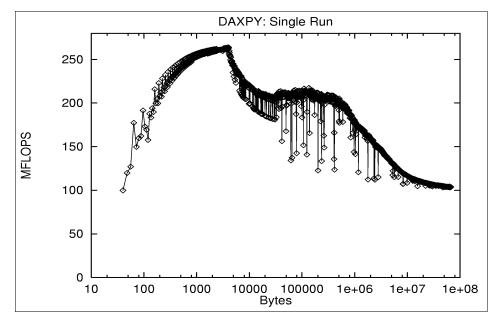

|     | DAXPY: Single Run                                                   |                |

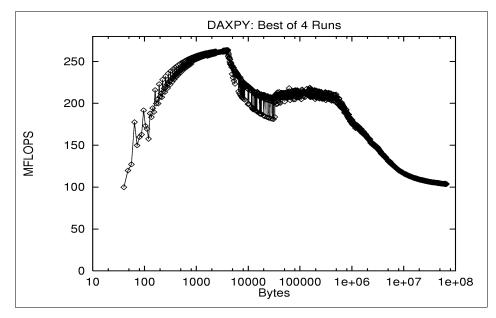

| 17. | DAXPY: Best of 4 Runs (1) 10                                        | )0             |

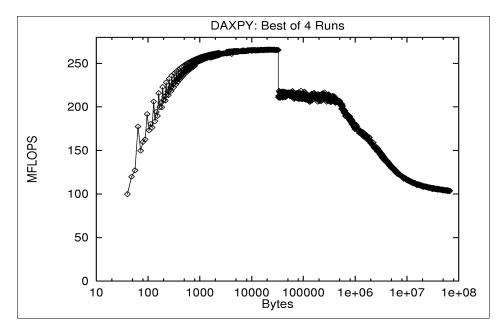

|     | DAXPY: Best of 4 Runs (2) 10                                        |                |

| 19. | Stride versus Loop Count for L1 Cache                               | )4             |

| 20. | Stride versus Loop Count for TLB 10                                 | )5             |

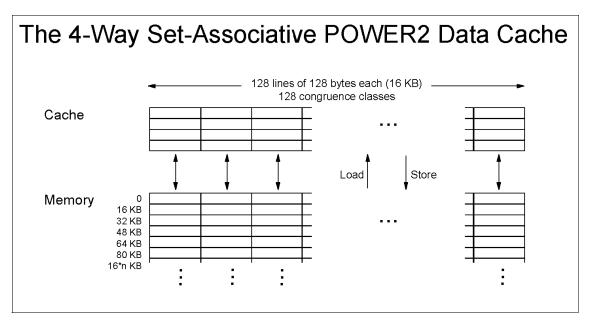

| 21. | The 4-Way Set-Associative POWER2 Data Cache                         | 20             |

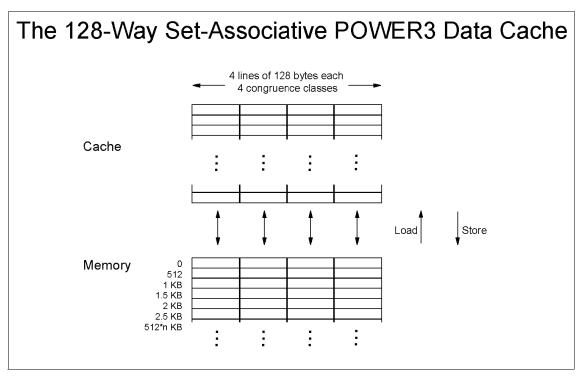

| 22. | The 128-Way Set-Associative POWER3 Data Cache                       | 21             |

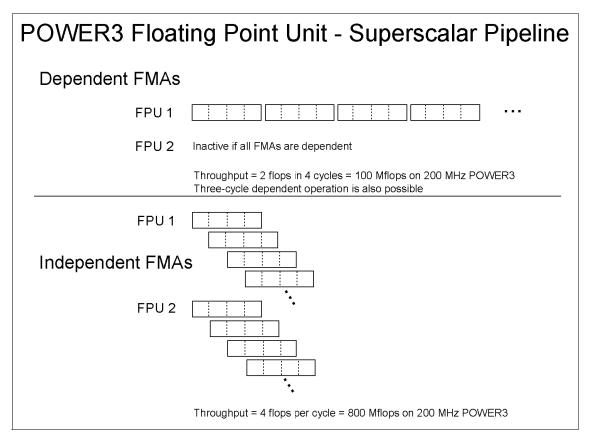

|     | POWER3 Floating Point Unit - Superscalar Pipeline                   |                |

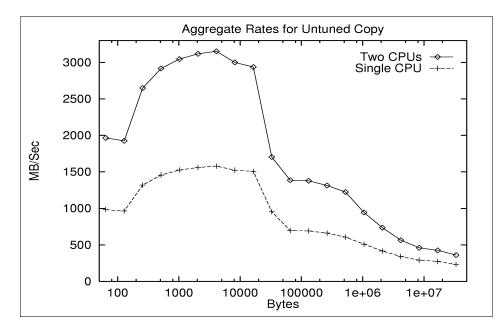

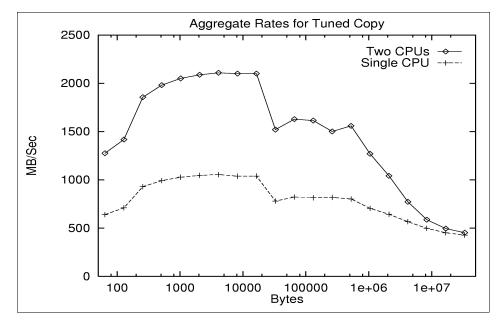

| 24. | Aggregate Rates for Untuned Copy14                                  | 8              |

| 25. | Aggregate Rates for Tuned Copy 14                                   | 8              |

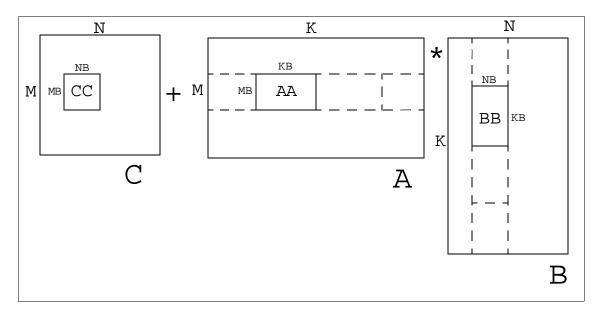

|     | Block Matrix Multiplication                                         |                |

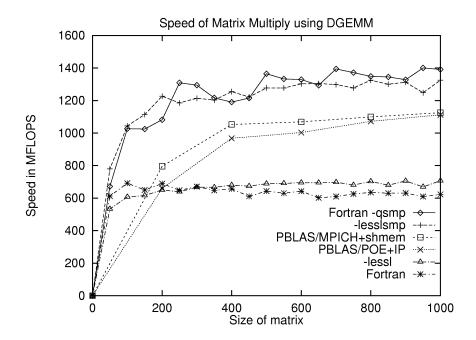

|     | Performance of DGEMM 15                                             |                |

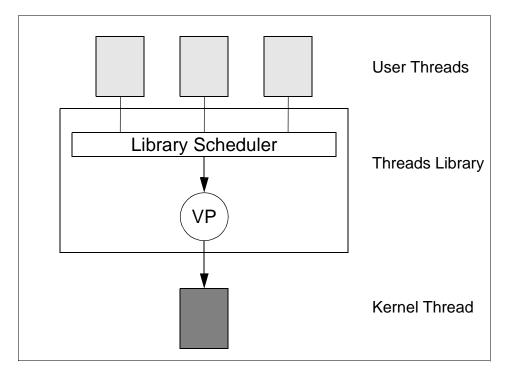

|     | M:1 Threads Model                                                   |                |

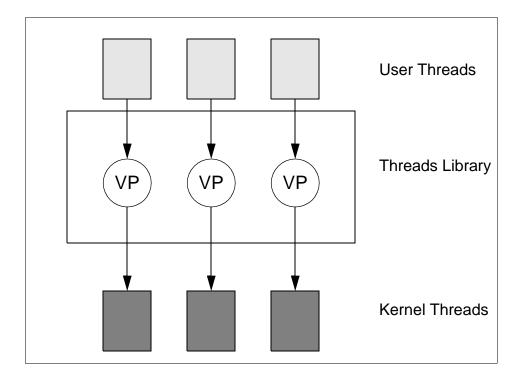

|     | 1:1 Threads Model                                                   |                |

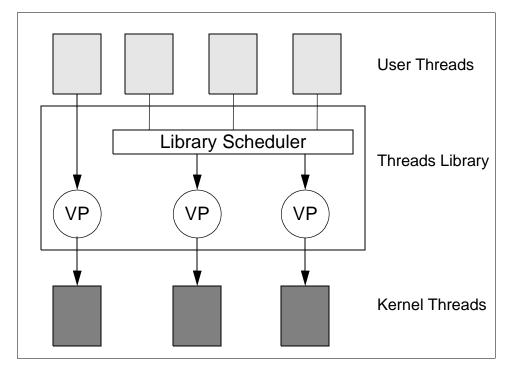

| 30. | M:N Threads Model                                                   | <del>)</del> 1 |

## Tables

| 1.  | Performance of POWER1 versus POWER2 2                                |

|-----|----------------------------------------------------------------------|

| 2.  | POWER3's Low Execution Latencies                                     |

| 3.  | RS/6000 43P 7043 Model 260 Memory Bandwidth                          |

| 4.  | Fortran Storage Classes and AIX Segments                             |

| 5.  | The Benchmark Environment                                            |

| 6.  | CPU Time for Original Programs in Seconds                            |

| 7.  | CPU Time for Tuned Programs in Seconds                               |

| 8.  | Storage Areas and Their Maximum Sizes                                |

| 9.  | Four Different dcopy Approaches70                                    |

| 10. | Three DAXPY Versions:                                                |

|     | Cycles of Some Functions                                             |

| 12. | Complex Exponential Function                                         |

|     | Power Function                                                       |

|     | Advantages and Disadvantages of Msg Passing Techniques               |

|     | Synchronous versus Asynchronous Transfer Times                       |

|     | Data Transfer Rates for L1, L2, and Memory 88                        |

|     | Case Study T1: Performance of Tuned and Untuned Code 131             |

|     | Case Study T2: Performance of Untuned and Tuned Code 134             |

|     | Performance of Case Study T3 139                                     |

| 20. | Performance of Load/Store Bound Loop 140                             |

|     | Summary of Copy Rates 149                                            |

|     | Real User Programs 149                                               |

|     | GAMESS Runs in Seconds 160                                           |

|     | Times for Oil Reservoir Simulator Code                               |

|     | Times for Weather Forecast Code                                      |

|     | FIRE Kernel Benchmark Cases 163                                      |

|     | FIRE Kernel Benchmark Results 163                                    |

|     | FIRE Benchmark Results 164                                           |

|     | RADIOSS Benchmark Test Cases 166                                     |

|     | RADIOSS Benchmark Results 166                                        |

|     | CPU Time for SUBROUTINE JACOBI, (in Seconds) 172                     |

|     | LINPACK Performance                                                  |

|     | SPEC95 Performance                                                   |

|     | Sustained MB/s Memory Bandwidth Measured by STREAM 174               |

| 35. | NAS NPB 1.0 (LU, SP, BT) Single CPU Performance, Time in Seconds 175 |

### Preface

This redbook provides information to help you understand and exploit the new generation of computer systems based on the RS/6000 POWER3 architecture. Specifically, this publication will address the following issues:

- POWER3 features and capabilities

- CPU and memory optimization techniques, especially for Fortran programming

- AIX XL Fortran Version 5.1.1 compiler capabilities and which options to use

- Parallel processing techniques and performance

- · Available libraries and programming interfaces

- Performance examples on commonly used kernels and on several full applications

The anticipated audience for this redbook is as follows:

- · Application developers

- End users who may be involved in making modifications to applications

- · Technical managers responsible for equipment purchase decisions

- Managers responsible for project planning

- · Researchers involved in numerical algorithm development

- End users with an interest in understanding the performance of their applications

While this publication is decidedly technical in nature, the fundamental concepts are presented from a user point of view and numerous examples are provided to reinforce these concepts. Furthermore, this publication is organized such that the information becomes more detailed as one progresses through the chapters. This organization will allow readers to stop, once they have achieved the level of understanding they desire, without having to search through the publication.

To some extent, this book should be regarded as a series of subtopics that can be read alone. Each chapter is relatively complete in itself, referring to other chapters where appropriate.

#### The Team That Wrote This Redbook

This redbook was produced by a team of specialists from around the world working at the International Technical Support Organization, Austin Center.

**Stefan Andersson** is a Staff Engineer/Scientist at IBM Poughkeepsie. He has an MS in mathematics from the University of Heidelberg. He began his work with IBM at the IBM Scientific Center, Heidelberg in 1990. He has been involved in parallel computing on RS/6000 SP since 1992. Currently, he is a member of the technical benchmark team at IBM Poughkeepsie. His areas of expertise include performance tuning for the POWER architecture, distributed memory coding and tuning for the RS/6000 SP, and shared memory coding and tuning on IBM SMPs.

**Ron Bell** is an IBM IT Consultant in the UK. He has an MA in Physics and a DPhil in Nuclear Physics from the University of Oxford. He has 27 years of experience with IBM High Performance Computing. His areas of expertise include the Fortran language, performance tuning for POWER architecture, and MPI parallel coding and tuning for the RS/6000 SP. He has for many years collaborated with HKS Inc. to optimize their ABAQUS product for IBM platforms.

**John Hague** is an IBM IT Consultant in the UK. He obtained a PhD in High Energy Physics at University College, London, and worked in this field at the Rutherford Lab in the UK and the Lawrence Livermore Lab in Berkeley until he joined IBM in 1970. John was assigned to the IBM ITSO in Poughkeepsie in 1985 to provide worldwide technical support for the IBM Vector Facility. Since then, he has worked exclusively in the scientific and technical area, and has considerable expertise in vectorizing, parallelizing, and tuning scientific programs, particularly in the Petroleum and Weather Forecasting areas.

**Holger Holthoff** is an IBM IT Consultant in Germany. He has been involved in parallel computing on RS/6000 SP since he joined the IBM Scientific Center, Heidelberg in 1994. Currently, he is a member of the RS/6000 Technical Support focusing on high-performance computing projects and CAE applications in manufacturing industries. He obtained the Dipl.-Ing. and Dr.-Ing. degree in mechanical engineering from University of Karlsruhe and Braunschweig, respectively. His areas of expertise include performance tuning for the POWER architecture and message passing programming for the RS/6000 SP.

**Peter Mayes** is a Senior IT Specialist in the UK. He has 15 years of experience in the field of high-performance computing. He holds the degrees of MA in Mathematics, MSc in Mathematical Modeling and Numerical

Analysis, and DPhil in Engineering Mathematics, all from the University of Oxford. His areas of expertise include Fortran programming, particularly for high-performance and parallel computers, and administration of RS/6000 SPs.

**Jun Nakano** is an IT Specialist of IBM Japan. From 1990 to 1994, he was with IBM Tokyo Research Laboratory and studied combinatorial optimization. Since 1995, he has been involved in RS/6000 and SP benchmarks. He holds MSc in physics from University of Tokyo. He is interested in algorithms, computer networks, and operating systems.

**Danny Shieh** is a Senior Engineer/Scientist of IBM Austin. He joined the IBM Palo Alto Scientific Center in 1969. From 1974 to 1976, he was assigned to the Large Scale Computing department in IBM San Jose Research. From 1985 to 1986, he was assigned to the IBM International Technical Support Center in Poughkeepsie, NY to support the IBM 3090 Vector Facility. He joined the IBM RS/6000 team in 1992. His current assignment is technical support of S&TC marketing for RS/6000 products. He received the MS and PhD degrees in Atmospheric Sciences in 1967 and 1969, respectively, from New York University.

**Jim Tuccillo** is an atmospheric scientist by training. He has attended Cornell University, Old Dominion University, and Johns Hopkins University. Jim has been involved in the development of Numerical Weather Prediction (NWP) Models on high-performance vector, parallel vector, and distributed memory systems since 1980. Jim has worked in the NWP development labs of the US Weather Service and NASA where he has been involved in the development of research and operational NWP codes for weather forecasting in the US. Jim currently works for IBM's Global Government Industry organization where he is involved in issues associated with NWP and high-performance computing on IBM's SP system. Jim has research interests in the areas of parallel algorithms and parallel programming paradigms for high-performance, numerically intensive computing.

This project was coordinated by:

Scott Vetter IBM Austin

Thanks to the following people for their invaluable contributions to this project:

| Alan Adamson  | IBM Toronto |

|---------------|-------------|

| Yukiya Aoyama | IBM Japan   |

| Arthur Ban    | IBM Austin  |

| Howard Brauer | IBM Austin  |

| Luke Browning    | IBM Austin          |

|------------------|---------------------|

| Frank Johnston   | IBM Poughkeepsie    |

| Matthias Laux    | IBM Heidelberg      |

| Lisa Martin      | IBM Toronto         |

| Joan McComb      | IBM Poughkeepsie    |

| Frank O'Connell  | IBM Austin          |

| Mark Papermaster | IBM Austin          |

| Farid Parpia     | IBM Poughkeepsie    |

| Jim Shearer      | IBM Watson Research |

| David Tuttle     | IBM Austin          |

| Steve White      | IBM Austin          |

|                  |                     |

#### **Comments Welcome**

#### Your comments are important to us!

We want our redbooks to be as helpful as possible. Please send us your comments about this or other redbooks in one of the following ways:

- Fax the evaluation form found in "ITSO Redbook Evaluation" on page 221 to the fax number shown on the form.

- Use the electronic evaluation form found on the Redbooks Web sites:

For Internet users For IBM intranet users http://www.redbooks.ibm.com

http://w3.itso.ibm.com

• Send us a note at the following address:

redbook@us.ibm.com

### **Chapter 1. Introduction**

This publication is designed to familiarize you with the IBM RS/6000 POWER3 architecture and provide you with the information necessary to exploit the new high-end technical workstations based on this architecture.

The two-way symmetric multiprocessing (SMP) workstation RS/6000 43P 7043 Model 260 will be the first POWER3 system to be available. Thus, most analysis presented in this publication refers to this system.

#### 1.1 RS/6000 Processor Evolution

In this section, the stages of processor development are discussed, starting with the POWER1 architecture through to the latest POWER3. Various references for additional reading are included.

#### 1.1.1 POWER1

The first RS/6000 products were announced by IBM in February of 1990, and were based on a multiple chip implementation of the POWER architecture, described in *IBM RISC System/6000 Technology*, SA23-2619. This technology is now commonly referred to as POWER1, in the light of more recent developments. The models introduced included an 8 KB instruction cache (I-cache) and either a 32 KB or 64 KB data cache (D-cache). They had a single floating-point unit capable of issuing one compound floating-point multiply-add (FMA) operation each cycle, with a latency of only two cycles. Therefore, the peak MFLOPS rate was equal to twice the MHz rate. For example, the Model 530 was a desk-side workstation operating at 25 MHz, with a peak performance of 50 MFLOPS. Commonly occurring numerical kernels were able to achieve performance levels very close to this theoretical peak.

In January of 1992, the Model 220 was announced, based on a single chip implementation of the POWER architecture, usually referred to as RISC Single Chip (RSC). It was designed as a low-cost, entry-level desktop workstation, and contained a single 8 KB combined instruction and data cache.

The last POWER1 machine, announced in September of 1993, was the rack-mounted Model 990. It ran at 71.5 MHz and had a 32 KB I-cache and a 256 KB D-cache.

#### 1.1.2 POWER2

Announced in September 1993, the Model 590 was the first RS/6000 based on the POWER2 architecture, described in *PowerPC and POWER2: Technical Aspects of the New IBM RISC System/6000*, SA23-2737. The most significant improvement introduced with the POWER2 architecture for scientific and technical applications is that the floating-point unit (FPU) contains two 64-bit execution units, so that two floating-point multiply-add instructions may be executed each cycle. A second fixed-point execution unit is also provided. In addition, several new hardware instructions were introduced with POWER2:

- Quad-word storage instructions. The quad-word load instruction moves two adjacent double-precision values into two adjacent floating-point registers.

- Hardware square root instruction.

- Floating-point to integer conversion instructions.

Although the Model 590 ran with only a marginally faster clock than the POWER1-based Model 580, the architectural improvements listed above, combined with a larger 256KB D-cache size, enabled it to achieve far greater levels of performance, as shown in Table 1.

|                    | Model 580 | Model 590 |

|--------------------|-----------|-----------|

| Architecture       | POWER1    | POWER2    |

| MHz                | 62.5      | 66        |

| D-cache            | 64KB      | 256KB     |

| Peak MFLOPS        | 125       | 264       |

| LINPACK DP MFLOPS  | 38        | 130       |

| LINPACK % of peak  | 30%       | 49%       |

| LINPACK TPP MFLOPS | 104       | 237       |

Table 1. Performance of POWER1 versus POWER2

In October 1996, IBM announced the RS/6000 Model 595. This was the first machine to be based on the P2SC (POWER2 Super Chip) processor. As its name suggests, this is a single chip implementation of the POWER2 architecture, enabling the clock speed to be increased further. The Model 595 runs at 135MHz, and the fastest P2SC processors, found in the Model 397 workstation and RS/6000 SP Thin4 nodes, run at 160 MHz, with a theoretical peak speed of 640 MFLOPS.

### 1.1.3 PowerPC

The RS/6000 Model 250 workstation, the first to be based on the PowerPC 601 processor running at 66 MHz, was introduced in September, 1993. The 601 was the first processor arising out of the partnership between IBM, Motorola, and Apple. The PowerPC architecture includes most of the POWER instructions. However, some instructions that were executed infrequently in practice were excluded from the architecture, and some new instructions and features were added, such as support for symmetric multiprocessor (SMP) systems. In fact, the 601 did not implement the full PowerPC instruction set, and was a *bridge* from POWER to the full PowerPC architecture implemented in more recent processors, such as the 603, 604, and 604e. Currently, the fastest PowerPC-based machines from IBM for technical purposes, the four-way SMP system RS/6000 7025 Model F50 and the uni-processor system RS/6000 43P 7043 Model 150, use the 604e processor running at 332 MHz and 375 MHz, respectively.

#### 1.1.4 **POWER3**

The new POWER3 processor, described in detail in Chapter 2, "The POWER3 Processor" on page 7, essentially brings together the POWER2 architecture, as currently implemented in the P2SC processor, with the PowerPC architecture. It combines the excellent floating-point performance delivered by P2SC's two floating-point execution units, while being a 64-bit, SMP-enabled processor ultimately capable of running at much higher clock speeds than current P2SC processors.

#### 1.2 SMP-Based System Views

Since the POWER3 architecture provides SMP support, POWER3-based systems will feature multiple CPUs with a uniform access shared memory and shared I/O resources. This section outlines the different ways in which these multiple CPUs can be exploited, either by running multiple job streams to achieve greater overall system throughput, or by using a shared or distributed memory programming model to reduce the time to solve an individual problem.

#### 1.2.1 Job Level Parallelism with Single CPU Jobs

For work loads consisting of many independent jobs each using a single CPU, the multiple CPUs of a POWER3 based system will provide greater throughput performance than a uni-processor system. For example, POWER3 based systems with two CPUs may provide twice the nominal performance on a work load when compared with a comparable

Introduction 3

uni-processor system. Each POWER3 CPU will also provide an improvement in performance over existing CPUs.

#### **1.2.2 Automatic Parallelization (Fortran)**

The XL Fortran compiler (Version 5.1.1 or later) provides support for automatic parallelism of programs to provide increased performance so as to reduce the elapsed time of a program. Essentially, the code is analyzed for independent pieces of work that can be dispatched, in parallel, to the multiple CPUs of a POWER3 based system. This SMP capability is also available on machines using PowerPC processors, such as the Model F50. The ability of the compiler to detect opportunities for parallelism can vary and is dependent on the intrinsic properties of the problem being solved and the source code implementation. The nominal performance improvement over using a single CPU is generally limited to the number of CPUs on the POWER3 based system. Typically, new programs can be written in a manner that allows for a high-level of compiler-detected parallelism. Existing programs can often be modified to allow for significant levels of parallel efficiency. The automatic parallelization capabilities of XL Fortran can often be assisted through the insertion of compiler directives, as discussed in the next section.

#### **1.2.3 Compiler Directives**

Compiler directives are often used in conjunction with the automatic parallelization capability of the XL Fortran compiler to assist in situations where the dependency analyzer is unable to detect independent pieces of work. Compiler directives appear as Fortran comments so that code portability is preserved. OpenMP is an evolving industry standard that will provide for code portability across shared-memory parallel systems.

### 1.2.4 Message Passing Interface

The Message Passing Interface (MPI) is the industry standard for parallel programming on distributed memory systems, such as the IBM RS/6000 Scalable Parallel (SP) system. Programs that have been parallelized using the Message Passing Interface are highly portable between different platforms. In general, MPI programs also perform excellently on SMP systems. MPI is supported on clustered RS/6000 uni-processor machines as well as on SMP systems.

With this paradigm, the programmer has explicitly decomposed the problem to run as separate processes that communicate and synchronize through the MPI library. The separate processes of an MPI program are transparently mapped against the multiple CPUs of a POWER3 based system.

For IBM RS/6000 SP systems, an alternative approach exploiting SMP nodes is to assign a separate MPI process to each CPU of each node. With this approach, MPI message passing will take place at both the intra-node and inter-node level, and threads are not required to address the multiple CPUs of each node.

#### 1.2.5 Using POSIX Threads

The *thread* programming interface is the native interface of parallel programming on SMP systems, but also used for performance improvements on uni-processor systems. On RS/6000, POSIX threads support is provided through both a C and Fortran application program interface (API) and allows for the exploitation of the multiple CPUs of a POWER3 based system. Since POSIX threads is an industry standard, programs written using this library are generally portable to other SMP platforms. At the time of publication, the Fortran binding for pthreads is not part of the POSIX phreads standard, therefore, Fortran pthreads implementations may be AIX specific.

#### 1.2.6 Combined MPI/Threads Paradigm

For IBM RS/6000 SP systems with SMP nodes, a combined MPI and threads programming paradigm is also supported. With this approach, a single MPI processes is assigned to each SMP node, and multiple threads are executed on each node. The threads will be used to execute the computational kernels so as to exploit the multiple CPUs on the node, and MPI communication will take place between the nodes. Threads can be either explicitly created through the POSIX Threads library or can be implicitly created with the automatic parallelism features of the XL Fortran compiler (with or without compiler directives), as discussed in 1.2.2, "Automatic Parallelization (Fortran)" on page 4.

Introduction 5

### Chapter 2. The POWER3 Processor

The POWER3 microprocessor introduces a new generation of 64-bit processors especially designed for high performance and visual computing applications. POWER3 processors are the replacement for the POWER2 and POWER2 Super Chips (P2SC) in high-end RS/6000 workstations and technical servers.

#### 2.1 Processor Overview

The POWER3 implementation of the PowerPC architecture provides significant enhancements compared to the POWER2 architecture. The SMP-capable POWER3 design allows for concurrent operation of fixed-point instructions, load/store instructions, branch instructions, and floating-point instructions. The POWER3 is designed for ultimate frequencies of up to 600 MHz when fabricated with advanced semiconductor technologies such as copper metallurgy and silicon-on-insulator (SOI). In contrast, the P2SC design has reached its peak operating frequency at 160MHz. The first POWER3 based system, RS/6000 43P 7043 Model 260, runs at 200 MHz.

Capable of executing up to four floating-point operations per cycle (two multiply-add instructions), the POWER3 maintains the emphasis on floating-point performance and memory bandwidth that has become the hallmark of POWER2 based RS/6000 systems. Integer performance has been significantly enhanced over the P2SC with the addition of dedicated integer and load/store execution units, thus improving its SPECint95 performance relative to the 160 MHz P2SC by about 50 percent at 200 MHz. This gives the POWER3 far more balanced performance, which is especially notable in graphics intensive applications.

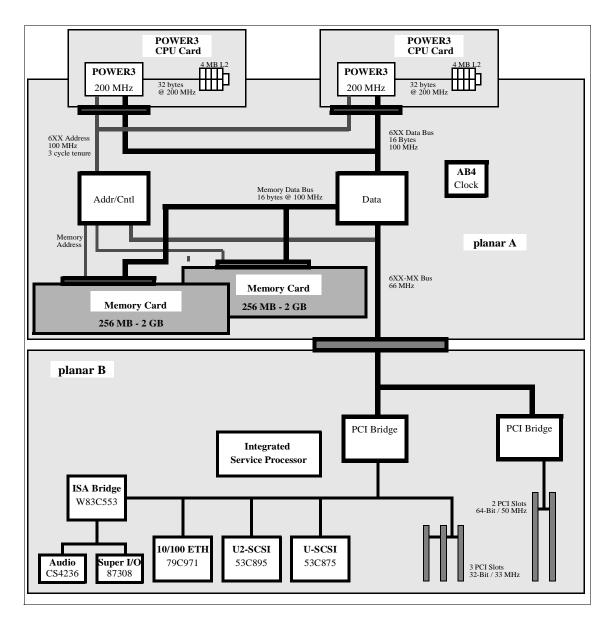

The POWER3 is a 64-bit PowerPC implementation with a 32-byte backside L2 cache interface (private L2 cache bus), and a 16-byte PowerPC 6XX bus, as shown in Figure 1. The POWER3 has a peak execution rate of eight instructions per cycle (compared to six for the P2SC) and a sustained performance of four instructions per cycle.

Significant investments in the chip's data flow, instruction routing, and operand buffering have been made in order to sustain a high computational and corresponding data rate. The POWER3's level-one (L1) data cache is an efficient interleaved cache capable of two loads, one store, and one cache line reload per cycle. Although half the size of the P2SC's cache, the L1 is effectively supplemented by a dedicated second level (L2) cache, which may be from 1 MB to 16 MB in size. Data and instruction prefetching mechanisms

improve the memory access performance by hiding memory latency. Also, the large 128 byte line size takes advantage of the locality of reference (spacial reuse) characteristic of large engineering and scientific data reference patterns

Figure 1. POWER3 Processing Units (Model 260)

#### 2.2 POWER3 Execution Core

Unlike some competitive chips, which need several pipeline stages before instructions enter the first execution stage, POWER3 keeps this front end of the pipeline short, using only three stages. POWER3 needs only one cycle to access the instruction cache, one cycle to decode and dispatch the instructions to different execution units, and one more cycle to access the operands. POWER3's relatively short pipeline keeps its mispredicted branch penalty to only three cycles, up to 24 cycles shorter than its competitors.

Up to eight instructions (two floating-point, two load/store, two single-cycle integer, a multi-cycle integer, and a branch) can be in execution in each cycle. Ready instructions are issued out of order from the issue queues, allowing instructions of different types, as well as of the same type, to execute out of order. The load/store and branch instructions are issued in program order.

For branch instructions whose conditions are not known in the decode stage, POWER3 uses a 2,048-entry branch history table (BHT) to predict the branch direction. Because a branch is often resolved in the decode stage or soon thereafter, the benefit of the BHT when used to predict the current encounter of the branch is less in POWER3 than in designs with deeper pipelines. To better use the BHT, however, POWER3 uses the BHT to predict both the current and the next encounter of each conditional branch, using a branch target address cache (BTAC).

POWER3 uses rename registers for the general-purpose registers (GPR), floating-point registers (FPR), and the condition-code register (CCR) to allow out-of-order and speculative execution of most instructions. The few exceptions are stores and certain move-to-special-register instructions that are difficult to undo. Although instructions can be issued out-of-order, and thus, their operands can be read out-of-order from the registers, the rename registers eliminate anti- and output-dependencies by enabling the registers to be updated in program order.

POWER3 has two identical FPUs, each delivering up to two floating-point operations per cycle. POWER3's FPUs execute multiply-add instructions, as Table 2 shows, taking only one cycle throughput to calculate the frequently used (a\*b+c) operation.

| Instruction        | Number of Cycles |        |  |

|--------------------|------------------|--------|--|

|                    | 32 bit           | 64 bit |  |

| Integer Multiply   | 3-4              | 3-9    |  |

| Integer Divide     | 21               | 37     |  |

| FP Multiply or Add | 3-4              | 3-4    |  |

| FP Multiply-Add    | 3-4              | 3-4    |  |

| FP Divide          | 14-21            | 18-25  |  |

| FP Square Root     | 14-23            | 22-31  |  |

Table 2. POWER3's Low Execution Latencies

The non-blocking caches support four outstanding L1 data demand requests and two outstanding L1 instruction demand requests in order to reduce the memory subsystem latency. The L1 cache also supports hits under misses, the L1 cache allows a fifth demand request which hits the cache to proceed even when there are four previous outstanding misses to the data cache. In

The POWER3 Processor 9

comparison, the POWER2 architecture allows only one outstanding cache miss without blocking. Cache hits are satisfied within a single cycle. The writeback data cache implements a four-state *MESI* cache coherence protocol (possible states: modified, exclusive, shared, and invalid) to support SMP environments.

POWER3 uses instruction- and data-prefetch mechanisms to reduce pipeline stalls due to cache misses. The instruction cache is two-way interleaved on cache-line boundaries, allowing one bank to be accessed for instruction fetches while the other bank is accessed for the next cache line. When the former access hits in the cache but the latter access does not, a prefetch request for this next cache line is issued to the L2 cache. Because the prefetch is still speculative, the request is not propagated to the main memory. If it misses in the L2 cache, this allows the request to be canceled upon detecting a mispredicted branch instruction. An instruction prefetch takes six cycles from the 200 MHz L2 cache.

For the data cache, the Model 260 can prefetch up to four streams of data from memory or L2 cache into L1 cache. To establish a prefetch stream, the prefetch mechanism monitors every access that misses in the data cache, searching for cache-miss references to two adjacent cache lines. For this purpose, a stream address filter queue of depth 10 is used, which contains the guessed next stream addresses. The filter is maintained by a least recently used (LRU) mechanism in order to age out seldom used prefetch streams. Upon finding such a pair of succeeding cache misses, it initiates a prefetch request for the next cache line. The stream addresses, along with the ascending or descending prefetch direction, is kept in a four-entry stream address buffer. Once a prefetch stream is identified, the address of every data-cache access is checked with the addresses in the stream address buffer. When a match is found, a prefetch request for the next cache line is made, and the address in the matching entry is updated with the address of the new prefetch request. A simplified view on the prefetch hardware is given in Figure 2.

When initially predicting the direction of a prefetch stream, it is assumed that if the word that causes the cache-miss occurs in the bottom half of the cache line, the next higher line will be required, but if the miss occurs in the top half, then the next lower line will be required. Then data is being prefetched in sequentially in either a forwards or backwards direction. If the initial prediction is wrong, the direction is corrected for the subsequent stream.

Figure 2. Data Prefetch Overview

The 64-bit address space is managed by using 80-bit virtual addresses and 40-bit real memory addresses, which support up to 1 terabyte. A 256-entry two-way set associative translation lookaside buffer (TLB) based on a least recently used replacement algorithm is used to access 4 KB memory pages.

The performance of many technical applications is mainly determined by the performance of the memory subsystem. POWER3 systems are designed to deliver industry leading memory bandwidth, which has already been a strength of the POWER2 architecture. The bandwidth, as listed in Table 3, in terms of GB/s depends on the actual clock frequency. As an example the DAXPY operation,  $y(i)=y(i)+a^*x(i)$ , yields a sustained memory bandwidth of 1.3 GB/s, close to the peak bandwidth of 1.6 GB/s of a POWER3 Model 260 system. DAXPY performance is analyzed in more detail in Chapter 7.3.3, "DAXPY" on page 98.

The load latency, due to either a data or instruction L1 miss that hits the L2 cache, amounts nine CPU cycles. A data access that misses the L1 and L2

The POWER3 Processor 11

cache causes a latency of about 35 cycles on a Model 260. However, this does not depend on the processor only, but also on the system.

| Access                       | Interface<br>Width<br>[Bit] | Clock<br>Frequency<br>[MHz] | Bandwidth<br>[Byte/cycle] | Bandwidth<br>[GB/s] |

|------------------------------|-----------------------------|-----------------------------|---------------------------|---------------------|

| Load Register from L1        | 128                         | 200                         | 2*8                       | 3.2                 |

| Store Register to L1         | 64                          | 200                         | 8                         | 1.6                 |

| Load/Store L1 from/to L2     | 256                         | 200                         | 4*8                       | 6.4                 |

| Load/Store L1 from/to Memory | 128                         | 100                         | 2*8                       | 1.6                 |

Table 3. RS/6000 43P 7043 Model 260 Memory Bandwidth

#### 2.3 POWER3 Roadmap

The first generation of POWER3 based systems will operate at CPU speeds of 200 MHz and memory bus speeds of 100 MHz. The processor board will hold a direct mapped L2 cache of 4 MB per processor. The initial chip design does not support fractional processor-to-cache and processor-to-system clock ratios (such as 3:2 mode). But the second generation of POWER3 chips will remove this limitation. This will be the first design based on IBM's advanced CMOS-7S process. With help of this 0.2-micron process, which uses copper interconnects, clock speeds of more than 300 MHz will be achievable. The die size will shrink from 270 mm<sup>2</sup> to 160 mm<sup>2</sup>, with a few additional functions.

IBM plans a second derivative of POWER3 chips in a 0.18-micron process, targeting speeds up to 500-600 MHz. This process may showcase IBM's unique Silicon-on-Insulator (SOI) technology. SOI protects the millions transistors on a chip with a *blanket* of insulation, reducing harmful electrical effects that consume energy and hinder performance. A floating-point and integer performance of SPECfp95 70+ and SPECint95 30+, respectively, is expected.

The faster POWER3 chips will support fractional bus modes (such as 5:2 and 7:2 for processor-to-bus and 3:2 for processor-to-cache interfaces) which will allow the core to run at its full speed. Using a set-prediction mechanism, the new chips will also support a four-way set-associative L2 cache.

Figure 3 on page 13 shows the high-level partition of logical units within the POWER3 chip.

Figure 3. POWER3 Chip Layout: 270 mm<sup>2</sup> Die, 15 Million Transistors

#### 2.4 POWER3-Based Systems

The POWER3 CPU will be featured in several different computer systems. There will be stand-alone workstations up through IBM RS/6000 SP nodes.

#### 2.4.1 RS/6000 43P 7043 Model 260

The Model 260 is a desk-side RS/6000 system designed to perform as a high-performance technical workstation, visual client, or workgroup server. The mechanical package can accommodate up to two processor cards, two memory cards, and five PCI adapters. It also supports two hot-swap DASD bays (Ultra SCSI), two 5 1/4" media bays, and one floppy drive.

Each processor card carries one POWER3 chip running at 200 MHz.

The memory controller function is located on the planar. A system planar is shown in Figure 4 on page 14. The memory chipset supports a 128-bit data path to memory running at 100 MHz, giving the system a peak memory

The POWER3 Processor 13

bandwidth of 1.6 GB/s. The two processor cards have to share this bandwidth. The chipset is not only an interface to the memory but also to the 6XX-MZ mezzanine bus used for the I/O.

Figure 4. Logical View of the Model 260

Each memory card can carry between 256 MB and 2 GB of memory using 128 MB dual inline memory modules (DIMMs), giving the system a maximum total memory of 4GB. These sizes will double when 256 MB DIMMs become available.

#### 2.4.2 IBM RS/6000 SP Nodes

In the future, there will be several nodes for the IBM RS/6000 SP available. The first one will be based on the RS/6000 43P 7043 Model 260. The differences between these node and the Model 260 are the form factor in order to fit into the IBM RS/6000 SP frame and the ability to connect it to the high performance switch. In order to fulfill the Accelerated Strategic Computing Initiative (ASCI) contract, IBM will also offer an eight- and later a 16-way SMP based on the POWER3 processor. These models are expected to contain several unique features and new design points.

#### 2.4.3 DOE ASCI Project

On July 26, 1996, Lawrence Livermore National Laboratory (LLNL) announced it had selected IBM for an award of a \$93 million contract to build the world's fastest supercomputer as part of the Department of Energy's (DOE) Accelerated Strategic Computing Initiative (ASCI) program, called ASCI Blue Pacific. The final configuration of the proposed system will consist of:

- 512 eight way POWER3 SMP nodes

- More than three teraflops peak performance

- 2500 GB total system memory

- 75 terabytes global disk capacity

- 6400 MB/s I/O bandwidth

In order to meet the increased need for computing power, the next step after ASCI Blue Pacific, called ASCI White, is already announced. The ASCI White System will consist of 8192 POWER3+ CPUs capable of peak speed of 10 trillion operations per second.

Both the ASCI Blue Pacific and the ASCI White project will drive the future RS/6000 and IBM RS/6000 SP system development in hardware as well as software. The result of this work will provide future gains through improved products for IBM Customers.

For more information about the ASCI project, visit the following Web pages:

| http://www.doe.org        |

|---------------------------|

| http://www.llnl.gov/asci/ |

The POWER3 Processor 15

## Chapter 3. XL Fortran Version 5

XL Fortran Version 5 is the first XL Fortran compiler that has the ability to exploit SMP processors concurrently for improving the performance. It is also the first to produce object code that runs in 64-bit mode on AIX 4.3 or later. This chapter mainly describes differences between XL Fortran Version 5.1 and previous versions that users should be aware of for compiling and running programs on POWER3 hardware.

#### 3.1 SMP Support

One of the most outstanding features of XL Fortran Version 5 is its support for SMP. The compiler automatically identifies DO loops that can be parallelized and makes object code that runs in a multi-threaded fashion. Or, you can give directives to the compiler in order to provide additional information on the code or to force the compiler to parallelize certain DO loops. Detailed explanations and examples will be given in Chapter 4, "Using the SMP Feature of XL Fortran" on page 29. An overview of compiler architecture is presented here. (See D. Kulkarni et al., "XL Fortran Compiler for IBM SMP Systems," *AIXpert Magazine*, December 1997.)

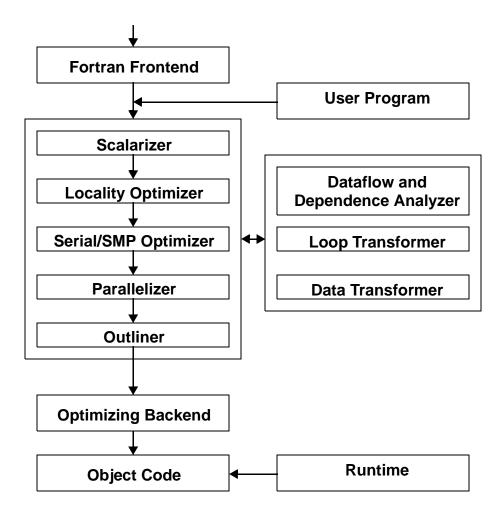

Figure 5 on page 18 shows the path through the XL Fortran compiler when the parallelization facility is activated with the -qsmp option. The Fortran front end takes your program as input, checks the program syntactically and semantically, and produces an intermediate representation of it. The scalarizer transforms the Fortran 90 array language constructs into scalar DO loops.

The subsequent locality optimizer and serial and SMP optimizer perform optimizations, including loop reordering, array padding, loop tiling, loop unrolling, elimination of conditionals, and so on. If given the target architecture by the -qarch option, the compiler takes into account hardware specifics, such as cache size and cache line size. The parallelizer uses loop reordering transformations to automatically parallelize loops at outermost levels, which minimizes parallelization overheads, such as barrier synchronization at the end of parallel loops, and ensures larger computation granularity on each of the processors of the SMP system. The outliner does the converse of subroutine inlining. It converts DO loops, which are decided to be parallelized, into subroutines.

You can see how a program is outlined by reading the outlining report section of hotlist, which is generated by the -qreport=hotlist compiler option. An example of hotlist is given in 4.1, "How to Compile, Link, and Execute" on

page 29. By invocation of xlf\_r or xlf90\_r, the object code is linked with thread-safe libraries for parallel execution.

Figure 5. XL Fortran Version 5 Compiler Architecture

In addition to automatic parallelization, XL Fortran Version 5 provides the pthreads library module (f\_pthread) as an interface to the AIX pthreads library. See *XL Fortran for AIX Language Reference Version 5 Release 1*, SC09-2607 or "XL Fortran Compiler for IBM SMP Systems," *AIXpert Magazine*, December 1997 for details.

# 3.2 Support for POWER3

The XL Fortran compiler has a -qarch option that tries to produce efficient object code that may contain machine instructions specific to the target architecture. The default value is -qarch=com, which means the executable can be run on any hardware platform of POWER and PowerPC, but in order to fully use the hardware's capability, it is recommended to use the appropriate -qarch option, especially for scientific and technical applications. In addition to architectures supported by XL Fortran Version 4.1 (that is, com, pwr, pwr2, ppc, and so forth), XLF Version 5.1 introduces two new architectures: pwr3 (V5.1.1) and rs64a (V5.1.0). Currently, RS/6000 Model 260 (and its corresponding SP nodes) and RS/6000 S70 (S7A) conform to pwr3 and rs64a, respectively.

Since XL Fortran does not optimize the program by default, you should specify appropriate options when compiling. To begin with, it is recommended to use the following combination of compiler options for POWER3 machines:

\$ xlf -qarch=pwr3 -03 -qtune=pwr3 yourprogram.f

The -O3 option instructs the compiler to do the highest level optimization. This optimization level has the potential to rearrange the semantics of the programs. Although it produces a mathematical equivalent result, it may not produce a bitwise identical result with the unoptimized code. If this is a concern, you can add the -qstrict option to ensure that you get the bitwise identical results with the unoptimized code. The -qarch and -qtune options both perform architecture-dependent optimization for the POWER3. Further tuning of compiler options should be carried out with these options as a starting point. More detailed discussions on compiler options are given in 8.2, "Recommended Compiler Options" on page 112.

#### 3.3 64-Bit Support

In order to be able to exploit the huge address space offered by 64-bit addressing, Fortran programmers need to understand how memory is handled by the AIX and the XL Fortran compiler, both in 32-bit and 64-bit mode. This section gives both the background and some practical implications of 32-bit and 64-bit addressing.

In AIX, virtual memory is divided into segments. In 32-bit mode, a 32-bit address is divided into a 28-bit field, which gives the offset within a 256 MB  $(2^{28}$  bytes) segment, and a 4-bit field, which selects between 16 segments. In 64-bit mode, 28 bits are again used to address offsets within a 256 MB

XL Fortran Version 5 19

segment, but the number of segments which may be addressed is vastly increased.

# 3.3.1 Fortran Storage Classes

Before explaining how segments are used, it is necessary to understand Fortran storage classes. Each variable belongs to one of the following storage classes:

| Automatic                   | For variables not retained once the procedure ends       |

|-----------------------------|----------------------------------------------------------|

| Static                      | For variables which retain memory throughout the program |

| Common                      | For common block variables                               |

| <b>Controlled Automatic</b> | For automatic arrays                                     |

| Controlled                  | For allocatable arrays                                   |

From the point of view of the operating system, these classes are categorized as one of the following types:

data Initialized static and common variables

bss Uninitialized static and common variables

heap Controlled (or, allocatable) arrays

stack Controlled automatic arrays and automatic variables

The size of these types, where the size is known before execution begins, may be determined by running the size command against the executable as follows:

```

$ size -f a.out

a.out: 1132(.text) + 216(.data) + 134217744(.bss) + 452(.loader) +

12(.except) = 134219556 (32-bit executable)

$ size -X 64 -f a.out

a.out: 1112(.text) + 272(.data) + 134217760(.bss) + 559(.loader) +

20(.except) = 134219723 (64-bit executable)

```

Note that initialized static and common variables and arrays are stored in the data area of the executable file itself; so very large initialized arrays can lead

to very large executable files. These Fortran storage classes and types are mapped onto AIX segments, as listed in Table 4.

| Fortran Storage<br>Class | Туре        | AIX segment<br>(32-bit) | AIX segment<br>(32-bit, with<br>-bmaxdata) | AIX segment<br>(64-bit)                   |

|--------------------------|-------------|-------------------------|--------------------------------------------|-------------------------------------------|

| Static                   | Data or BSS | seg. 2                  | segs. 3-10                                 | segs. 0x10                                |

| Common                   |             | (256 MB)                | (2 GB)                                     | -0x6FFFFFF<br>(4.5 x 10 <sup>5</sup> TB)  |

| Controlled               | Неар        |                         |                                            |                                           |

| Automatic                | Stack       | seg. 2                  | seg. 2                                     | segs. 0xF0000000                          |

| Controlled<br>Automatic  |             | (256 MB)                | (256 MB)                                   | -0xffffffff<br>(6.5 x 10 <sup>4</sup> TB) |

Table 4. Fortran Storage Classes and AIX Segments

Data, bss, and heap are generically termed *user data* and the permissible maximum size of user data is governed by the "data" process limit. Stack is governed by the "stack" process limit. Process limits can be set on a per-user basis in the file /etc/security/limits. Both hard and soft limits may be set in this file. You may then use the ulimit command to raise or lower the soft limit up to the hard limit, or to lower (but not raise) the hard limit.

# 3.3.2 32-Bit Mode

The default mode is the 32-bit mode. As seen from Table 4, all storage classes are allocated to segment 2, a single 256 MB segment. By default in AIX 4.3, the soft limit for user data is 128 MB and for stack is 64 MB. The hard limits are usually set to unlimited by the root user. The linker flags -bmaxdata and -bmaxstack may be used to increase the permissible data and stack sizes beyond the soft limits up to the hard limits, without setting the shell's process limits using ulimit. Note, however, that use of the -bmaxdata flag selects the "Large Address Space Model", described in 3.3.3, "32-Bit Mode, Large Address Space Model" on page 22. If a process exceeds its data limit, it will fail to load if the size of data is known from the object file, or an ALLOCATE statement will fail if the heap grows too large. If the stack limit of a program is exceeded at run time, it will fail with a "Segmentation fault" error message.

XL Fortran Version 5 21

#### – Take Note

Care should be taken when increasing the size of data and/or stack. The user data comes from the lower address area of segment 2, whereas the user stack area is allocated from the top of the segment. There are no checks made to ensure that the user stack area doesn't overlap with the user data area. If the stack overwrites the data area, it is possible either for the program to end abnormally, or worse, for the program to fail silently and produce incorrect results.

# 3.3.3 32-Bit Mode, Large Address Space Model

If the program is linked with the flag -bmaxdata:N, then N bytes are allowed for the user data area, and the user data area is moved from segment 2 to segments 3 through 10, allowing a total of eight segments, or 2 GB, of user data. For example, to allow up to 512 MB, or two segments, of user data, link with the flag -bmaxdata:0x20000000. Note that even if N is less than 256 MB, the user data area resides above segment 2.

As shown in Table 4 on page 21, the user stack area still resides in segment 2. In other words, in either 32-bit mode, the size of the stack (automatic variables and Fortran 90 automatic arrays) is limited to a little less than 256 MB.

Even if a program is linked to use the Large Address Space Model, it is still limited by its stack process limits and its hard data process limit, as explained above.

#### 3.3.4 64-Bit Mode

XL Fortran introduced a new compiler option, -q64, in Version 5.1, which allows the object code to run in 64-bit mode. As seen from Table 4 on page 21, the permissible sizes of stack and user data are huge, although they are still limited by the process limits discussed above. And as with 32-bit mode, -bmaxstack and -bmaxdata may be used to go beyond the soft limits, up to the hard limits, without setting the shell's limits with the ulimit command. However, in this case the -bmaxdata flag does not change the addressing model.

# 3.3.5 Compiler Defaults and Limits

Although the potential size of stack and user data is effectively limited only by the physical memory and paging space installed, there are some other implications of using the -q64 option and 64-bit mode:

- The default size of an integer POINTER (often called Cray pointers or Sun pointers to distinguish them from standard Fortran 90 pointers) is 8 bytes in 64-bit mode.

- The maximum array size increases to approximately 2<sup>40</sup> bytes.

- The maximum dimension bound range is extended to  $[-2^{63}, 2^{63}-1]$ .

- The maximum array size for array constants has not been extended and will remain the same as the maximum in 32-bit mode. The limit depends on the space used by the compiler for a particular program.

- Arrays with a size greater than 2<sup>31</sup>-1 cannot be initialized.

- The maximum iteration count for array constructor implied DO loops increases to 2<sup>63</sup>-1.

- The maximum character variable length extends to approximately 2<sup>40</sup> bytes.

- The maximum length of character literals remains the same as in 32-bit mode. This is limited by the maximum length of a single (possibly continued) Fortran statement, currently 6700 characters.

- The LOC intrinsic function returns an INTEGER(8) value.

#### Important

The default INTEGER and the default REAL size remains 4 bytes in 64-bit mode.

The -q64 option can be combined with -qhot, -O4, -qsmp, and -qipa options in version 5.1.1. Currently, settings for the -qarch option that are compatible with the -q64 option are, -qarch=auto (if compiling on a 64-bit system), -qarch=com, -qarch=ppc, -qarch=rs64a, and -qarch=pwr3. Note that you cannot mix 32-bit and 64-bit object files to create an executable.

# 3.3.6 64-bit Integer Arithmetic Support

In order to use the POWER3's native 64-bit integer computation, you need to compile the program with the -q64 option, and define integers explicitly in the program as INTEGER\*8 or use the -qintsize=8 compiler option to make the

XL Fortran Version 5 23

default size of INTEGER to 8 bytes. Integer constants can have INTEGER\*8 attribute by adding a suffix \_8 as in 123456\_8.

Important

In 64-bit mode, use INTEGER\*8 loop variables for better performance.

# 3.4 Performance Improvements over Previous XL Fortran

This section presents results of a benchmark for a customer, and it shows the improved performance of XL Fortran Version 5.1 and the relative performance of the P2SC chip (160 MHz) and the POWER3 chip (200 MHz). The benchmark was done for the following 14 programs:

| cfd     | Computational fluid dynamics                                         |

|---------|----------------------------------------------------------------------|

| finite  | Finite element method structure analysis iterative eigenvalue solver |

| modyn   | Molecular dynamics                                                   |

| ns3d    | 3-D computational fluid dynamics                                     |

| pureg   | Monte Carlo simulation of gauge theories QCD                         |

| bem3d   | 3-D transient enclosure flow                                         |

| crystal | Computational physics software package                               |

| jcg3d   | 3-D solid structure FEM by J-CG solver static, Yale format           |

| chamber | Time-dependent 3-D computational fluid dynamics                      |

| deft    | Molecular dynamics                                                   |

| enzlong | Life science chemistry                                               |

| cirta   | Computational fluid dynamics                                         |

| mopac93 | Computational chemistry software package (IBM)                       |

| gamess  | Computational chemistry software package                             |

The programs were run *serial* and, for each program, the sum of user CPU time and system CPU time for the original version and the tuned version was

reported. The RS/6000 systems and the software used for the benchmark are listed in Table 5.

Table 5. The Benchmark Environment

|                 | P2SC/XLF3       | P2SC/XLF5       | POWER3/XLF5     |

|-----------------|-----------------|-----------------|-----------------|

| CPU Clock       | 160 MHz         | 160 MHz         | 200 MHz         |

| Memory          | 1 GB            | 1 GB            | 2 GB            |

| AIX             | 4.3             | 4.3             | 4.3             |

| XL Fortran      | 3.2.4           | 5.1.1           | 5.1.1           |

| Compiler option | -qarch=pwr2 -O3 | -qarch=pwr2 -O3 | -qarch=pwr3 -O3 |

The programs were linked with ESSL (for three tuned codes) and the MASS library. For execution on POWER3, a POWER3-enabled ESSL was used. The Fortran preprocessors used were VAST and KAP, which were both 1995 released versions.

Table 6 shows the results of original programs.

Table 6. CPU Time for Original Programs in Seconds

|         | P2SC/<br>XLF3 (A) | P2SC/<br>XLF5 (B) | POWER3/<br>XLF5 (C) | Ratio<br>(A)/(B) | Ratio<br>(B)/(C) | Prepro-<br>cessor |

|---------|-------------------|-------------------|---------------------|------------------|------------------|-------------------|

| cfd     | 125.5             | 115.3             | 101.1               | 1.09             | 1.14             | vast              |

| finite  | 296.5             | 289.4             | 184.0               | 1.02             | 1.57             |                   |

| modyn   | 744.4             | 640.5             | 593.0               | 1.16             | 1.08             |                   |

| ns3d    | 236.0             | 237.5             | 194.4               | 0.99             | 1.22             | kap               |

| pureg   | 666.2<br>676.8    | 697.0<br>659.3    | 532.7<br>505.3      | 0.96<br>1.03     | 1.31<br>1.30     | kap               |

| bem3d   | 372.7             | 347.9             | 284.4               | 1.07             | 1.22             | vast              |

| crystal | 7901.1            | 7621.0            | 6177.8              | 1.04             | 1.23             |                   |

| jcg3d   | 156.0             | 155.0             | 166.5               | 1.01             | 0.93             |                   |

| chamber | 28.1              | 24.5              | 18.7                | 1.15             | 1.31             |                   |

| deft    | 9.5               | 8.4               | 7.6                 | 1.13             | 1.11             |                   |

| enzlong | 80.1              | 67.6              | 65.2                | 1.18             | 1.04             | vast              |

| cirta   | 74.9              | 73.2              | 53.2                | 1.02             | 1.38             | kap               |

XL Fortran Version 5 25

|         | P2SC/<br>XLF3 (A) | P2SC/<br>XLF5 (B) | POWER3/<br>XLF5 (C) | Ratio<br>(A)/(B) | Ratio<br>(B)/(C) | Prepro-<br>cessor |

|---------|-------------------|-------------------|---------------------|------------------|------------------|-------------------|

| mopac93 | 4899.6            | 3840.2            | 3824.5              | 1.28             | 1.00             |                   |

| gamess  | 317.0             | 352.2             | 218.7               | 0.90             | 1.61             |                   |

| Average |                   |                   |                     | 1.07             | 1.23             |                   |

XL Fortran Version 5.1.1 shows a marked improvement in optimizing these programs on the average of seven percent over Version 3.2.5, and because of this improvement of the compiler, the Fortran preprocessors seem less effective. Only jcg3d became slower on POWER3 than P2SC, whose key kernel is sparse matrix-vector multiplication. The new cache organization and size of POWER3 was not able to hold the indirect addressing vector in cache. However, in general, the load/store units of POWER3 greatly enhanced kernels in these benchmark programs, and when comparing P2SC/XLF5 and POWER3/XLF5, POWER3 was faster by 23 percent on average. It was also observed that the majority of these programs gained performance improvement by using the MASS library.

Table 7 shows the results of tuned programs.

|         | P2SC/<br>XLF3 (A) | P2SC/<br>XLF5 (B) | POWER3/<br>XLF5 (C) | Ratio<br>(A)/(B) | Ratio<br>(B)/(C) | Note             |

|---------|-------------------|-------------------|---------------------|------------------|------------------|------------------|

| cfd     | 69.6              | 67.3              | 64.3                | 1.03             | 1.05             |                  |

| finite  | 114.0             | 111.6             | 107.6               | 1.02             | 1.04             |                  |

| modyn   | 66.3              | 71.5              | 59.4                | 0.93             | 1.20             |                  |

| ns3d    | 164.2             | 157.4             | 131.3               | 1.04             | 1.20             |                  |